电容作为基础电子元器件,在放大电路、谐振电路、高频电路等多种电路有所应用,是工程师及小白需要重点关注及使用的电子元件,但很多小白都不知道电容在高频电路的应用及设计方法,所以本文将重点分享电容在高频电路的应用及设计技巧。

1、电容在高频电路的应用

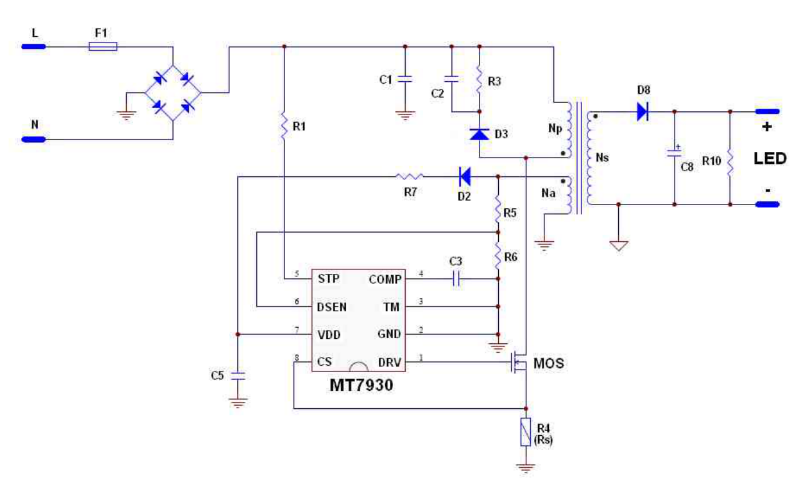

从理论上讲,电容的容量越大,容抗就越小,滤波效果就越好。一些人也有这种习惯认识。但是,容量大的电容一般寄生电感也大,自谐振频率低(如典型的陶瓷电容,0.1uF的fo=5MHz,0.01ulF的fo=15MHz,0.001uF的fO=50MHz),对高频噪声的去耦效果差,甚至根本起不到去耦作用。分立元件的滤波器在频率超过10MHz时,将开始失去性能。元件的物理尺寸越大,转折点频率越低。这些问题可以通过选择特殊结构的电容来解决。

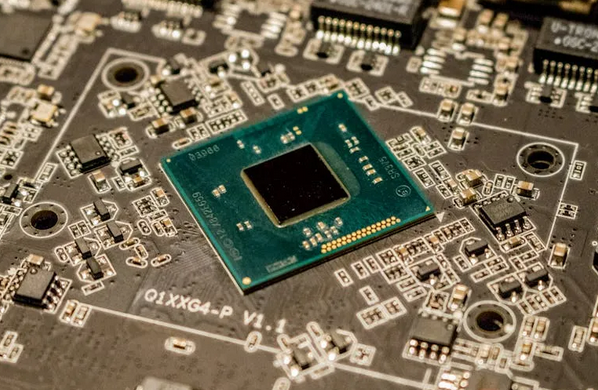

贴片电容的寄生电感几乎为零,总的电感也可以减小到元件本身的电感、通常只是传统电容寄生电感的1/3~1/5,自谐振频率可达同样容量的带引线电容的2倍(也有资料说可达10倍),是射频应用的理想选择。

传统上,射频应用一般选择瓷片电容。但在实践中,超小型聚脂或聚苯乙烯薄膜电容也是适用的,因为他们的尺寸与瓷片电容相当。

三端电容能将小瓷片电容频率范围从50MHz以下拓展到200MHz以上,这对抑制VHF频段的噪声是很有用的。要在VHF或更高的频段获得更好的滤波效果,特别是保护屏蔽体不被穿透,必须使用馈通电容。

2、电容在电路设计的有用技巧

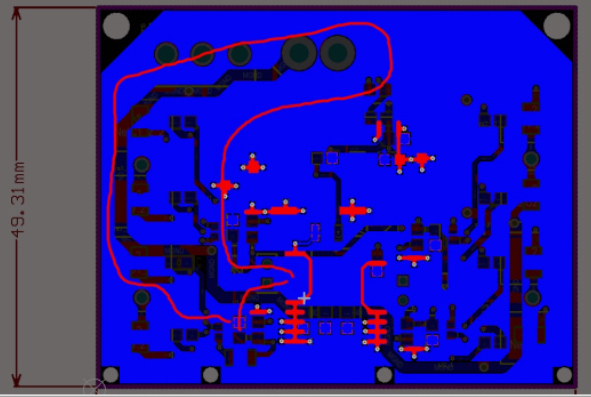

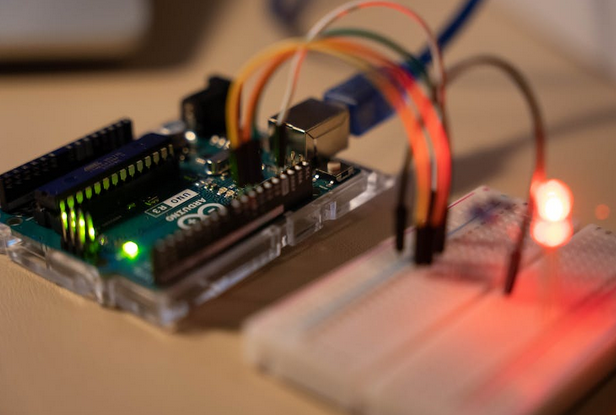

①去耦电容的安装方式与PCB设计安装去耦电容时,一般都知道使电容的引线尽可能短。但是,实践中往往受到安装条件的限制,电容的引线不可能取得很短。况且,电容引线的寄生电感只是影响目谐振频率的因素之一,自谐振频率还与过孔的寄生电感、相关印制导线的寄生电感等因素有关。一味地追求引线短,不仅困难,而且根本达不到目的。这说明要保证去耦效果,在PCB设计时,就要考虑相关问题。设计印制导线时,应使去耦电容距离芯片电源正负极引脚尽可能近(当然电容引线要尽可能短)。设计过孔时应尽量减小过孔的寄生电感。

②干扰电路。电子设备中的单元电路应设计和选用本身电磁能量辐射小、抗干扰能力强的线路形式。小信号放大器应增大线性动态范围,提高电路的过载能力,减小非线性失真;功率放大器工作在甲类状态时,产生的谐波最小;工作在乙类时,应采用推挽形式来抑制二次谐波;丙类状态用于射频放大,为抑制谐波电平应采用锐调谐、高Q滤波器。

③器件和电路的合理布局。将容易受到干扰的敏感元器件和单元电路尽可能地与干扰源远离;输出与输入端口妥善隔离;高电平电缆与脉冲引线与低电平电缆分开排布。

暂无评论