无线通信的迅猛发展激发了射频收发器设计的热潮,作为高性能压控振荡器(VCO)和无源滤波器等集成电路模块的重要元件,片上电感市场在近年来基本上是处于炙手可热的电子市场之一,但长久地发展必然带来了多种问题,所以我们接下来看看金属互连线电感的问题及解决方法。一般来说,金属互连线片上电感存在的问题主要集中在其品质因数低和占据芯片面积大等多个方面,具体如下:

1、品质因数低

最通用的电感品质因数定义是电感贮存的峰值磁能和峰值电能之差与其一个周期内的损耗之比。平面螺旋电感的不同线圈之间的耦合系数比较低、较大的串连电阻、相对大的寄生电容和衬底的损耗使得片上电感的品质因数不高。尤其是标准CMOS工艺的衬底是半导体,在衬底的电能和磁能损耗较大,使得标准CMOS工艺设计片上电感成为难题和热点。

2、电感占据了太大的芯片面积

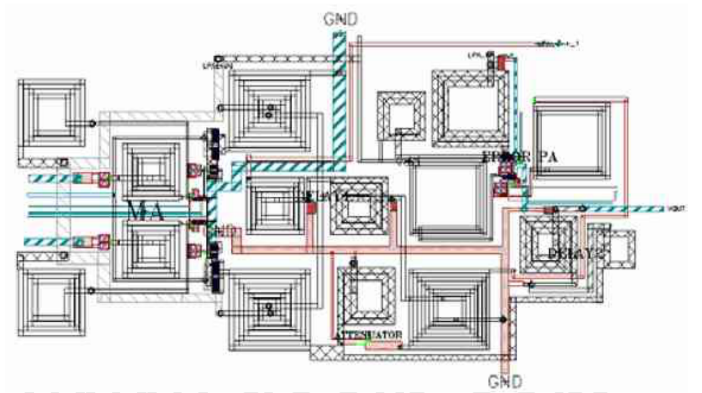

随着工艺技术的提高,芯片的特征尺寸在不断地缩小,单位面积的晶体管数量在迅速增加,成本不断地降低,而电路所需的电感值没有下降,这意味着电感的有效面积不会随着特征尺寸的降低而降低。电感占据的面积与晶体管占据的面积比在不断地加大。如图所示是一个线性功率放大器版图,整个功放的绝大多数面积是电感。降低电感的芯片面积,成为在保证电感性能之外的--一个重要课题。

3、串扰

由于片.上电感可以采用保护环和地屏蔽等方法进行电场屏蔽,使得电感附近的电路不受电感电场的影响。使用标准CMOS工艺,没有方法屏蔽电感磁场而不降低其性能,不可避免的要拉大电感与其他的电路间距,降低电感磁场的耦合,这样就增大了电感的实际芯片占有面积。

片上电感的研究需要电磁场、高频电路、工艺、数学等背景知识。往往研究电感

的人具有物理背景,而缺少电路知识,将电感作为一个元器件研究。具有电路知识的人往往不具备物理背景,很难对电感优化设计,电感的设计要根据电路的需要来调整电感的电感值、寄生电阻和寄生电容,达到电路的性能最佳。

暂无评论