什么是PCB信号等长处理

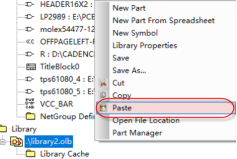

在做PCB设计时,为了满足某一组所有信号线的总长度满足在一个公差范围内,通常要使用蛇形走线将总长度较短的信号线绕到与组内最长的信号线长度公差范围内,这个用蛇形走线绕长信号线的处理过程,就是我们俗称的PCB信号等长处理。

为什么要等长

一般在PCB设计时,进行信号等长处理的原因有以下几个。

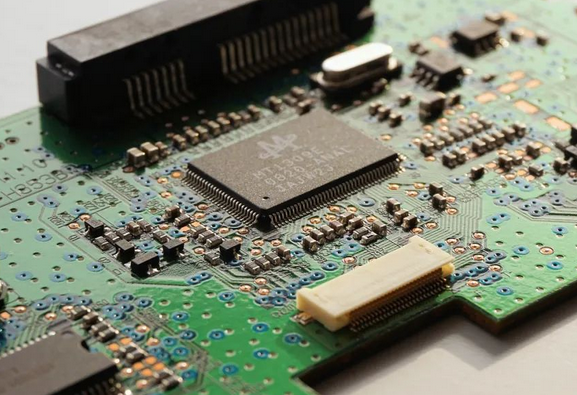

1、 一般做等长是为了满足系统对信号组的等时,即为了满足此组内信号的时序须满足系统要求。比如对于DDR,其数据信号每8位一组,做+/-25mil处理,如果此组信号等长没有在此公差范围内,信号线长度相差太大,会导致其相对延时较长,最终导致DDR运行速率不高。但是我们做设计时有时发现DDR器件等长没有做,其成品也可正常运行,并没产生影响,原因一般是系统软件对此信号做了延时处理,软件上做了时序控制。对于带状线来说,每1ps延时对应的走线长度是6mil左右,所以一般信号组长度每相差6mil,其总延时在1ps。一般我们做设计时等长并不用控制的太小,控制到+/-10mil左右就已经很好了。+/-10mil 等长和+/-1mil 等长,在时间上的差异不超过 4ps,一般的IC信号裕量都不止4ps,所以做等长时没必要控制的过小,从而导致自己设计走线困难。

2、 差分信号(差分信号分析可查看我们的公众号往期文章)等长是为了满足相位,一对差分信号相位相差180度,如果长度相差太大,会导致其相位偏移过大。

PCB设计时等长处理方法

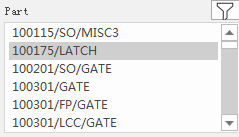

1、 设计时我们首先要看器件的数据手册,根据数据手册获取需要等长的信号及其等长范围。对于常规的信号,如DDR、网口、HDMI信号等内容,可根据设计经验进行等长。

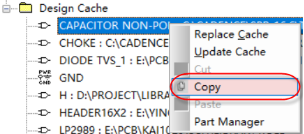

2、 在做等长之前,要先找到需要做等长的信号组中的最长的信号线,想办法将其缩短,以减短此组内所有信号线的长度及其他信号线所需要绕线的长度。

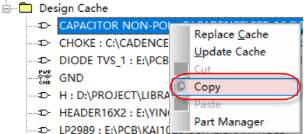

3、 等长处理时要考虑好空间较小位置信号的绕线,尽量先调走其附近信号,将此部分信号处理,以免做到最后其绕线空间不够,等长不出来。

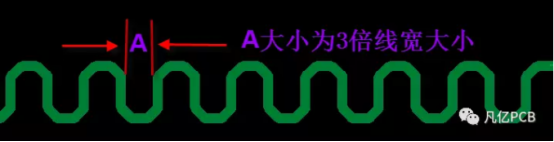

4、 绕等长时,其蛇形线边缘间距一般要保持3W,即3倍线宽大小,如果空间限制,至少要做到2W。

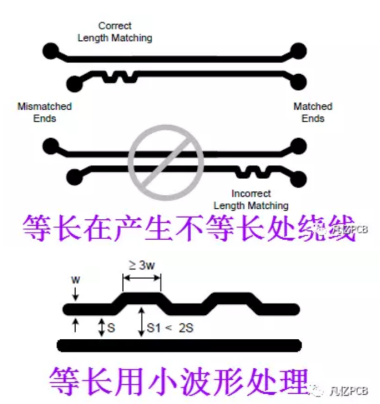

5、 对于差分信号,其等长误差一般控制为+/-5mil,绕等长的位置在产生长度误差的一端,绕的波形为小波形。

暂无评论