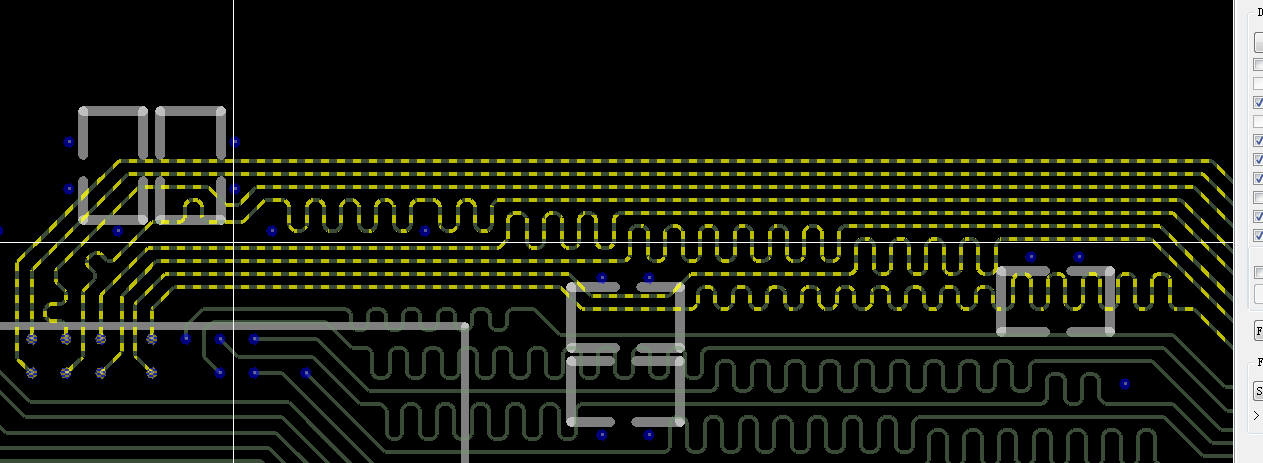

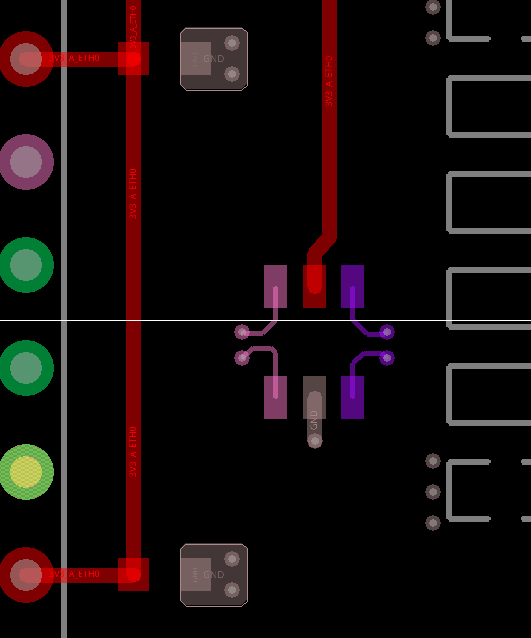

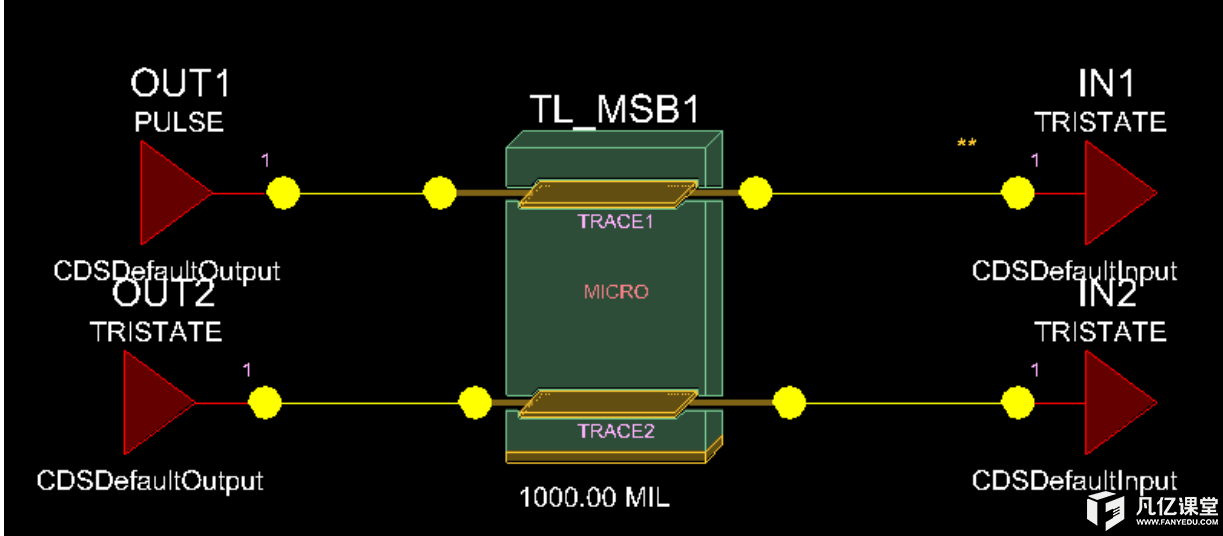

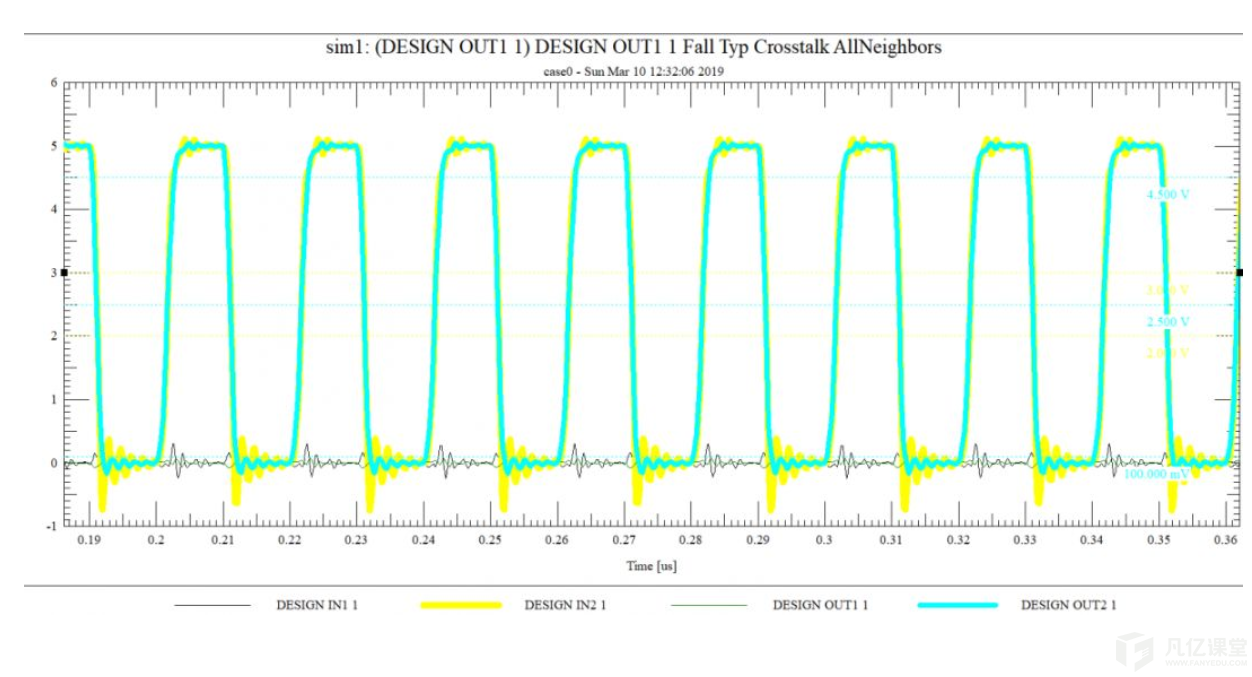

串扰是两条信号线之间的耦合、信号线之间的互感和互容引起线上的噪声。容性耦合引发耦合电流,而感性耦合引发耦合电压。 PCB板层的参数、信号线间距、驱动端和接收端的电气特性及线端接方式对串扰都有一定的影响。下面是在SigXplorer里面搭建了一个串扰的仿真链路,黄色部分就是得到的信号之间的串扰分析结果。

(1)很多PCB工程师都知道串扰,知道3W,但是在遇到实际问题的时候因为受到空间的影响,间距太近没有空间调整。只能做到在空间距离允许的情况下尽量拉大布线的间距,没有直观的手段来衡量评估串扰的大小是否能够符合设计的要求。今天我们将和小伙伴一起来使用Allegro 17.2来分析布线的耦合系数对串扰进行评估,通过这个功能可以让工程师可以直观地评估间距和串扰的关系,用具体的数据来量化设计,让工程师做到设计心中有数。

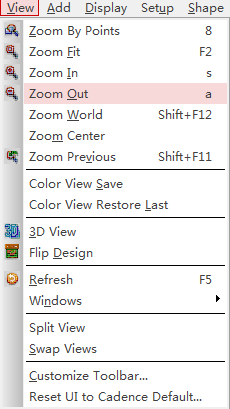

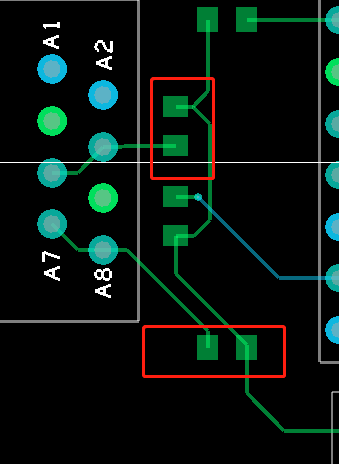

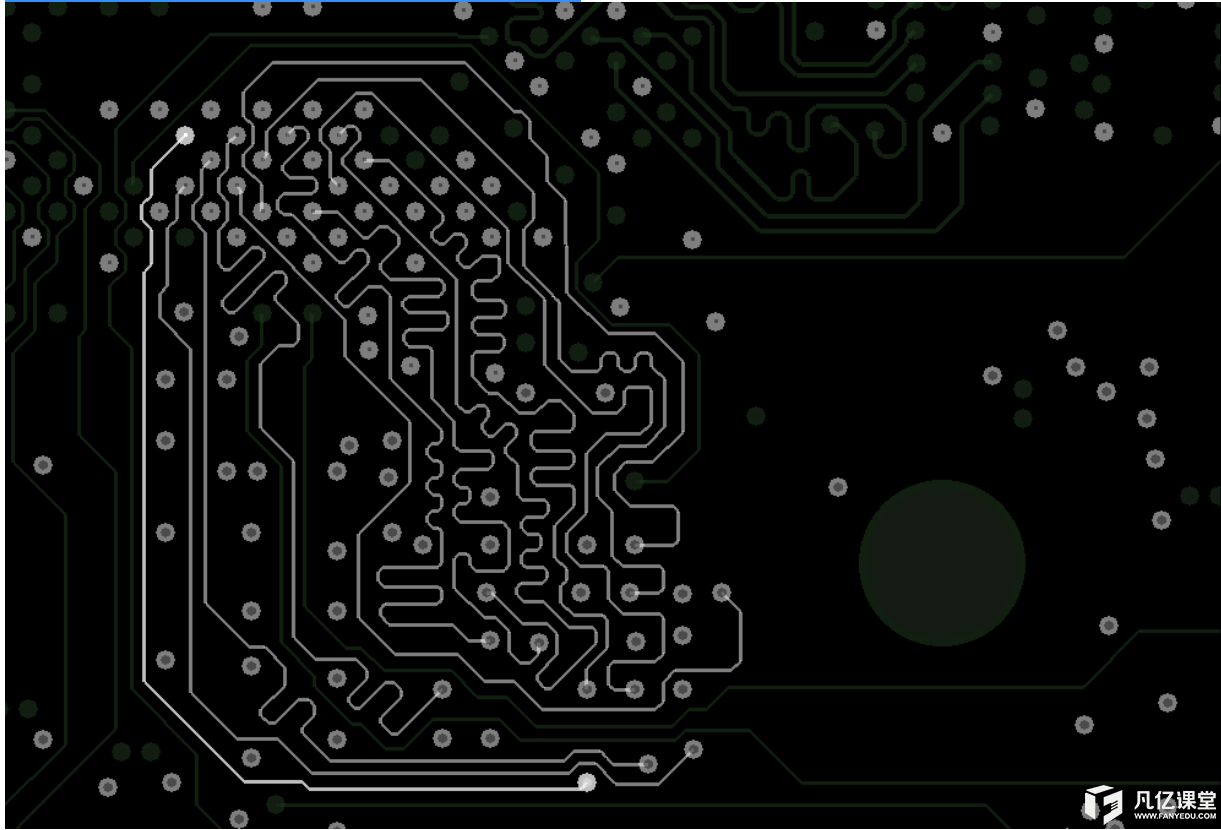

(2)下面这个图是一个EMMC的信号,我们将使用这个实例文件来分析布线之间的耦合情况。一般来说,耦合分析需要设置耦合考虑的起始百分百也就是考虑耦合的开始阀值。通俗的说法就是当布线之间的耦合超过多少的时候需要进行考虑。比如2%,也就当耦合超过2%的时候才考虑,小于2%以下的时候不考虑耦合的影响。那么耦合要超过多少耦合率才是不合格的呢? 这个就没有一个统一标准了。通常的工程实践中可以按照5%来评估,也就是说,当耦合率超过5%的时候就需要引起工程师的重视,超过10%的耦合率是违反了设计规则的,耦合将不能被允许接受。

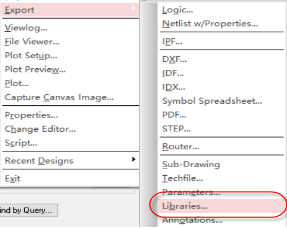

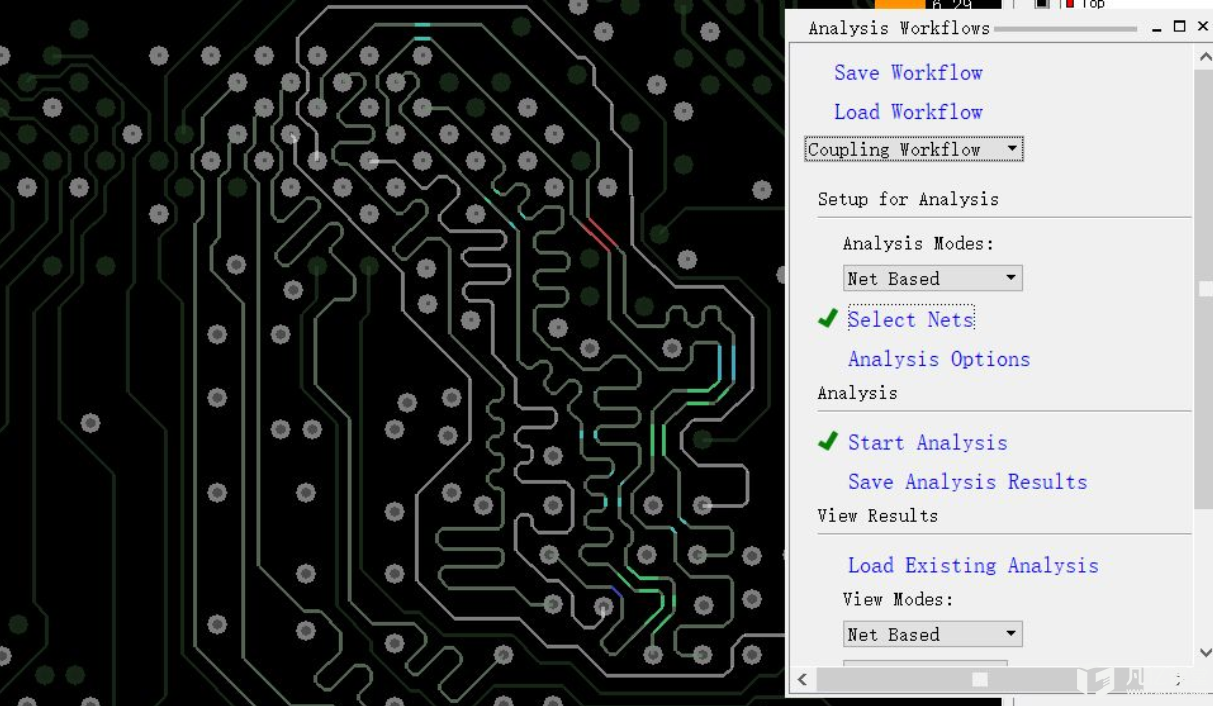

(3)开启Analysis Workflows,选择Coupling Workflow开始设置其他参数,选择需要分析的网络。

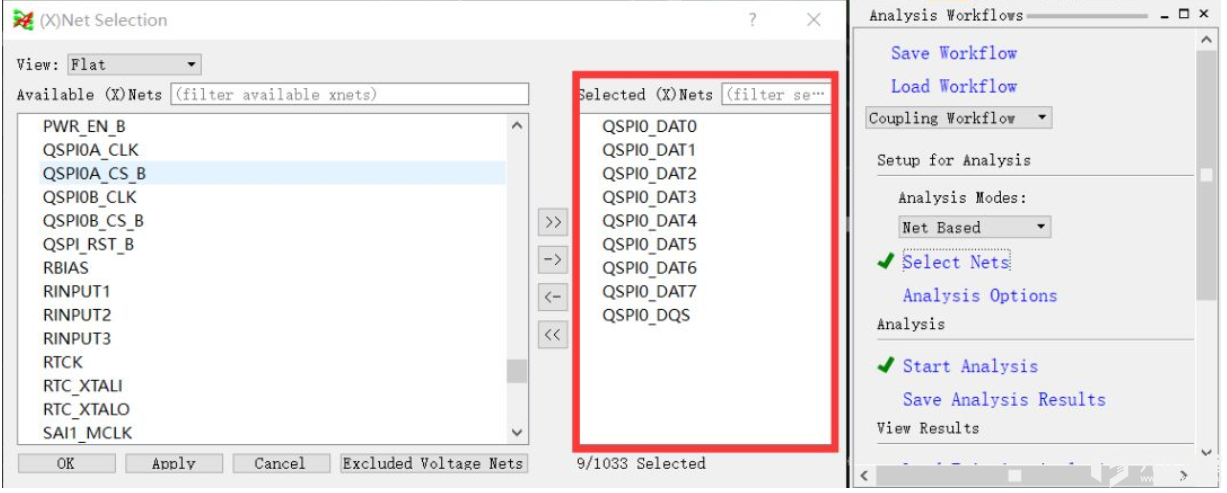

(4)在流程中选择需要进行分析的NET网络,比如QSPIO_DATA0-7,QSPIO_DQS等信号。

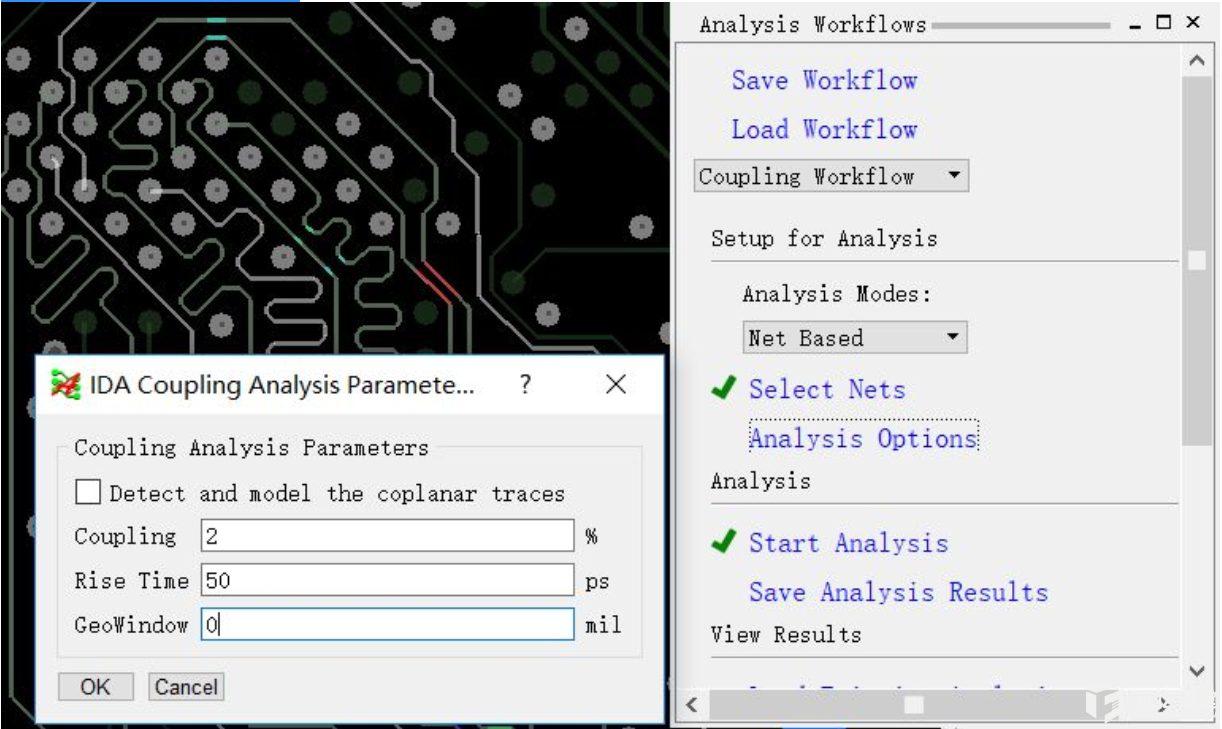

(5)设置仿真的参数,Coupling设置超过2%以上的耦合才予以考虑,设置仿真参数后,点击选择start analysis就可以进行仿真。

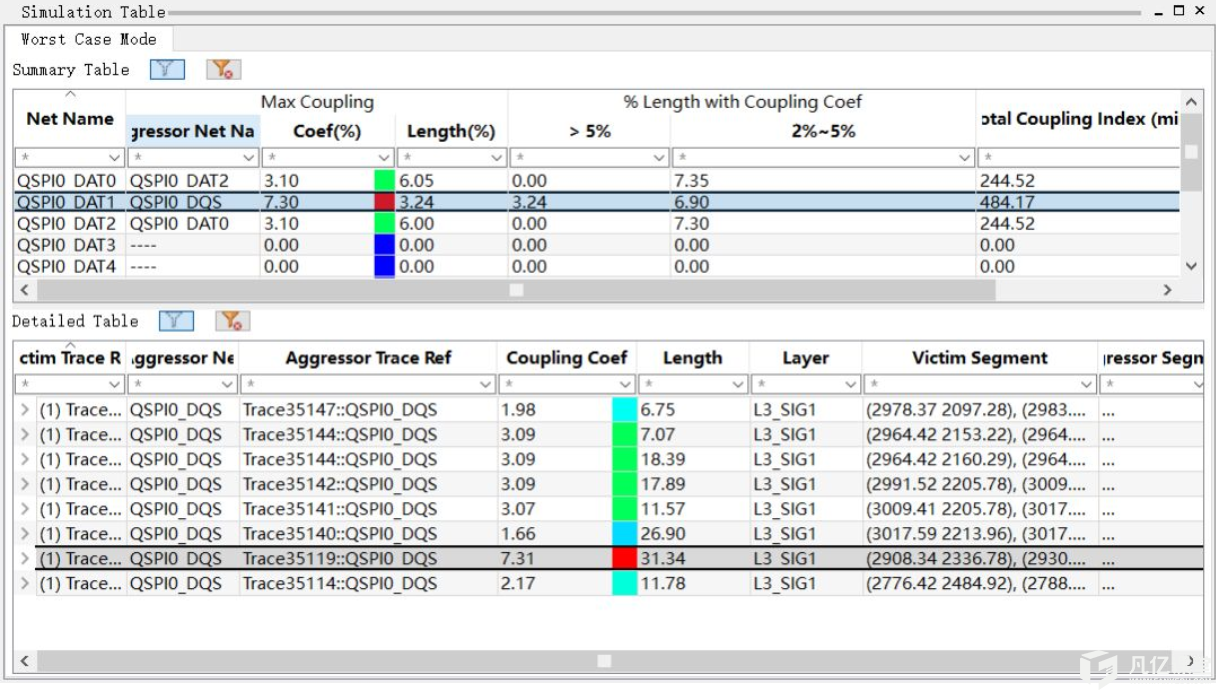

(6)仿真结束后显示的结果有两种方式,一种是表格的方式,一种是耦合系数图的方式显示出来。

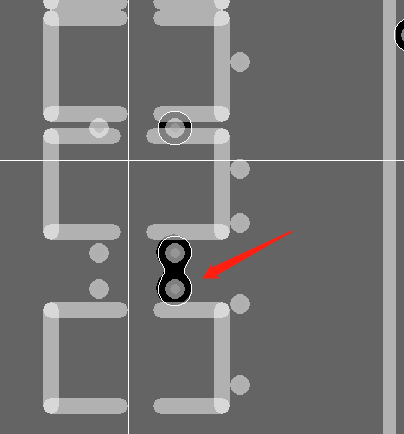

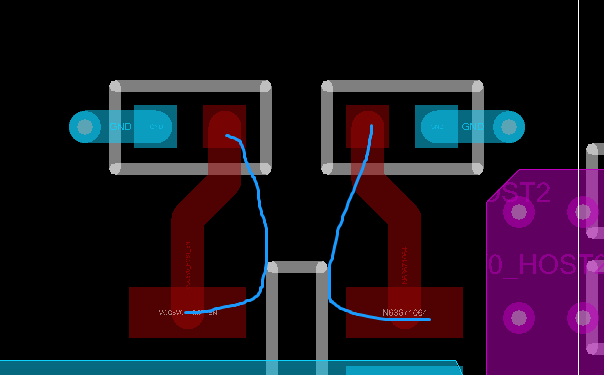

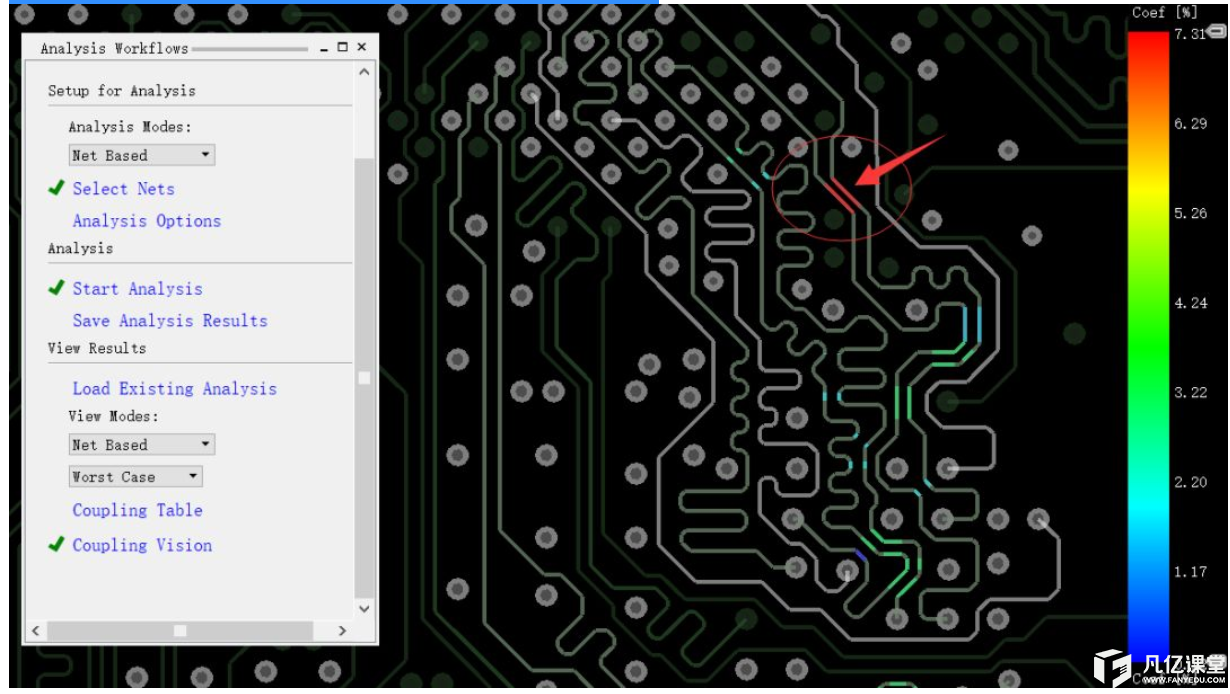

下图是图标的方式显示出来的结果,从表格中可以看出QSPIO_DATA1和QSPIO_DQS这两个网络耦合的系数为7.30%,其中耦合系数在2%-5%长度为6.9(总线长度的比例数字),耦合系数大于5%的长度为3.24(总线长度的比例数字),耦合发生在L3层。工程实践中,需要关注耦合系数大于5%以上的布线长度,这个布线长度越小越高,若长度比较长,可以考虑将这些布线间距人为的拉开减少耦合。

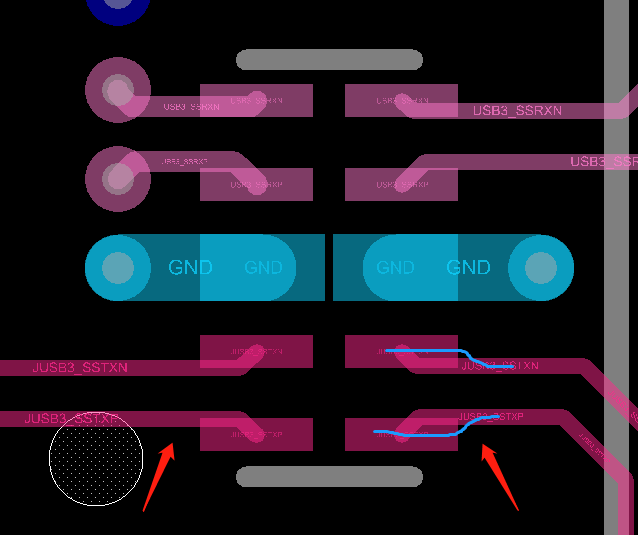

(7)在切换到Coupling Vision耦合系数图的显示方式的时候,可以用鲜艳的红色标识出来耦合系数较大的部分。如下图中的情况,可以明显的看到QSPIO_DATA1和QSPIO_DQS这两个网络存在明显局部平行布线情况,局部耦合系数为7.31。

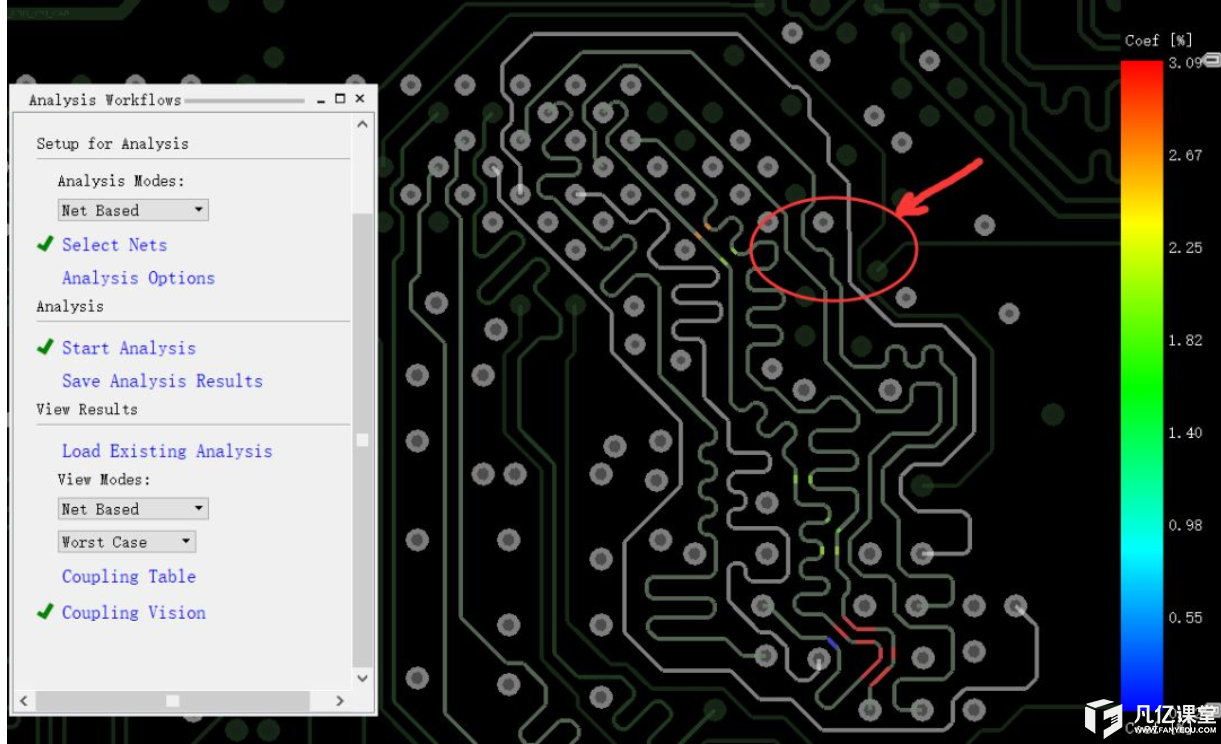

(8)通过对QSPIO_DATA1和QSPIO_DQS这个部分的布线进行调整加大布线距离之后,可以看到该部分的耦合系数明显降低。

分析小结

通过Cadence Allegro 17.2布线耦合系数分析,可以用量化的指标看到电路板上布线的耦合情况,针对超过标准的部分布线可以轻易的进行修改,然后再次进行耦合仿真。这样做成为减少串扰的有效手段,对于提升设计效率以及设计的准确性是有很大帮助。阅读完这篇文章的小伙伴可以自己去试一试这个新功能,让自己的设计做到心中有数,胸有成竹。

声明:本文来源于耀创深圳 旅行的苏西,版权归原作者所有。

如涉及版权或对版权有所疑问,请第一时间与我们联系