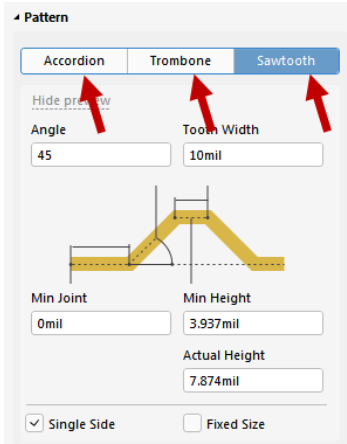

Altium Designer 21全新功能- 蛇形等长快捷调节

0 评论

7574 浏览

2022-04-29 11:29:19

文章

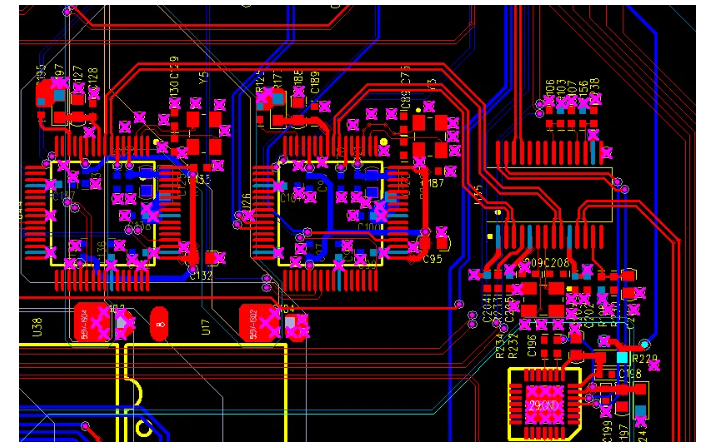

受规则的限制,操作不了蛇形线,只能硬生生按照最原始的方法把差分线走成等长

0 评论

2437 浏览

2021-12-14 16:56:11

文章

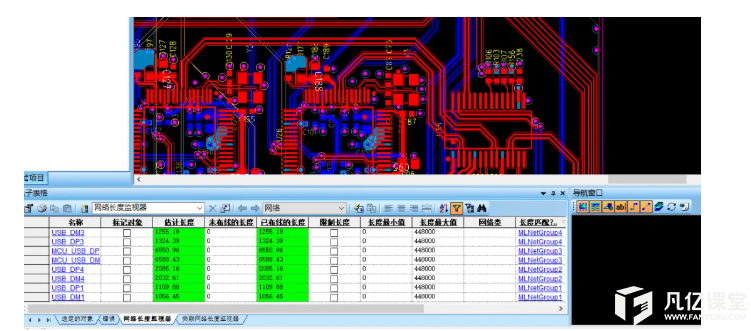

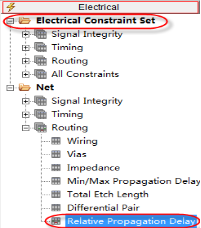

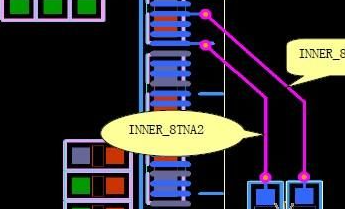

【Allegro软件PCB设计120问解析】第82问 在Allegro软件做等长设计时候,如何让等长进度条跟随蛇形线移动呢?

1 评论

4553 浏览

2021-04-02 14:13:49

文章

2021-05-11 11:17:22

2021-05-11 11:17:22

3811

3811

0

0