凡亿教育-小辣椒

凡事用心,一起进步打开APP

公司名片可测性设计中常见问题及解决方法(上)

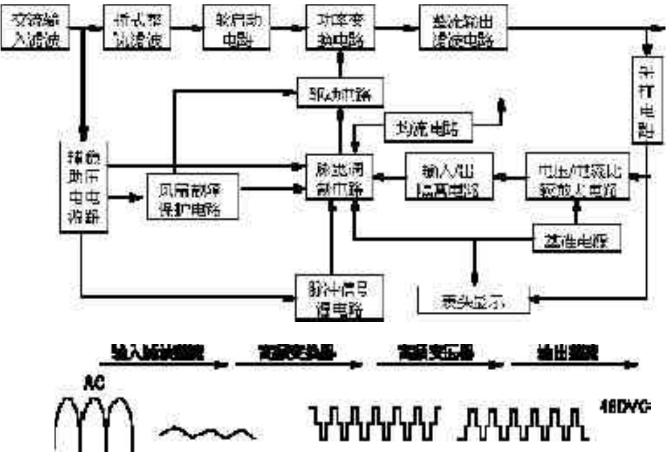

在IC设计中,可测性设计是很重要的内容,如果设计不当,将导致后续测试无法进行,或覆盖率降低,这两种都会大幅降低IC产品的竞争力,因此IC设计必须做好可测性设计,保证测试无误,下面就盘点可测性设计中遇见的问题及解决方法。

1、设计中用到了时钟的两个边沿;

多边沿的处理:设计中的寄存器最好使用一个时钟沿,若在一个扫描链中,一些寄存器用上升沿,一些寄存器用下降沿,则覆盖率会受到影响,若设计中必须用到两个石中盐,则最好将不同时钟触发的寄存器放入不同的扫描链中。

2、设计中存在多个时钟域;

多时钟域的处理:在一个设计中往往存在多个时钟,这些时钟分别做成时钟树,有不同的延时,而在扫描模式下,时钟信号统一来自外部端口,扫描时钟信号经过不同的时钟树,会有不同的延时,因此表现为较大的时钟偏差。这时候,当数据在扫描链中进行移位时,可能将产生建立时间、保持时间错误,解决方法是在扫描链上跨两个时钟域的地方接入一个锁存器(lock up锁存器)。

3、有门控时钟;

在许多设计中,例如在低功耗设计中,存在着门控时钟逻辑,而在扫描时,时钟不能被阻断,这时候需加入控制逻辑,以避免时钟门控逻辑的影响。

4、有内部生成的时钟信号;

内部生成时钟信号的处理:在IC系统中,经常用到内部生成的时钟信号,最常见的例子是分频时钟,若内部生成的时钟驱动的寄存器直接接入扫描链中,则一些寄存器的时钟信号是另一些寄存器的数据输出,这样在扫描移位时将引发问题。

解决方法:利用MUX,在测试时使用外部引脚输入的时钟。

由于文章篇幅的限制,将此文分为上下两篇,欲看下篇可点击右侧链接《可测性设计中常见问题及解决方法(下)》。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表凡亿课堂立场。文章及其配图仅供工程师学习之用,如有内容图片侵权或者其他问题,请联系本站作侵删。

相关阅读

进入分区查看更多精彩内容>

暂无评论