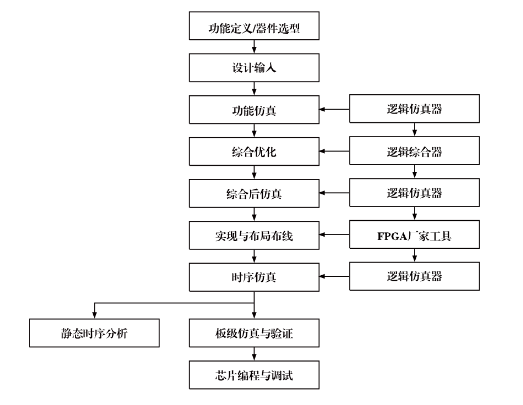

对FPGA工程师来说,可靠性设计是极其重要的,若是没处理好FGPA的触发器,没有满足特定的时序关系,导致FPGA电路不可靠,极有可能产生亚稳态问题,很容易打乱设计步伐,因此,了解FPGA设计的时钟域和亚稳态是很有必要的。

一般来说,亚稳态意味着输出信号不能在预定的时间内进入已知的状态,也就是器件的传播延迟超过了额定值,当发生亚稳态后,即使最后输出稳定下来,也无法保证输出的逻辑值是正确的,在输出信号从亚稳态到稳态的变化过程中,输出信号也许长期游离于非法的逻辑电平值,也可能发生振荡,但不论哪种情况,对下一级门电路来说是一场灾难。

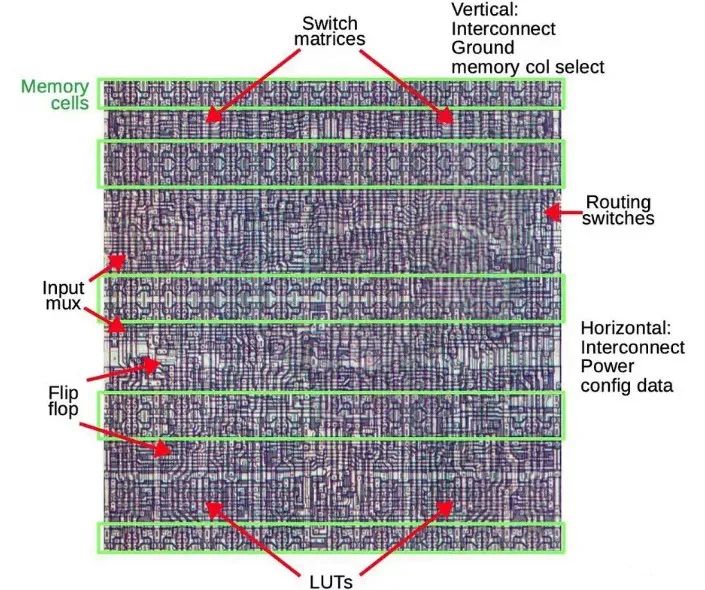

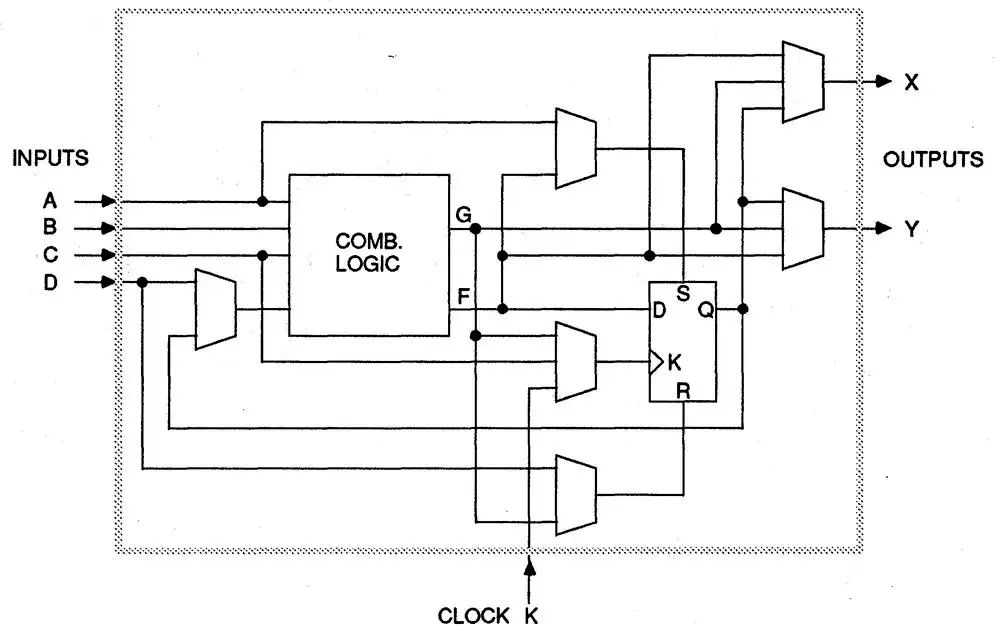

在 FPGA 中,时钟域是个很重要的概念,几乎所有亚稳态的发生都是由于跨时钟域的问题所引起的。要想理解跨时钟域所引发的故障,首先要了解时钟域,以及同步信号、异步信号的概念。所谓时钟域,是指在 FPGA 内部由单一时钟或者由多个但是相位恒定的时钟控制的区域。··个时钟和其派生时钟(通过 PLL 产生)属于同一个时钟域,反转时钟也属于同一个时钟域。如果时钟之间的基准不同,比如来自不同的晶振,即使标称频率相同(通过频率计能看到晶振的频率漂移),也属于不同的时钟域。简单的讲,同步信号是指属于同一个时钟域的信号,异步信号就是指属于不同的时钟域的信号。也可以这样解释,同步信号是指信号与采样时钟之间具有稳定的相位关系,异步信号是指信号与采样时钟之间没有稳定的相

位关系。任何异步信号对于本地时钟域系统都味着一个不稳定的源,因为总是存在这种可能,时钟会在异步信号变化的时候进行了采样。也就是说,因为异步信号会在相对于时钟触发沿的任何位置到达,所以有这种可能,异步信号会在由建立和保持时间界定的时间窗中变化,这就违背了器件的正常工作条件。当发生这种情况时,芯片可能会出现 3 种不同的结果:

(1)识别成功,稳定的输出新的数据

(2)识别失败,继续稳定的输出旧的数据

(3)识别失败,进入亚稳态

因为实际中无法断定究竟会出现上述哪一种结果,所以为了保证工作正常,所有跨时钟域的信号即异步信号不能直接使用,必须全部进行同步处理变为本地的同步信号。

暂无评论