在现代电子设计领域,随着计算机性能的不断提升,高速数据传输变得越来越重要,DDR(双倍数据率)内存模块作为计算机系统的重要器件,其高速PCB布局布线显得尤为关键,正确的布线设计可提升DDR的稳定性、性能和可靠性,下面来总结下DDR模块的高速PCB布线要点。

特性阻抗:单端50欧,差分100欧;

数据线每10根尽量走在同一层(D0-D7、LDM、LDQS),(D8-D15、UDM、UDQS);

①低八位数据组DDR_data_bus:DO-D7、LDM、LDQS;

②高八位数据组DDR_data_bus:D8-D15、UDM、UDQS;

③地址线控制线时钟线设为一组:DDR_addr_buso。

信号线的间距满足3W则,数据线、地址(控制)线、时钟线之间的距离保持20mil以上或至少3W;

空间允许的情况下,应该在它们走线之间加一根地线进行隔离。地线宽度推荐为15-30mil;

VREF电源走线先经过电容再进入管脚,Vref电源走线线宽推荐不小于20mil,与同层其他信影间距最好20mil以上;

所有信号线都不得跨分割,且有完整的参考平面,换层时,如果改变了参考层,要注意考虑增加回流地过孔或退藕电容;

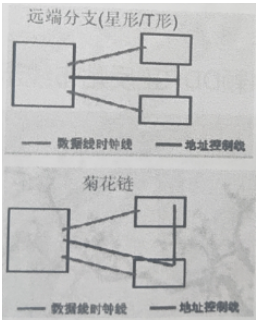

菊花链需得到仿真验证或芯片Layout Guide要求。(一般主控支持读写平衡的才支持菊花链);

所有DDR信号距离相应参考平面边沿至少30-40mil。任何非DDR部分的信号不得以DDR电源参考;

等长要求:

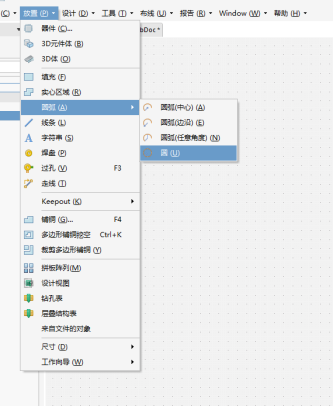

①数据线以 DQS 为基准等长,地址线、控制线、时钟线以时钟线为基准等长,若软件中没有以时钟线为基准的,要手动将其选为基准线;

②数据线最大长度尽量不超过2500mil,组内长度误差范围控制在+/- 25mil,DOS 与时钟线长度误差控制在+/-250mil,单片 DDR 的最大误差不超过 1000mil;

③地址线误差范围控制在+/-100mil;

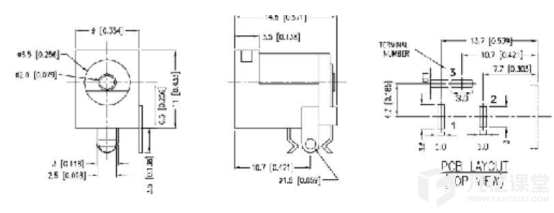

④DQS、时钟差分对内误差范围控制在+/-5mil,设计阻抗时,使对内间距不超 过2倍线宽。信号实际长度应当包括零件管脚的长度,尽量取得零件管脚长度,并导入软件中。

DDR 内存组,所有铜DDR相关的阻容电容,一直向 CPU 方向延伸至CPU的DDR控制器,称作DDR保护区域。这个区域里面需要满足以下条件。

①不得出现与DDR无关的信号;

②必须提供完整的GND平面,信号线下方的平面不得终端;

③必须提供完整的电源平面,信号线下方电源不得中断。

此外,若对PCB设计依然不懂,有许多困惑未得到解决,也可来看看凡亿教育新推出的《高速PCB Layout设计企业培训课程》,专门针对公司打造的企业培训。

此文内容来自凡亿企业培训微信公众号,如涉及作品内容、版权和其它问题,请于联系工作人员,我们将在第一时间和您对接删除处理!

暂无评论