ADC是一个敏感器件,要好好对待它的各个输入端口,才能得到它本身的性能。

常规的,我们会在输入端加入抗混叠滤波器,时钟端使用抖动极低的时钟芯片的输出,那电源输入端呢?

在选用电源时,市面上有这么多LDO或者DC-DC,我们到底应该选择性能何样的,才能挖掘出ADC的本身性能呢。

为什么要好好考虑电源呢?

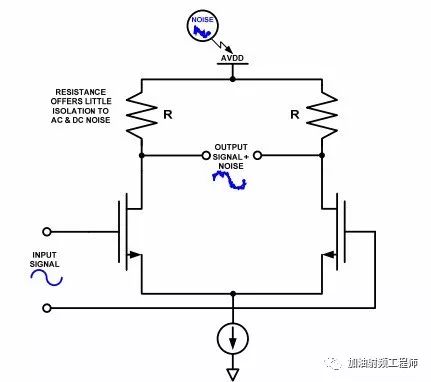

理想的电源就是一个直流信号,但是现实中,会有交流噪声叠加在上面,这些噪声就会影响ADC的性能。

ADC的PSSR和PSMR

ADC的PSSR大体的意思就是,假设有一个噪声信号叠加在DC上,然后测试ADC的输出,看该噪声信号在FFT频谱上的幅度,即体现ADC对电源噪声本身的衰减。

ADC的PSMR,大体的意思是,假设有一个噪声信号叠加在DC上,该噪声信号会与模拟信号输入产生调制信号,看该调制信号在FFT频谱上的幅度。

简单来说,就是假设叠加在DC的噪声信号为1MHz,模拟输入信号为100MHz,而PSSR关注的是ADC输出端1MHz的幅度,而PSMR关注的则是ADC输出端101/99MHz等的幅度。

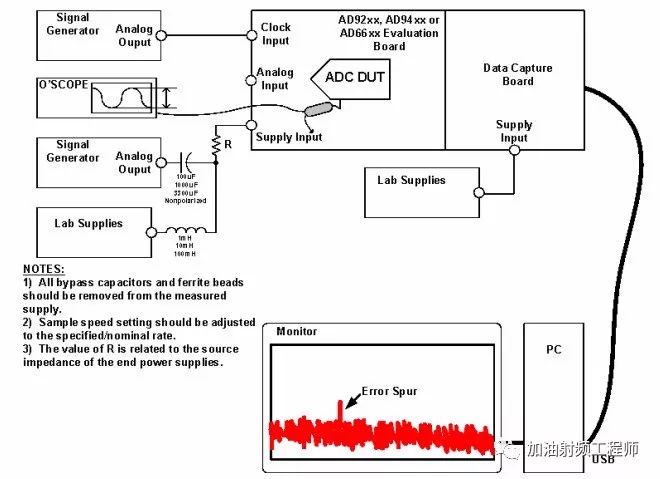

如何测试ADC的PSSR呢?

如上所述,ADC的PSSR即使ADC对电源上叠加的噪声的衰减。所以,我们可以按下面方式进行ADC的PSSR指标的测试:

(1)用信号源产生一频率为f的正弦信号,并将其叠加到直流电源上。

(2)用叠加了交流信号的直流电给ADC供电,同时将ADC的模拟输入端接地。

(3)计算ADC的输出频谱,看其频谱上在f处的杂散电平。

(4)遍历信号源的频率,可以测出ADC的PSSR与杂散频率的关系。

厂家ADC的手册上,有时候会提供PSSR指标,比如60dB就是一个比较常规的值;有时候则没有提到这个指标。这个时候该怎么办呢?

(1) 向ADC的供应商要。要是有原厂FAE直接对接的话,那是很幸福。如果没有的话,可以去厂家官网上的论坛上去留言,碰碰运气,看看会不会有原厂技术人员回答你的问题。我在TI的网站上提了几个问题,感觉技术人员都回答的很及时。不知道是不是负责该版块的技术人员正好特别尽责。

(2) 自己测试PSSR

(3) 如果对成本不敏感的话,可以选择好的LDO,再多加电容滤波。

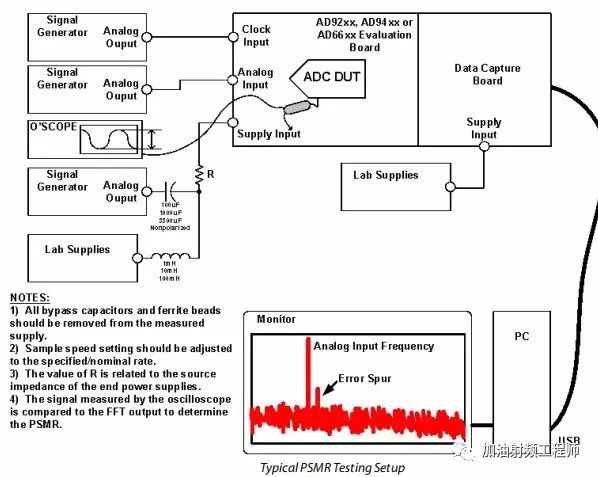

如何测试ADC的PSMR呢?

步骤:

见上面测试ADC的PSSR步骤。

区别在于:

(1)因为是要测试调制信号,所以产生噪声信号的信号源的输出频率一般会设置的比较低,比如1KHz~100KHz。

(2)ADC的模拟输入端也要有信号输入。

电源噪声对ADC性能的影响

有了PSSR和PSMR的数据,就要聊聊怎么将这些数据应用到设计中了。即如何选择电源芯片,以确保能达到ADC需要的要求。

大概步骤如下:

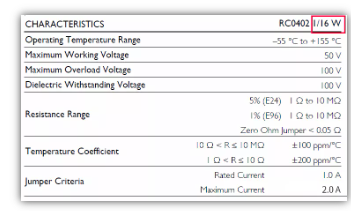

(1)看电源芯片的手册,查看其输出噪声指标,如果用DC-DC的话,还要看其

开关频率。

(2)看ADC手册上给出的PSSR值。

(3)用文中提供的excel文件进行计算.

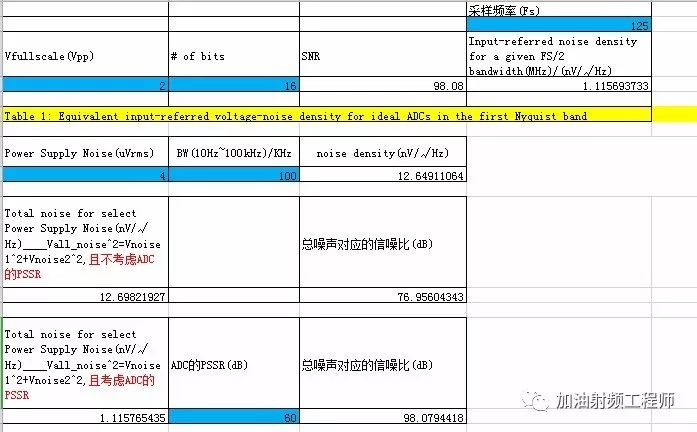

结合excel文件,解释电源的选择

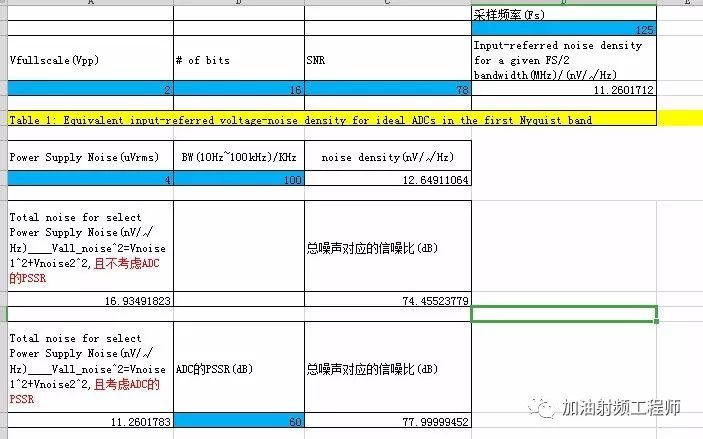

理想ADC

(1)假设ADC的满幅输入是2Vpp,采样频率为125MSPS,位数为16bit,在蓝色域输入对应数字,即可计算出理想ADC的信噪比为98dB,噪声底噪为1.1157nVrms/√Hz。

(2)假设选择了一LDO,其在10Hz~100KHz的带宽内,输出总噪声为4uVrms,即对应12.65nVrms/√Hz。

(3)如果不考虑ADC的PSSR,则算出ADC最终能输出的信噪比为76.95dB

(4)假设ADC的PSSR为60dB,则算出ADC最终能输出的信噪比为98.07dB.

实际ADC

(1)假设ADC的满幅输入是2Vpp,采样频率为125MSPS,位数为16bit,实际SNR为78dB,在蓝色域输入对应数字,即可计算出噪声底噪为11.26nVrms/√Hz。

(2)假设选择了一LDO,其在10Hz~100KHz的带宽内,输出总噪声为4uVrms,即对应12.65nVrms/√Hz。

(3)如果不考虑ADC的PSSR,则算出ADC最终能输出的信噪比为74.45dB,恶化了约3.55dB.

(4)假设ADC的PSSR为60dB,则算出ADC最终能输出的信噪比为77.99999452dB,基本没恶化.

所以,只有在文件中输入相应数据,你就可以计算出你应该选择输出噪声为多少的LDO。当然如果你在LDO的输出端用了滤波措施,在ADC电源供电端加了去耦电容,那对LDO的噪声要求会降低。

暂无评论