凡亿教育-婷婷

凡事用心,一起进步打开APP

公司名片如何降低RF电路的寄生电容?

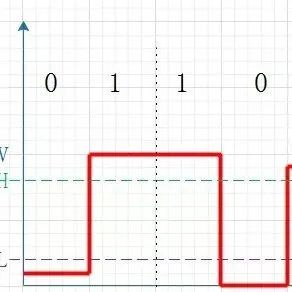

在高频电路设计中,寄生电容的存在是很重要的,它是指在电路中不期望存在的电容,通常是由电路元件之间的绝缘层、导线、接头等产生,它的存在会导致电路的频率响应、增益和相位等特征发生变化,甚至无法正常工作,所以降低RF电容的寄生电容是很有必要的。

1、寄生电容为什么会产生?

①元件之间的绝缘层

在电路中,元件之间通常需要绝缘层来防止短路或漏电,但也会引入额外的电容,影响电路的性能;

②导线和接头

导线和接头是电路中的重要组成部分,但它们也会产生寄生电容,特别是在高频情况下,到西安和接头的电感效应会更加明显,从而加剧寄生电容问题;

③接地和电源

同理,接地和电源也会引入寄生电容,接地和电源引脚与地或电源之间的绝缘层会形成往外的电容,影响电路的性能。

2、如何降低RF电路的寄生电容?

①接地通孔应位于接地参考层开关处;

②没有参考层间隙;

③将器件焊盘与顶层接地连接起来;

④保持差分线路的差分性;

⑤不要在噪声较大的电源层进行RF线路布线;

⑥使用接地隔离高速线路;

⑦RF信号线路附近没有时钟或控制线路;

⑧球帝那人尽量靠近器件。

本文凡亿教育原创文章,转载请注明来源!

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表凡亿课堂立场。文章及其配图仅供工程师学习之用,如有内容图片侵权或者其他问题,请联系本站作侵删。

相关阅读

进入分区查看更多精彩内容>

暂无评论