凡亿教育-小羊

凡事用心,一起进步打开APP

公司名片CMOS输入端逻辑混乱,如何解决?

在电子设计中,CMOS集成电路以低功耗、高噪声免疫和稳定性而受到了广泛应用,然而,当涉及处理多余的输入端时,很容易导致逻辑混乱问题的产生,这种现象经常发生在初级工程师或新手,下面来分析。

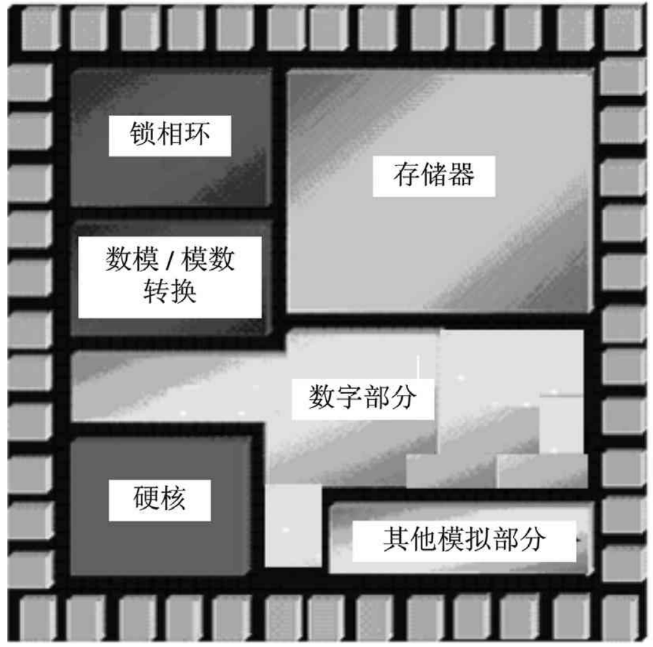

1、CMOS逻辑电平的定义

首先处理这些问题,先来来哦接下CMOS的逻辑电平:

CMOS逻辑电平通常分为高电平和低电平。高电平通常被定义为接近电源电压(VDD),而低电平则接近于地线电压(VSS)。在大多数情况下,CMOS门的工作电压范围是3.3V至5V。

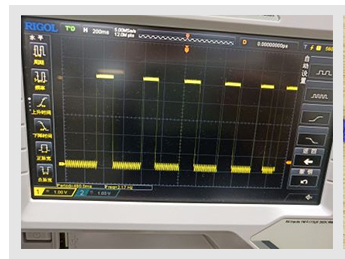

2、CMOS输入端悬空的逻辑行为

在CMOS电路中,若一个输入端未连接到任何逻辑门或信号源,而是被悬空处理,将被视为高电平,这是因为CMOS电路在未连接的输入端上默认是高阻态,即电阻无限大,相当于悬空,这种行为可能导致逻辑混乱,因为一个悬空的输入端会被误截石位一个稳定的信号输入。

3、如何解决逻辑混乱问题?

①连接适当的电阻或下拉电阻

为了避免逻辑混乱,可将悬空的输入端连接到适当的电阻或下拉电阻,以将其电平拉至低电平,下拉电阻的阻值通常根据CMOS的输入阻抗和所需的电流来选择。

②连接上拉电阻

如果悬空的输入端需要被解释为高电平,可将其连接到上拉电阻,以将其电平拉高至高电平,上拉电阻的阻值通常根据CMOS门的输入阻抗和所需的电流来选择。

3、连接其他逻辑门或信号源

如果悬空的输入端需要连接到其他逻辑门或信号源,应确保它们的连接是正确的,并遵循CMOS逻辑门的输入规范。

本文凡亿教育原创文章,转载请注明来源!

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表凡亿课堂立场。文章及其配图仅供工程师学习之用,如有内容图片侵权或者其他问题,请联系本站作侵删。

相关阅读

进入分区查看更多精彩内容>

暂无评论