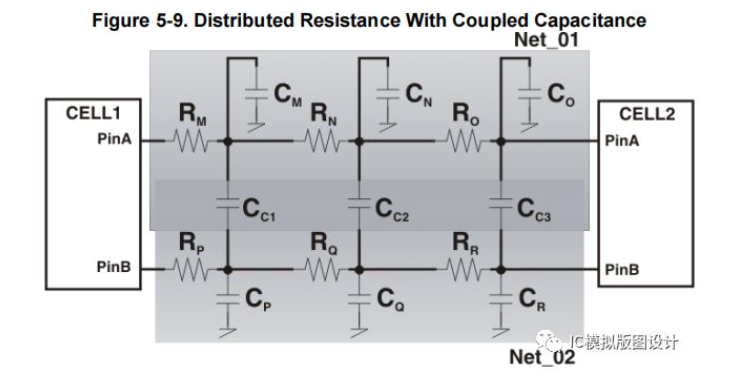

芯片的物理实现过程中不是所有的走线与器件都不是理想的。金属走线与金属走线有重叠有并行。器件也是周围也会有其他器件,或其他走线。最终都会引入额外的电容。就像在电路上额外多出来一些小的电容。无法避免。同样所有导电材料也会有电阻的特性。所以电路中又会有很多小电阻,也是无法避免的。

这些寄生电阻电容的影响就会改变电路频率响应,影响到电流的能力。下面是整理的一些知识点和个人一些经验与大家分析。

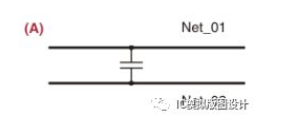

A图-c的输出,展示的是net -to -net的计算电容

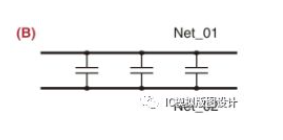

B图-rcc的输出,可以看到电容是根据电阻网络进行了分割,这里寄生电阻没有展示。

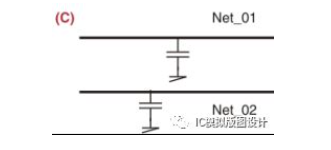

C图是-c with -g输出,lumpedC 全部等效到地。

Couple C 在网表中体现:cc_instance net_01 net_02 c

寄生电容:

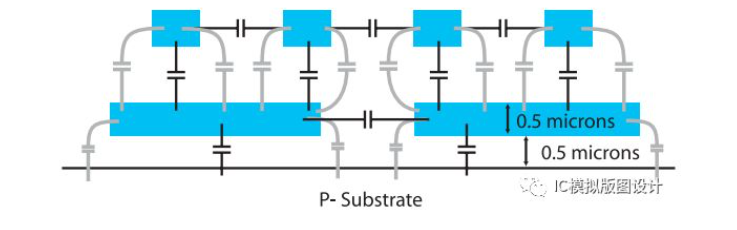

寄生电容哪里来,如下图四根金属走线走在下面两层金属上面。所产生的寄生电容大概分布如下,有金属侧壁间电容,也有上线金属面的电容。同样金属到衬底同样存在电容。

如果我们电路对电容不敏感,就像电源功率级部分,可以不用考虑这些。如果做高频高精度这些模块,寄生电容就很重要。

减小寄生电容的几种方式:

1.走线长度。最简单有效的方式减小走线长度。减小走线长度就减小与衬底的重叠面积,或减小与其他金属的重叠或并行面积。

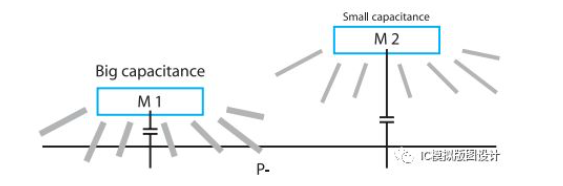

2.金属层次选择。通常离衬底越远,寄生电容就越小,容值与距离成反比。所以可以考虑改用高层金属来减小到衬底的寄生电容。但是还要考虑金属厚度的因素。

另一方面,减小到衬底的寄生电容,也是优化噪声的一种方式。衬底也是有 阻抗的,当噪声信号通过这些寄生电容耦合到衬底,噪声也就会 通过衬底干扰到其他敏感模块。

3.金属走线之间的寄生电容,减小并行走线长度与间隔层次走线。

寄生电容也不是带来都是不好的影响,我们可以利用走线上的寄生RC做些滤波,像最常用decap.

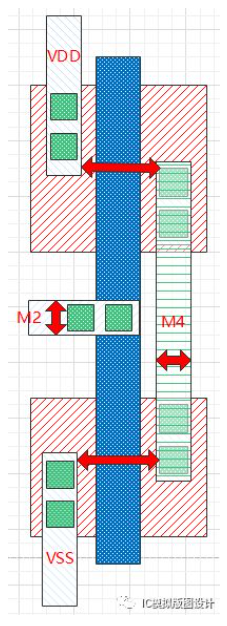

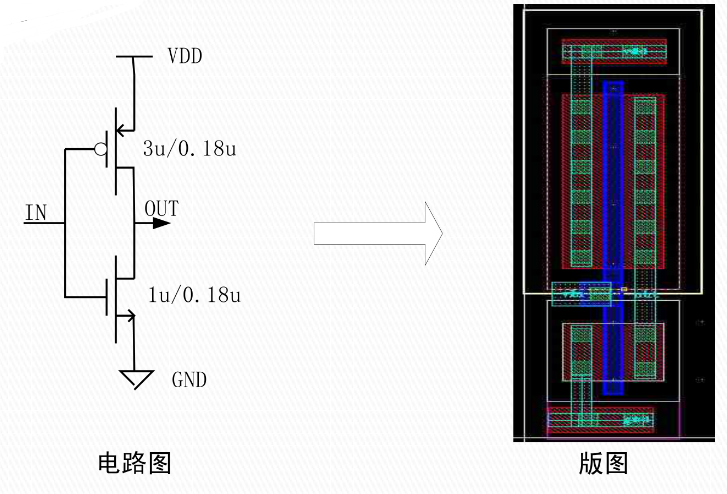

举个小例子,比如下图要优化通路上inv上寄生,那么我们可以从那些地方优化,信号通路走线使用高层,与其他走线尽可能减小相对侧壁面积。所以源漏尽量错开了一些。

寄生电阻:

关于走线寄生电阻想到计算IR drops.

如果电路上有10mv的压降,电路就无法正常工作。那就要通过IR仿真进行优化。下面举例分析走线的优缺点。

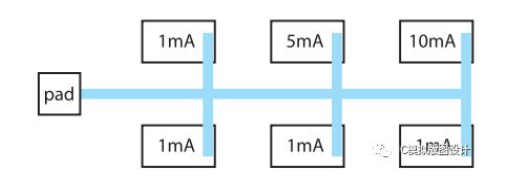

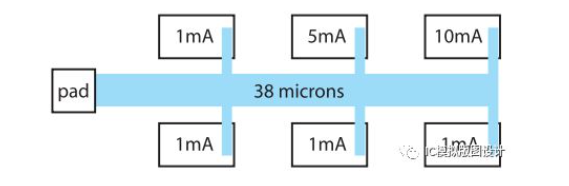

比如19mA需要走38 u的宽度。看下面几种图。

这种走线很明显可以看出最大的电流模块在走线的最远端。这样就需要很宽的金属一直到大电流模块,如下图

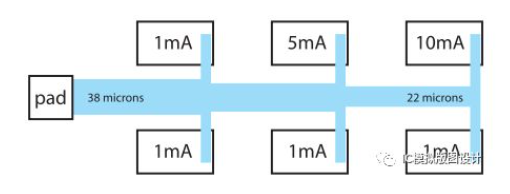

上图最后11mA也不需要这么宽的金属走线,所以可以进一步优化成下图走线。

上图几种走线到底有没有问题??

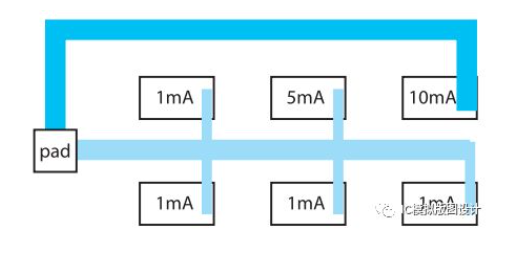

我们还要考虑电压降。大电流也会带来很大的压降,因为公用了总线在总线上有明显的电压降从而会影响到其他小电流模块的正常工作。所以进行如下图优化。

什么样的走线方式取决于电路的功能要求。所以我们在PMU项目中常常可以看到多个LDO都是分别供电,而不是都往一根电源主干上连接。一些电压参考信号或参考地信号都需要一个独立的连接。避免走线带来的压降影响。

减小计算电阻的方式:

1.增加走线宽度,叠层多根并联等。

2.改用方块阻值更低的金属层次走线。

###########################################################

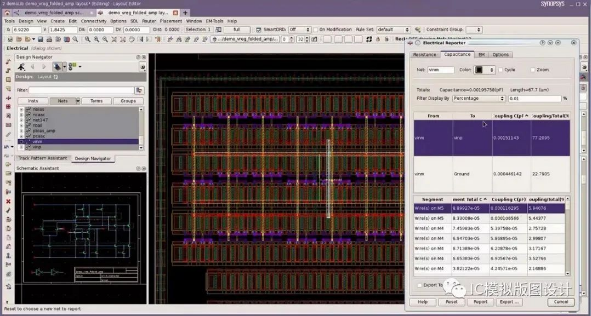

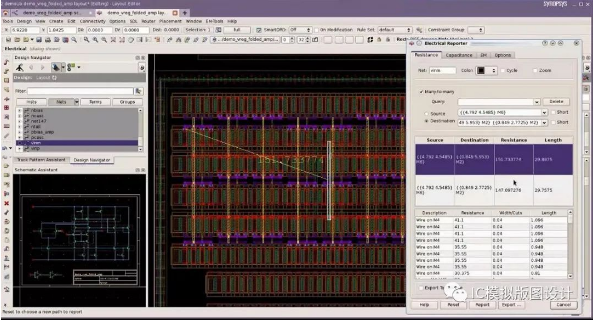

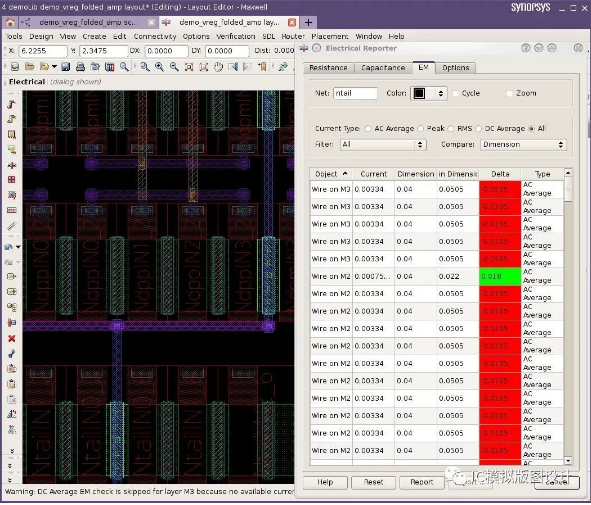

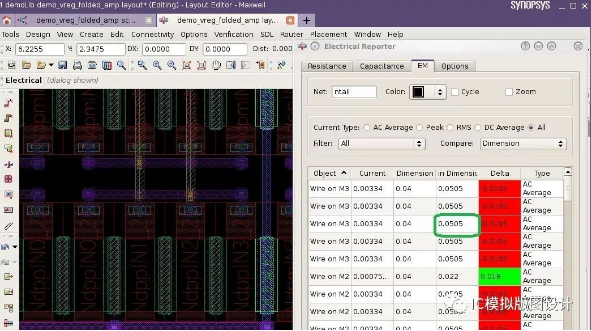

再介绍下CC里in-design reporter C 与 R EM的功能,可以快速及时给出当前指定走线的寄生情况。可以在设计过程中第一时间了解寄生违例。如下图指定net上的couple C 与lump C.

指定net上的两点间寄生电阻,以及分段寄生电阻情况。

指定net上的EM 违例情况分析

给出fix方案建议走线宽度.

声明:本文转载自IC模拟版图设计 公众号,如涉及作品内容、版权和其它问题,请于联系工作人员,我们将在第一时间和您对接删除处理!

暂无评论