上期文章我们最后提到了半导体参数,之所以专门挑一篇文章来说,因为它确实比较重要,可以让我们明白当前各种半导体材料的优势与劣势的原因。

不仅如此,还可以让我们明白一些东西,特别是二极管和三极管的一些特性。

其实这些问题,如果明白了下面参数的含义,那么也就理解得差不多了。

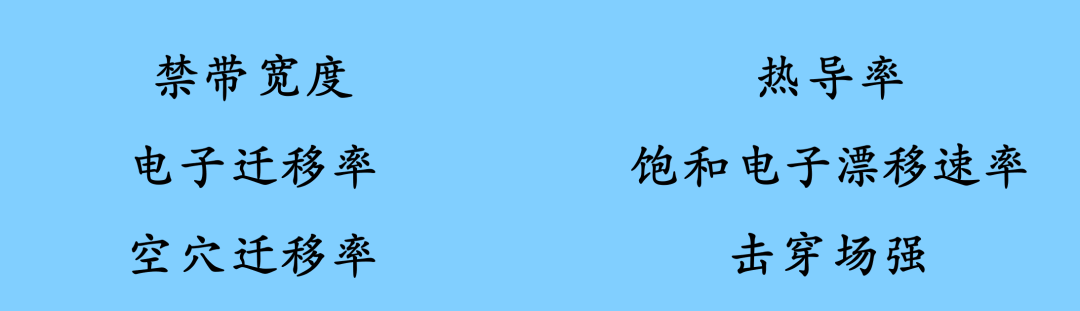

禁带宽度

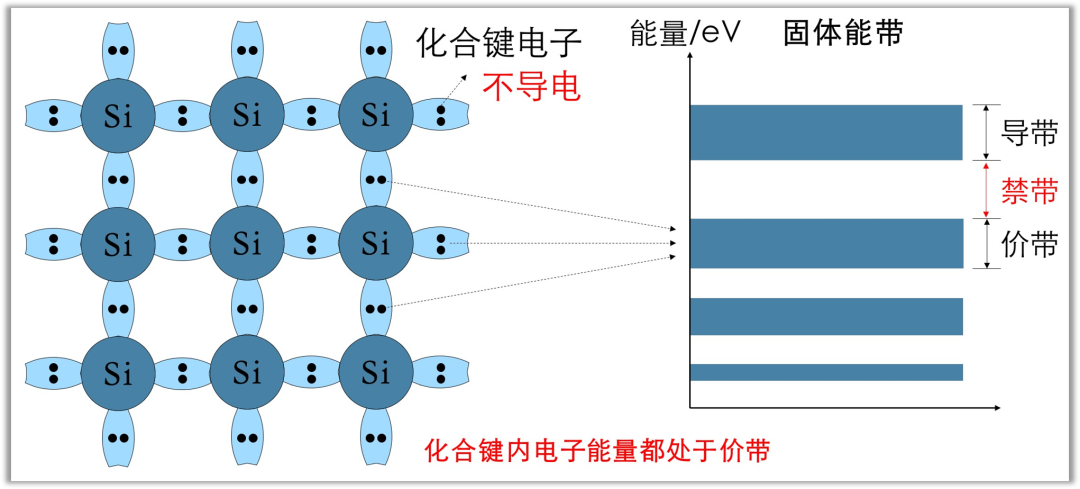

首先来看禁带宽度,这个参数是从能带模型里面来的。

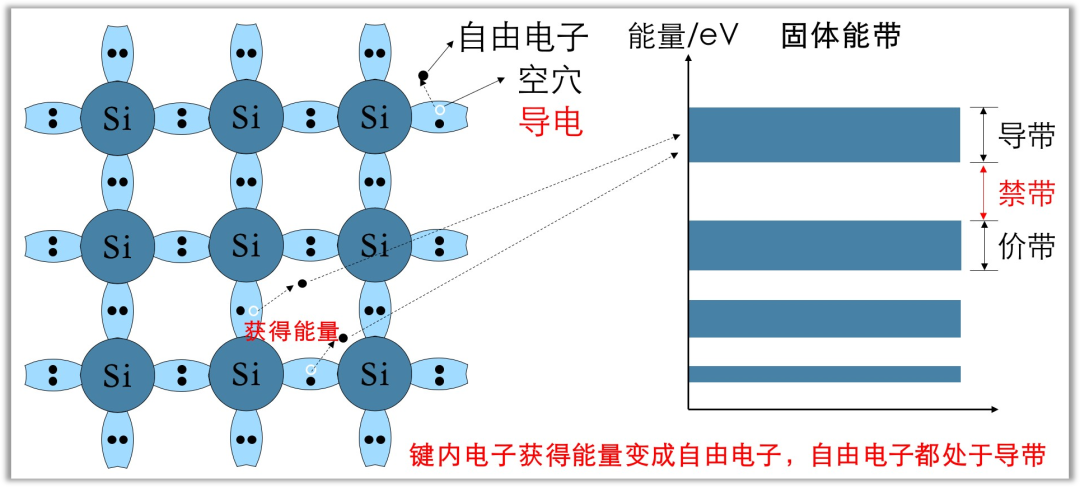

固体中电子的能量是不可以连续取值的,而是一些不连续的能带,要导电就要有自由电子或者空穴存在,自由电子存在的能带称为导带(能导电)。被束缚的电子要成为自由电子,就必须获得足够能量从价带跃迁到导带,这个能量的最小值就是禁带宽度。

这段文字不好理解,那我们就以硅晶体来举例吧。

硅原子最外层含有4个电子,硅原子与硅原子之前通过共享电子形成晶体,这个“共享电子”也可以叫做形成化学键。形成化学键后,电子不能自由移动,所以不能导电。

这些形成的化学键的电子的能量是各不相同的,但他们有个特点,都处于一个范围,这个范围就叫价带。

如果这些化学键的电子获得了能量,从里面跑出来了,那它就成了自由电子。电子离开的地方形成了一个空位,所以构成了空穴,这两者都是可以导电的。同样的,所有这些自由电子的能量也各不相同,但是它们都处于一个范围,这个范围就叫导带。

可以看到,这个导带和价带中间是有间隔的,这个间隔就是禁带。禁带宽度的大小实际上是反映了价电子被束缚强弱程度的一个物理量。

禁带宽度越大,价电子必须获得比较高的能量,才能从化合键里面出来成为自由电子。所以禁带宽度越大,能够因为分子热运动成为自由电子的数量越少,导电性能越差。

等等,扯了半天这个有什么用?没发现禁带宽度大有什么用?

别急,才到问题的一半,汗。。。

在这之前,我们来复习一下PN结,因为做晶体管必然少不了PN结。

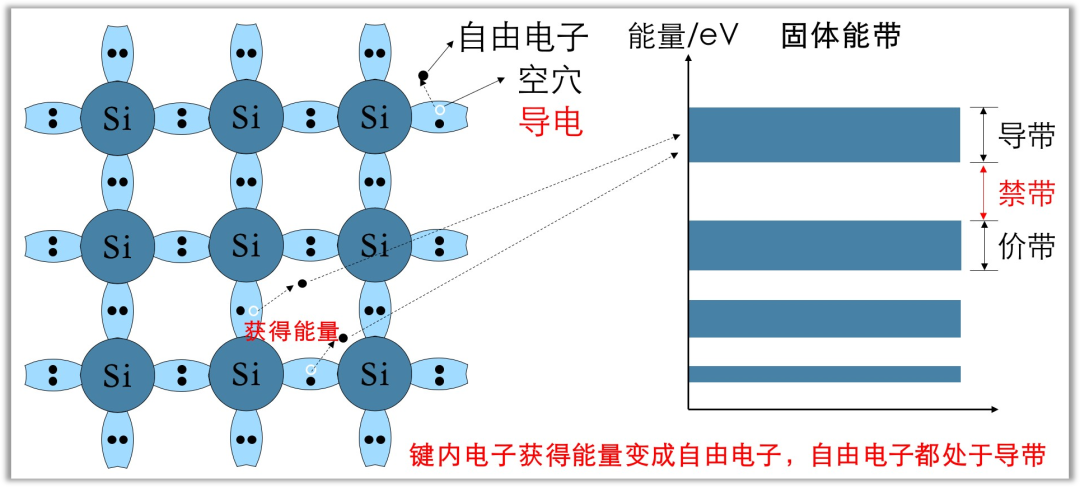

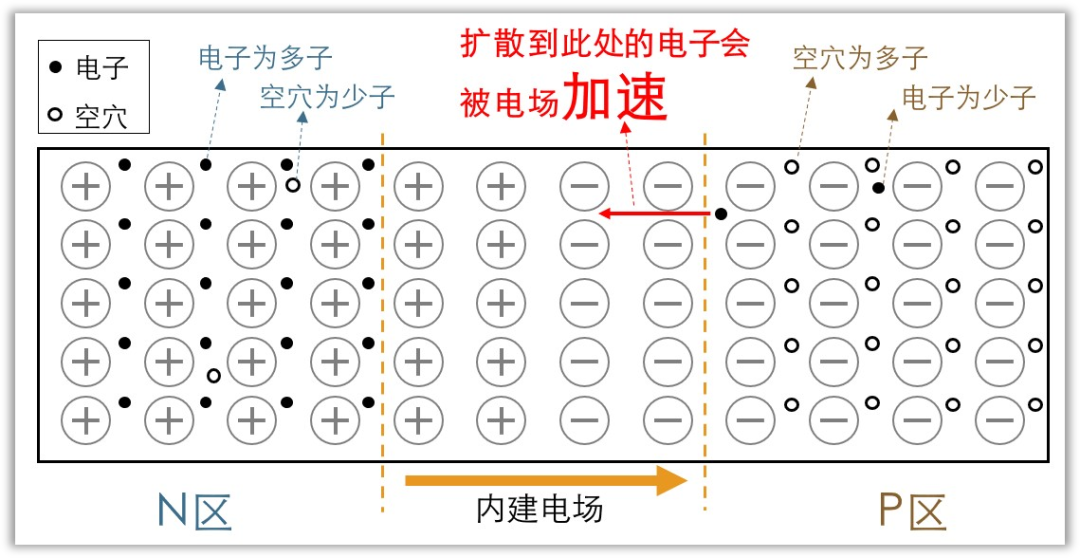

我们知道,PN结反偏是有漏电流的,这个漏电流是由少子的扩散形成的,虽然很少,但是会有。

也就是说,会有电子从中间的内建电场区经过。并且,电子会在这个区域被加速。

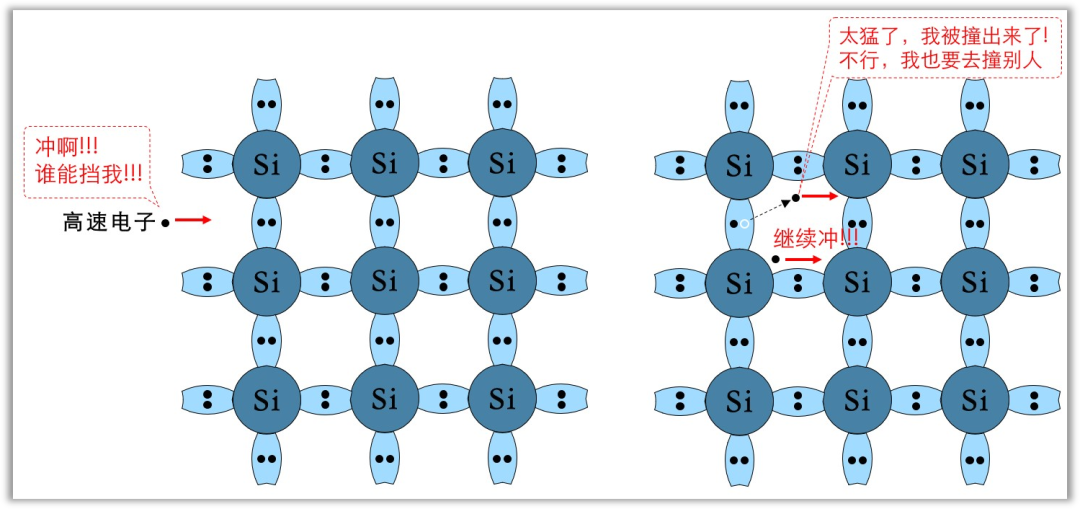

如果电压足够大,场强足够高,那么电子会被加速到较高的能量与原子相撞,原本在化学键里的电子会被撞出来成为自由电子。这个新产生的自由电子又受到电场力加速,去撞击其它的原子产生新的自由电子。

这样“一生二,二生四,子子孙孙无穷尽也”,大量的自由电子产生,电流急剧增大,这也就是“雪崩击穿”。

如果说禁带宽度比较大,价电子被束缚的比较紧,那么就不容易被撞出来了。

所以呢,禁带宽度大,能抗住的场强也就越高,耐压也就越高。同等耐压的器件,PN结就可以做得更薄,器件也能更小,又会带来寄生电容小的好处,器件也就能在更高的频率工作。

当温度上升,电子更容易获得能量。当温度上升到一定程度的时候,会有很多化学键里面的电子获得足够的能量变成自由电子,这样就破坏了半导体的特性。

试想一下,温度上升,自己产生的载流子比掺杂产生的载流子数量还多,那掺杂也就失去了意义,晶体管的功能也就失效了。

禁带宽度越大,需要升到更高的温度才能使化学键里面的电子变成自由电子,也就是说能工作在更高的温度。

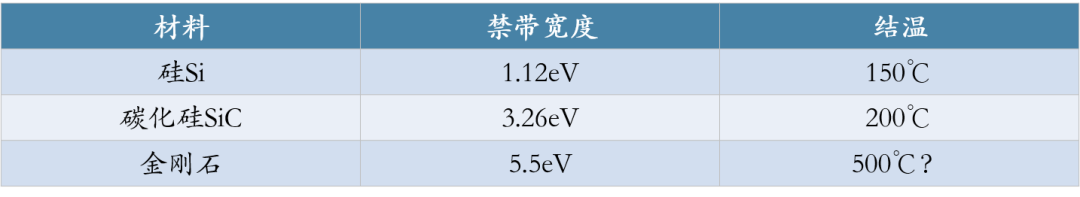

硅的禁带宽度是1.12eV,而碳化硅是3.26eV。所以碳化硅器件比硅器件更耐温,可以到200℃,而硅只能到150℃,传闻金刚石可以工作在500℃。

第三代半导体的特点就是禁带宽度大,所以主要应用于高温,大功率器件场合。

电子/空穴迁移率

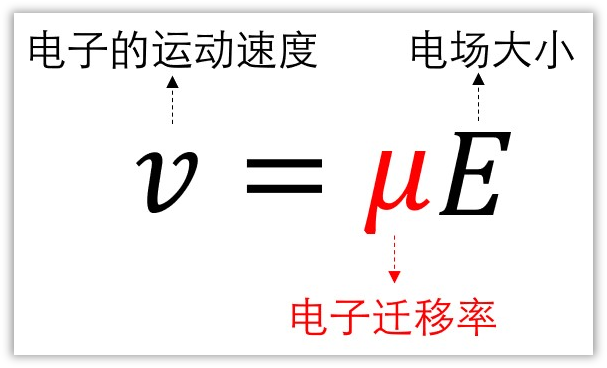

电子迁移率,指的是电子在电场力作用下运动快慢的物理量。

这个不好理解,我们可以这么看。

电子浓度相同的两种半导体材料,在两端施加相同的电压,那个迁移率更大的半导体材料,它里面的电子运动速度越快,单位时间通过的电子数不就越多吗?也就是说,电流越大。

这就说明了电子迁移率越高的半导体材料,电阻率越低,通过相同的电流,损耗越小。

空穴迁移率与电子迁移率一样,空穴迁移率越高,损耗越小。但是一般说来,电子的迁移率是要比空穴要高,因为空穴是电子的空位,空穴的运动,本质上是电子从一个空穴移动到另外一个空穴。

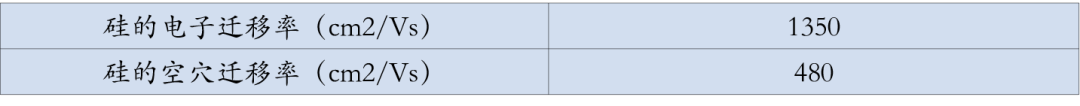

从上表可以看到,硅材料的电子迁移率要比空穴迁移率高几倍,这也是为什么NMOS管比PMOS管用得多的主要原因。

NMOS管在导通时,形成的是N型导电沟道,也就是说用来导电的是电子。而PMOS管导通,形成的是P型导电沟道,用来导电的是空穴。因为电子比空穴的迁移率要高,所以,同体积大小,同掺杂的情况下,NMOS管的损耗要比PMOS管小不少。

除了功耗之外,电子/空穴迁移率还影响什么呢?器件的速度

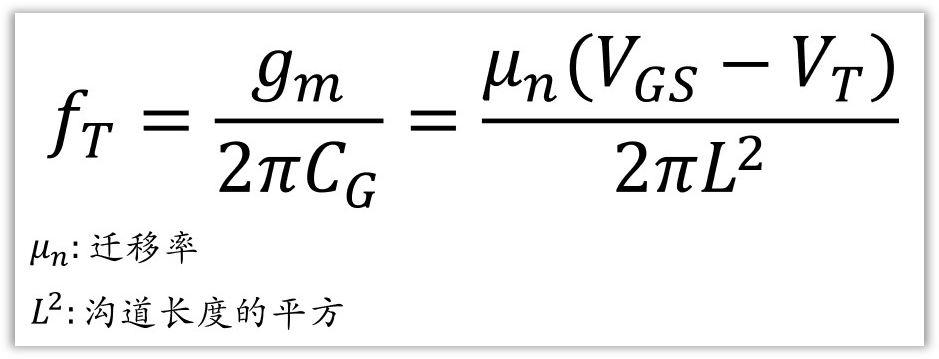

这是NMOS管的截止频率(输入/输出=1时的频率)

从最终的结果可以看到,截止频率与电子迁移率成正比。也就是说,电子迁移率越高,做出的NMOS管可以工作在更高的频率。

这个推导过程挺复杂的,我就不列了。那么有没有通俗的理解呢?

我的想法是这样的,仅供参考。

NMOS管的工作原理,是通过控制导电沟道,以此来控制源漏电流。在栅极加上正电压Vgs,衬底的电子会被带正电的栅极吸引,电子充斥在源端和漏端之间,形成了导电沟道,两边就可以通了。

当Vgs电压以高频率变化的时候,形成的导电沟道的厚薄也会变化。这个导电沟道的变化是通过电子的移动来形成的,电子移动速度越快(电子迁移率越高),那么导电沟道就能更快的响应Vgs的变化。所以说,电子迁移率越高,器件的工作频率越高。

同样的,PMOS管的工作速度,应该与空穴迁移率的大小正相关。

总的来说,电子迁移率越高,晶体管的功耗越小,速度越快。

从表中看出,二代半导体GaAs的电子迁移率是8500,InP的电子迁移率是4600,都是比Si的1350大很多。所以二代半导体的特点就是用在高频,大功率场合。

饱和电子漂移速率

在电场比较低的时候,整体电子的漂移速度与电场大小成正比。当电场大到一定值,电子整体的漂移速度不会再增加,达到饱和,这个速度就叫电子的饱和漂移速率。

这个参数像是决定了电子漂移速率的上限。

具体影响晶体管的什么性能,我也是不清楚。倒是多了个疑问。。。?

除此之外,还有一个问题。。。

欢迎大神们留言区答疑解惑!

结尾

以上就是我最近学习到的,结合自己的理解,分享给大家。没法保证我的理解都对,如有错漏,底下留言区交流,感谢!

暂无评论