凡亿教育-乐乐

凡事用心,一起进步打开APP

公司名片90天全能特训班21期 AD -喜之郎-4DDR

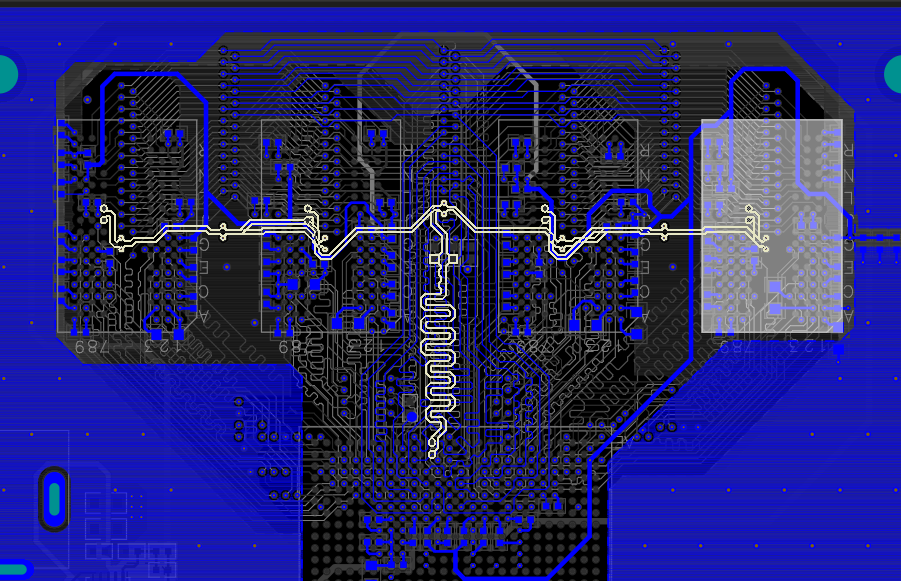

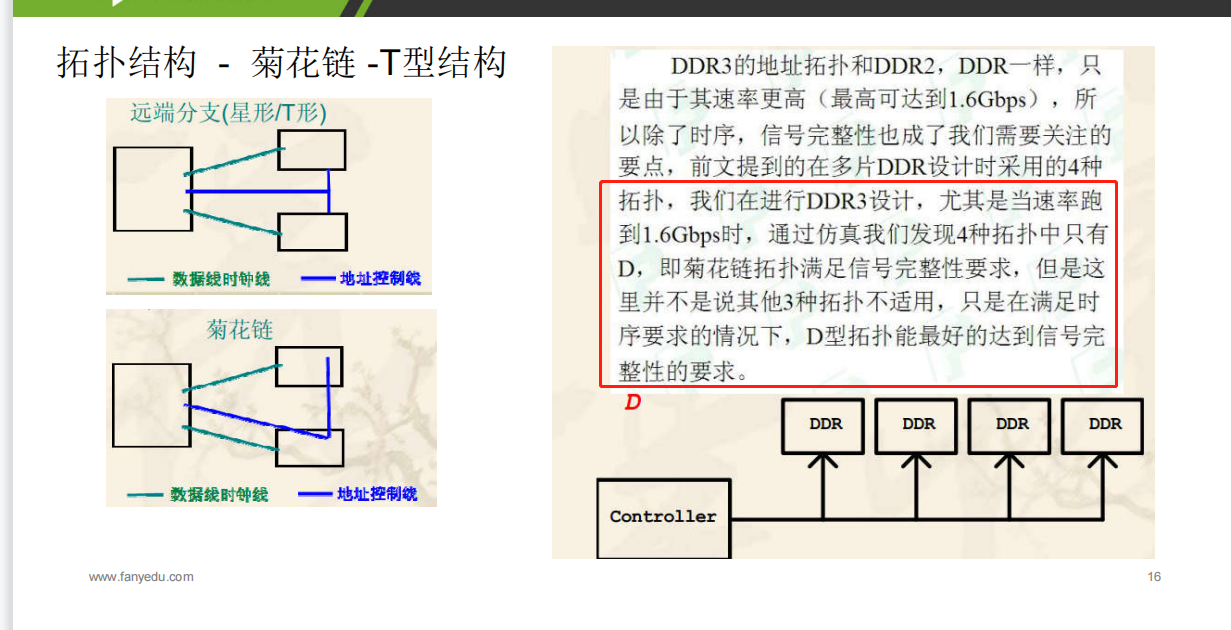

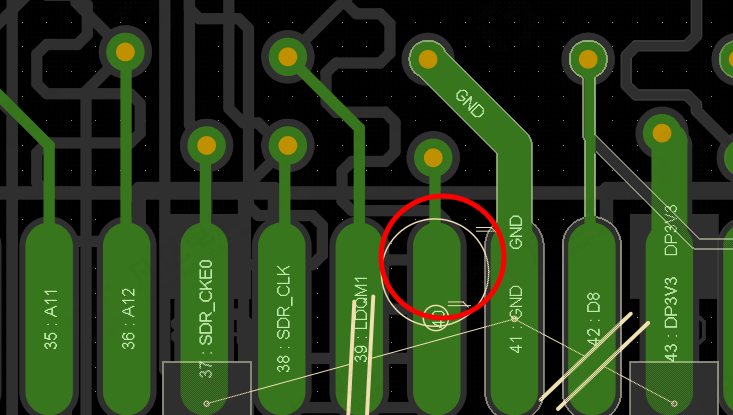

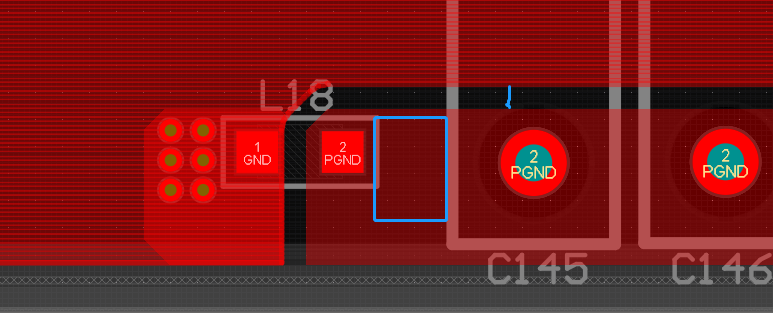

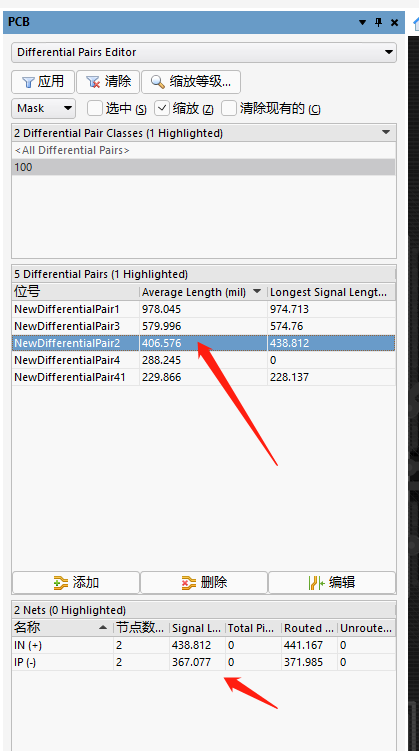

DDR3尽量采用菊花链形式,效果更加

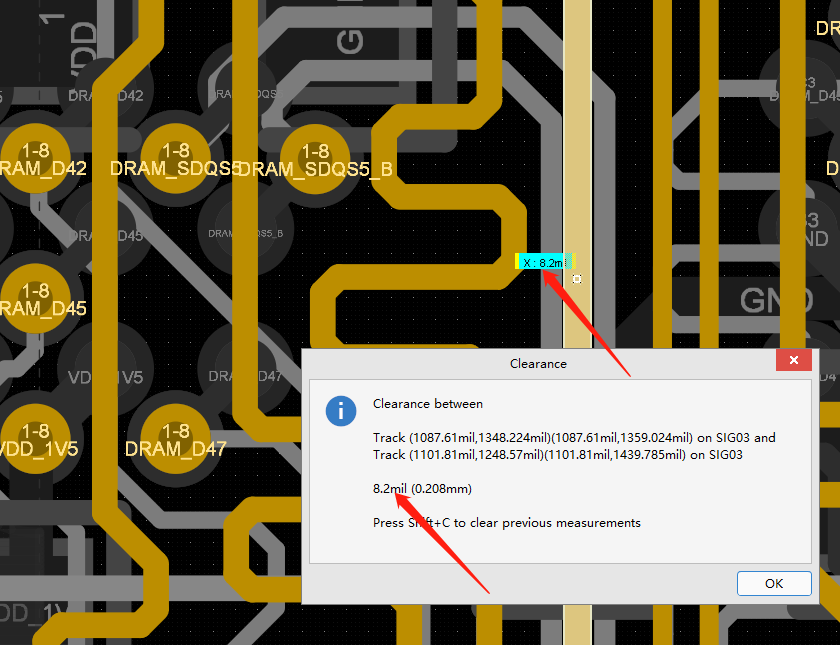

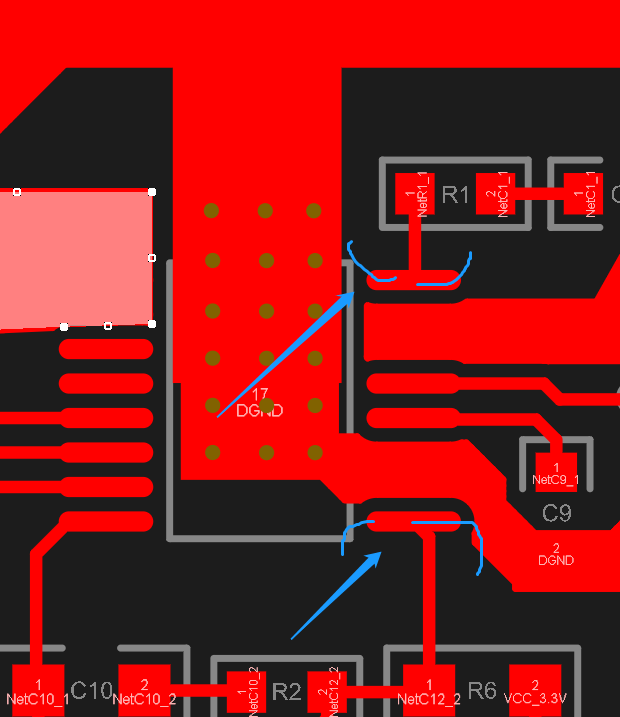

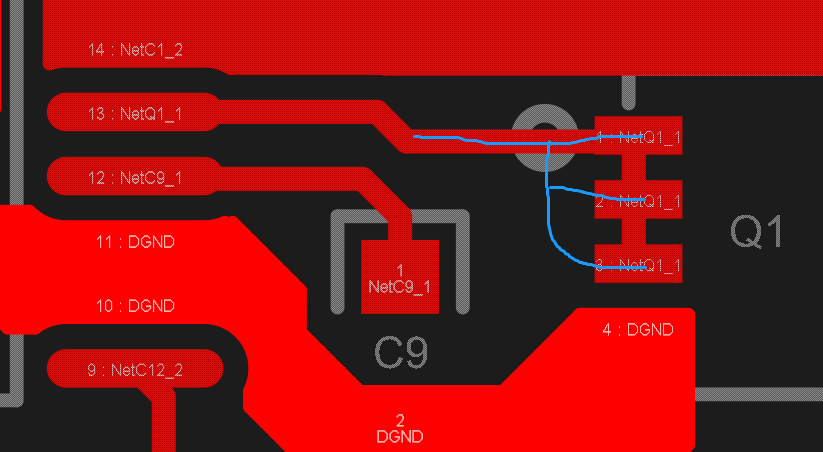

2.注意数据线之间等长需要满足3W间距规则

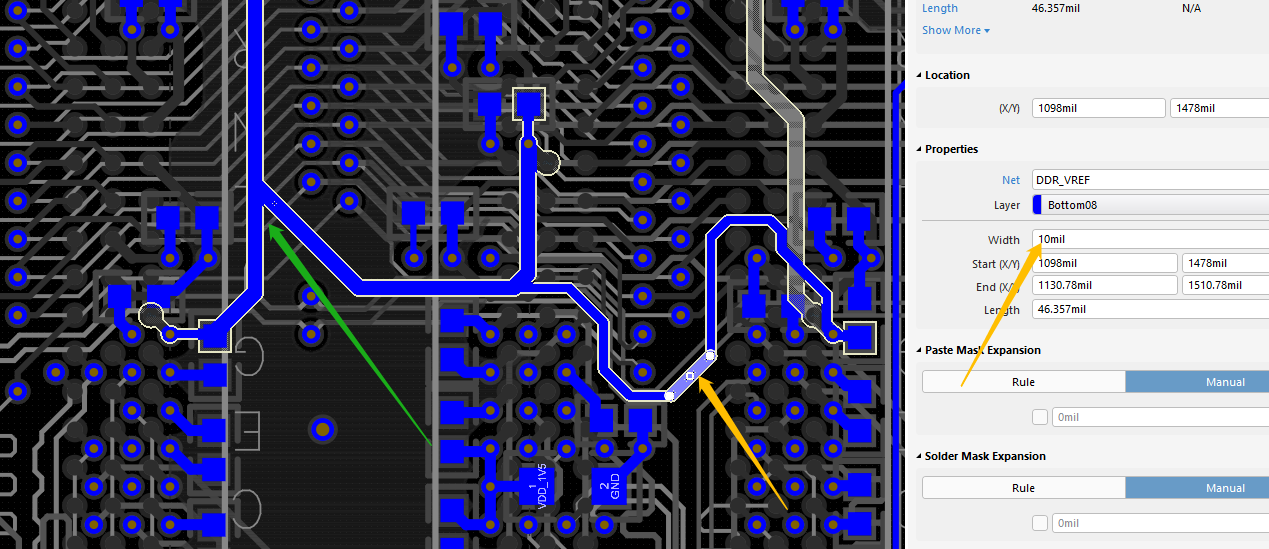

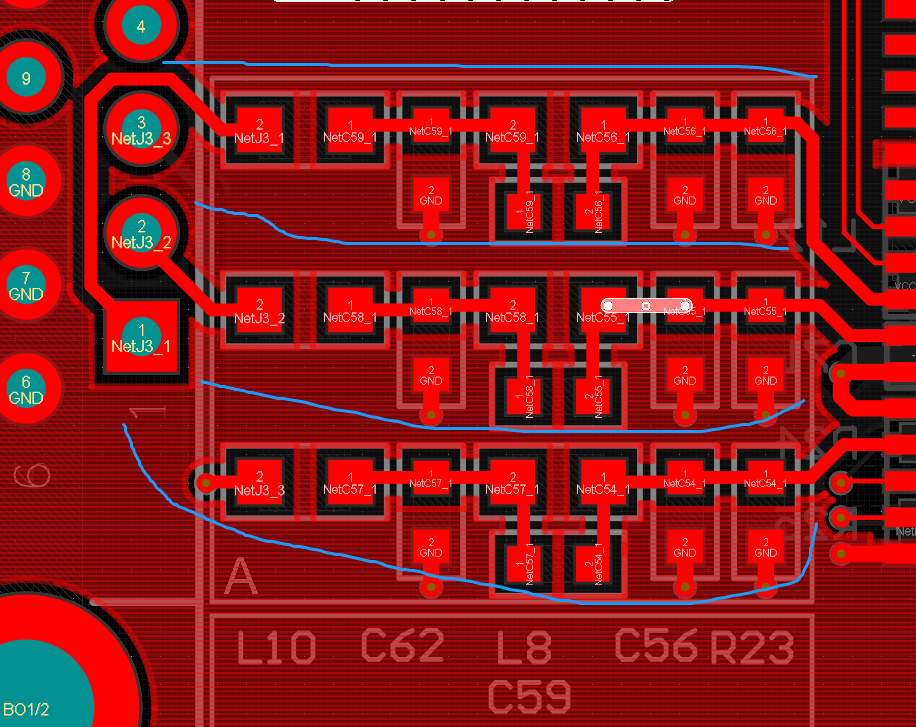

3.注意VREF电源走线需要加粗到15mil以上,尽量不要有锐角

以上评审报告来源于凡亿教育90天高速PCB特训班作业评审

如需了解PCB特训班课程可以访问链接或扫码联系助教:

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表凡亿课堂立场。文章及其配图仅供工程师学习之用,如有内容图片侵权或者其他问题,请联系本站作侵删。

相关阅读

进入分区查看更多精彩内容>

暂无评论