D类功率放大器以高输出功率,高效率,小体积等优点,在车载音响领域异军突起。在数字D类功放刚上电或功放播放状态切换时,人耳偶尔会听到“嘣”的声音,我们把这个爆破的声音称为pop noise。数字功放pop noise 出现的原因有很多,本文主要分析pop noise出现原因,并提供相应解决方法。

Pop noise成因有以下5点:

下面关于5点原因都做一个简单介绍。

1、电容充放电

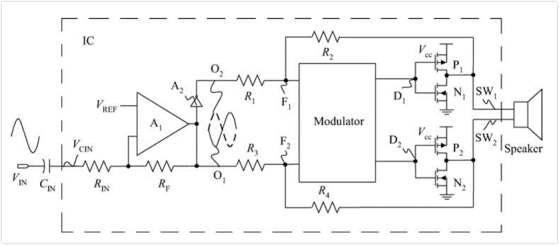

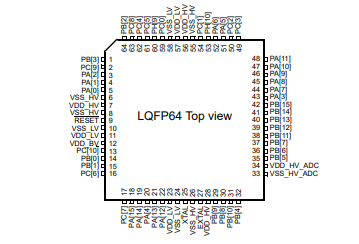

上图所示为单端输入功放,A1是比较放大器,用于设置增益,增强输入信号的负载能力。A2输出同A1输出完全反向。Modulator用于信号调制,将输入的模拟信号与三角波比较,生成PWM波驱动外围MOS。比较放大器A1的一端直连参考电压Vref,另一端通过RIN、CIN连接输入音频信号。

在系统上电时,Vref立刻上升到参考电压值,而A1的另一端则需要通过给RIN、CIN充电,在经一段时间后才能上升到参考电压值。A1两端的电压差经放大后,输出产生pop noise。该场景下可通过降低输入电容值,如换成1uf或0.47uf来实现降低 pop noise。

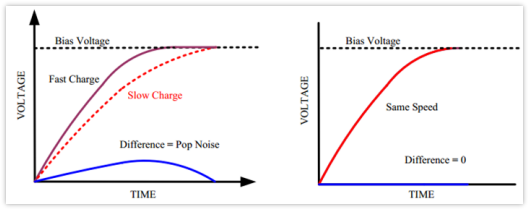

对于差分功放而言,如果P端和N端的输出外围硬件电路不匹配或者输入外围硬件电路不匹配,功放两端输入信号建立时间会不一样,该差分信号差也会输入功放并形成pop音。如下图所示,若A1两端电压上升速度一致,pop noise为0。5ns的信号建立时间差即可产生人耳可听到的pop音。

不同充电速度下的POP Noise

2、PWM启动和暂停

在系统掉电或上电,功放播放状态切换,或输入音源切换时,PWM会产生启停,进而产生瞬态的POP音。如下图所示,在连续PWM动作时,开关频率及其附近的镜像频率都可以顺利的被LC滤波器滤除。而在PWM启停时,开关频率及其奇次谐波会延伸到人耳可听的20-2kHz范围内。该开关频率低于LC滤波器的截止频率,不能被滤除进而产生pop音。

连续PWM及PWM启动的时频域图:

对于BTL结构的功放在进行AD调制时,PWM开启第一个Duty cycle,如果A-side拉低,Bootstrap 电容可以顺利充电,但B-side在此时拉高,这使得Bootstrap电容充电失败。Bootstrap电容提供N MOSFET的充电电压,如Bootstrap电容充电失败,则B-side 第一个PWM不能正常输出。A-side和B-side的不平衡输出会产生明显的POP音。TI针对该类pop noise进行了优化,在AD和BD调制中,都使得第一个PWM为低,进而消除Clock fault。

AD调制PWM开启示意图

3、上下电顺序错误

音频系统有严格的上下电顺序。通常功放的供电电压会比SOC的供电电压高,也比SOC电压建立时间早。为避免pop noise在SOC上电及功放上电时发生,要保持功放为Hi-zi/standby状态,且待功放充分充电后(20ms),再开启PWM波,输入音源。同理在功放断电时,为避免掉电速度不一致,我们需要Mute 并将Standby引脚拉低15ms后再进行掉电。TI 的PurePath Digital 具有优化后的启动序列,这使得可听音频带的pop音尽可能小。

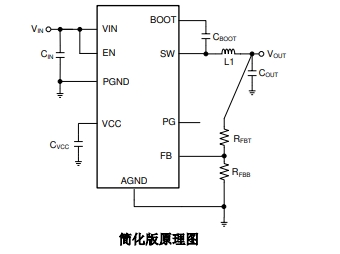

4、PVDD电压/Gain值急速抬升

PVDD电压急剧上升或Gain值急速抬升均会导致pop noise 出现。在进行原理图绘制时,需要将Cstart软启动电容设置在合理的范围内,防止PVDD急速上升。此外,针对某些功放在开机第一次POP noise出现后,还出现了第二次pop noise。这是因为功放在上电后,增益值会以一定步长爬升到设定增益,如果步长设定值过大,会导致pop noise的出现。

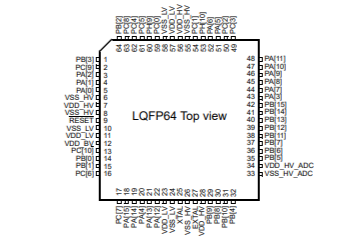

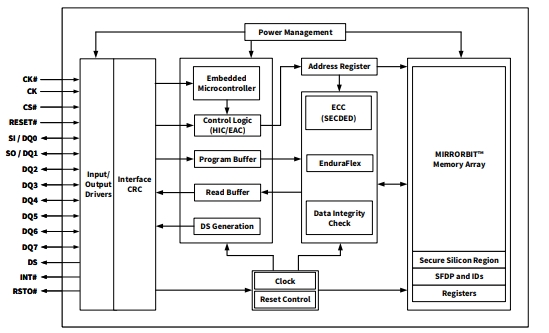

5、Hizi-play 状态切换Clock Fault

如果喇叭不仅仅在开机或者状态转换时出现pop 音,而是当功放从Hi-zi切换到play时,连续出现POP noise,此时应当检查是否出现Clock Fault。以TI的芯片TAS6424L/M-Q1系列为例,硬件工程师可以断开SOC的IIC控制,并将IIC通过USB转接板连接到PPC3进行Clock Fault检验。

若此时出现Clock Fault 应检查输入音频信号I2S/TDM是否满足数据手册的要求(见数据手册Electrical Characteristics 中Serial Audio Port)。此外,数据手册中还有其他特殊情况的说明,以TAS6424L/M-Q1系列为例,如果客户将SCLK和MCLK连接到一起,FSYNC需要为2 MCLK以上。若SOC为高通8155系列,FYSNC输出共有3个选项:第一是2MCLK ,第二是50% duty cycle ,第三为1 slot,我们可以选择后两项作为FSYNC输入。

暂无评论