【摘要】

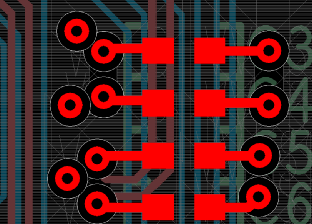

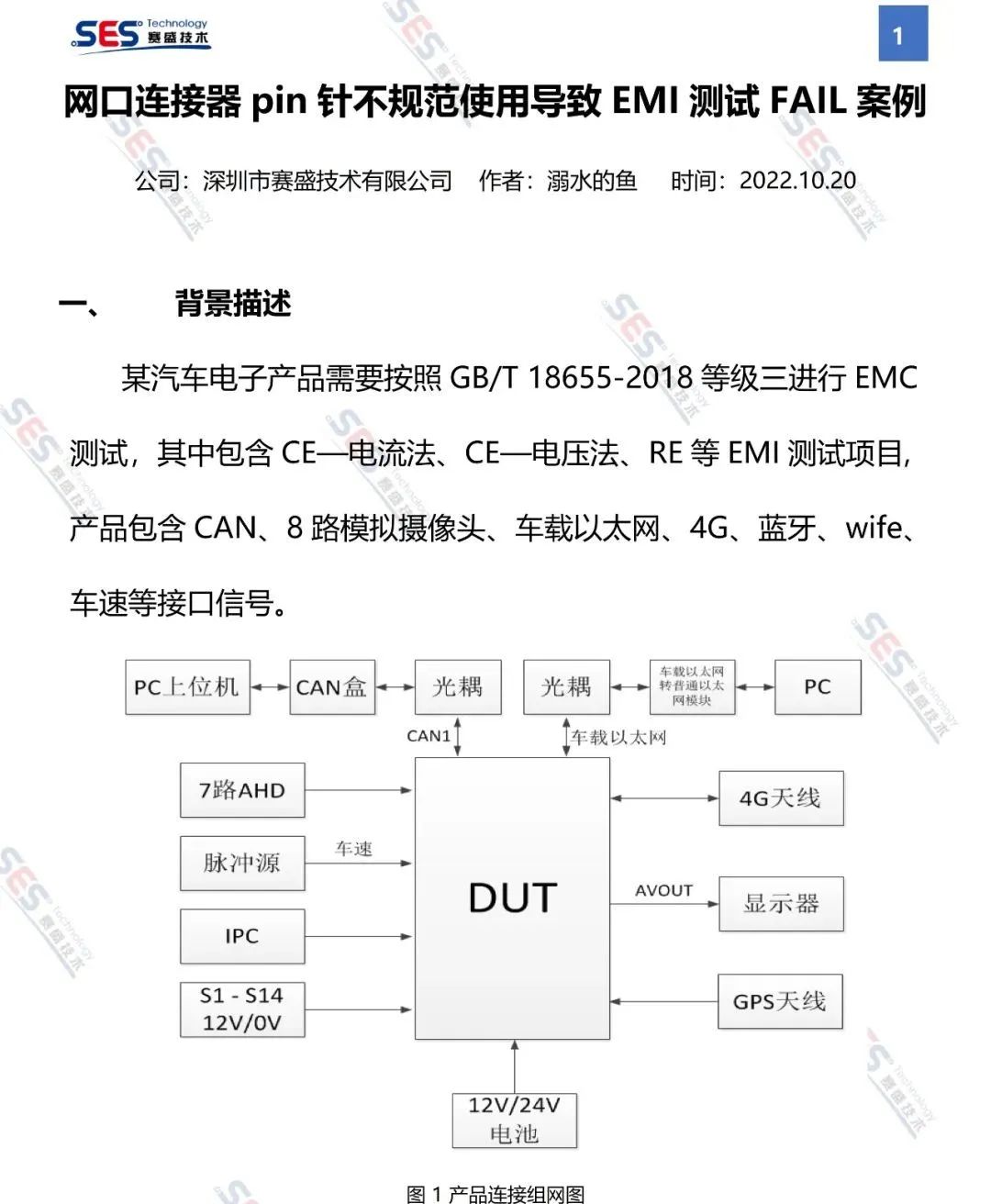

在某单板开发工作中,高速信号线非常多,为了保证单板的EMI性能,在PCB布线中,尽可能保证信号线走内部信号层,防止因为过多表层高速信号线产生的EMC问题无法定位。但是该方案带来的直接问题是高速信号线跃层过多,过孔较多,极大的增加了信号线的插入损耗,影响了信号完整性。在本单板设计中,为了兼顾性能和EMC,采取了反焊盘、电容下方挖地走线等方案改进了性能。一、问题提出 该单板存在多组高速信号线:16路GE,4对5Gbps的QSGMII Serdes,4对2.5Gbps的Flexlink Serdes以及5对125MHZ的差分时钟线,25MHZ,48MHZ,125MHZ单端时钟各一组等,另外还包括16-54路左右的POE供电网络等。考虑到后续的EMC情况,不可控因素非常多,所以为了保险起见,在PCB设计中严格遵照EMC要求来布局布线,并尽可能将高速信号线以距离管脚尽可能短的位置走过孔到内部信号层。这样导致的直接后果是高速信号线经过的过孔较多,插入损耗较大,对于性能方面的影响是显而易见的。 为兼顾EMC性能,高速信号线的过孔较多,尤其是5Gbps的SERDES信号对,一般都经过了4个过孔,根据仿真结果,插入损耗理想情况下最大值达到了-10.4dB,而厂家给的插入损耗阈值仅有-12.5dB,已经非常接近阈值,对于高速信号的数据传送性能造成了极大的隐患。 通过EDA仿真,以及查阅相关资料,目前的优化方案主要有以下三种: Ø反焊盘 ØStub 长度优化 Ø电容下方挖地二、优化方案1. 反焊盘 反焊盘指的是负片中铜皮与焊盘的距离。在高速PCB设计中,较大的反焊盘尺寸和较低的介电常数材料可以减少电容负载,从而可以降低过孔阻抗,减小传输延时。在该单板中,主要针对5Gbps的QSGMII SERDES差分对采用反焊盘处理。本单板使用的反焊盘示例如图2-1所示,

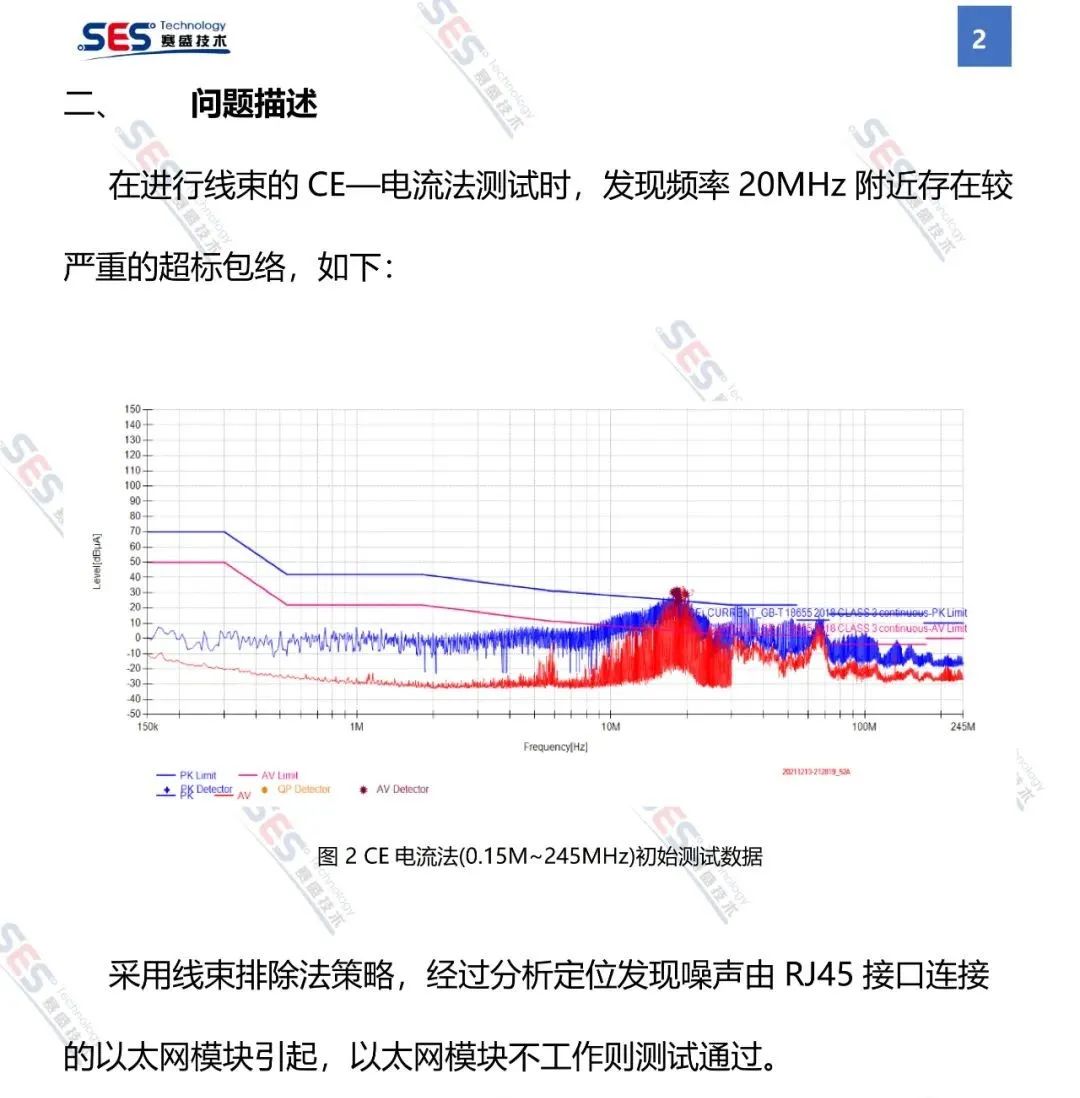

图2-1 反焊盘示例 通过对本板的仿真,采用反焊盘技术效果极为明显,仿真数据如表2-1所示。表2-1 反焊盘插入损耗仿真数据

| Via type | Undo VIA | Round Anti-Pad |

| Frequency | 5GHz | 5GHz |

| Insertion Loss(dB) | -1.4050 | -0.9430 |

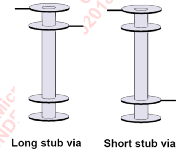

2.STUB长度优化 STUB指残端效应。在PCB设计中,往往为了降低成本,过孔都做成了通孔形式。在此情况下,从信号通过过孔到另一个信号层,往往信号在过孔的中间,过孔还残余一部分,这一部分残端即为STUB。STUB形成了一个天然的天线,它既可以发射信号,也可以接收干扰信号,造成对信号完整性的危害。STUB还会给PCB走线增加特性阻抗,并且减少走线的自身阻抗,对于高速信号线存在任何的stub都是不完美的。如果一个open stub是1/2波长,则其就等效于走线上的一个对地电容;而如果short stub是1/2波长,其相对于在一个走线上加上一个电感。STUB如图2-2所示 图2-2 STUB对比 在实际应用中,尤其是高速信号线的过孔,一般会采用埋孔来消除STUB影响,也有会通过钻孔处理,在单板完成后,将STUB部分挖除。 在本板中,考虑到成本及工艺方法,使用的过孔完全是通孔,所以STUB的问题无法规避,只能在每对差分对的过孔处添加GND孔,降低回流阻抗。

图2-2 STUB对比 在实际应用中,尤其是高速信号线的过孔,一般会采用埋孔来消除STUB影响,也有会通过钻孔处理,在单板完成后,将STUB部分挖除。 在本板中,考虑到成本及工艺方法,使用的过孔完全是通孔,所以STUB的问题无法规避,只能在每对差分对的过孔处添加GND孔,降低回流阻抗。

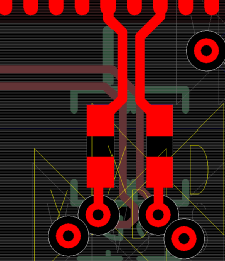

3.电容下方挖空处理 电容下方地平面挖空处理也是一种非常有效的方法,电容挖空主要解决的是电容不连续问题。在高速差分串行布线中,电容不连续是最常见的问题,主要问题是由于PAD和参考平面之间形成的寄生电容。而电容不连续极易产生插入损耗。 减小寄生电容的最常见方式是挖空PAD下方的参考平面,尤其是对于差分对中的AC耦合电容,效果尤其明显。在本次单板的PCB设计中,对于仿真结果最差的差分线执行了电容下方挖空处理。如图2-3所示:

图2-3 电容下方挖空处理 而通过对本单板进行仿真,得到的仿真结果如表2-3所示:表2-3 电容下方挖空仿真结果

| Via type | 未掏空 | 掏空 |

| Frequency | 5GHz | 5GHz |

| Insertion Loss(dB) | -1.2467 | -0.8363 |

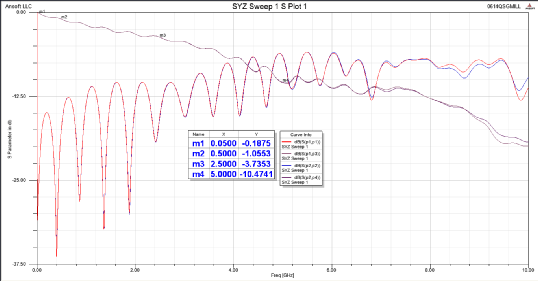

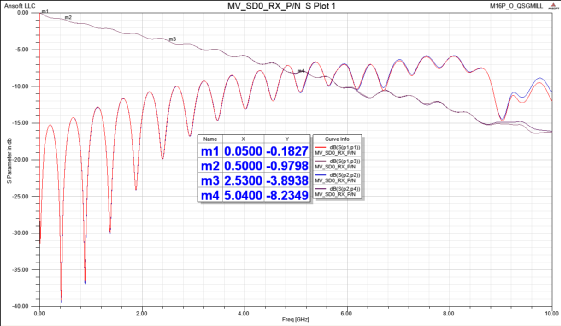

三、仿真结果对比如前所述,考虑到QSGMII接口速率较高,达到了5Gbps,同时有的差分对达到了4个过孔,并且最长走线达到了5000mil,很难保证最终的性能。所以为了保证插入损耗优化,综合采用了反焊盘及电容下挖空处理方案。如图3-1所示,为原始未作任何处理情况下的仿真结果,该仿真对象为走线最差的MV_SD0_RX_P/N差分对,由下图可见,随着频率增加,插入损耗越大,在5GHZ情况下,插入损耗达到了最差的-10.4741dB,与官方提供的阈值-12.5dB已经非常接近了。

图3-1 原始最差路径插入损耗在综合采用了反焊盘,电容下挖空处理以及过孔处打地孔形成回流路径等手段后,得到的仿真结果如图3-2所示:

图3-2 处理后仿真结果 由上图可见,经过处理的走线插入损耗降低到了-8.2349dB,相对处理前降低了2.2392dB,插入损耗降额效果还是比较理想的。四、总结随着通信系统的越来越复杂,速率越来越高,高速信号的各种性能要求会越来越高,遇到的问题也会越来越复杂。本次单板开发中,针对高速信号的插入损耗问题,在PCB布局和布线中,应用反焊盘,电容下方挖空,回流地孔等各种综合解决方案较有效的提高了插入损耗问题。本次实践是对于插入损耗问题的一次有效尝试,对于后续的开发具有一定的实践和借鉴意义。

暂无评论