凡亿教育-乐乐

凡事用心,一起进步打开APP

公司名片Cadence做封装库时要注意些什么?

许多电子工程师会选择Cadence Allegro来设计PCB,在使用时会遇到许多操作,其中之一是在Cadence环境中创建封装库,确保数据的高效与准确,那么在操作Cadence时需要注意什么?

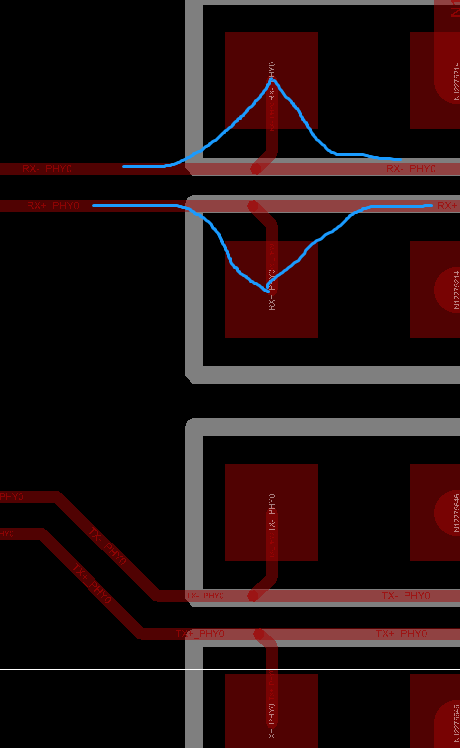

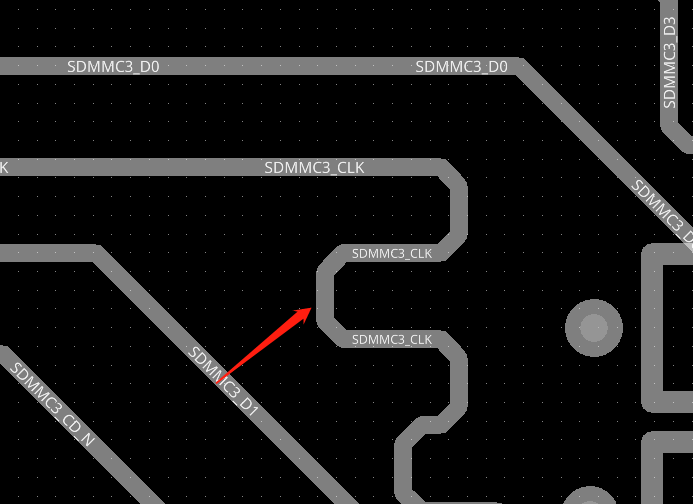

1、精确测量与缩放Pad尺寸

根据Pin脚的精确尺寸,合理设计Pad的width(通常为Pin宽度的1.2~1.5倍)和length(通常额外增加0.45mm左右),确保良好的接触性和电气性能。

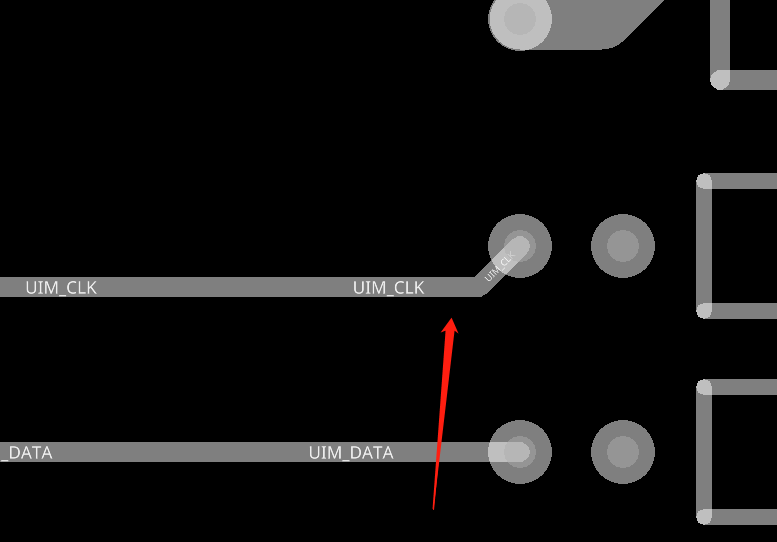

2、层次结构域管理

添加必要的层次,如SilkScreen_top和Bottom层用于丝印标识,确保光绘文件制作的顺利进行。避免丝印层覆盖Pad区域,防止制造混淆。

3、参考设计与标注

在Silkscreen层上标注Ref Des(参考设计)等关键信息,并明确指示1号Pin脚的位置,便于组装和测试过程中的识别与对齐。

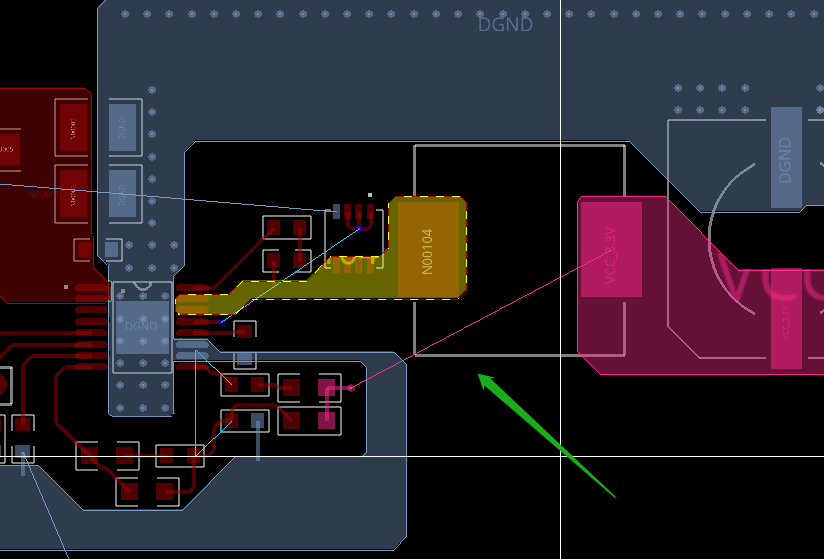

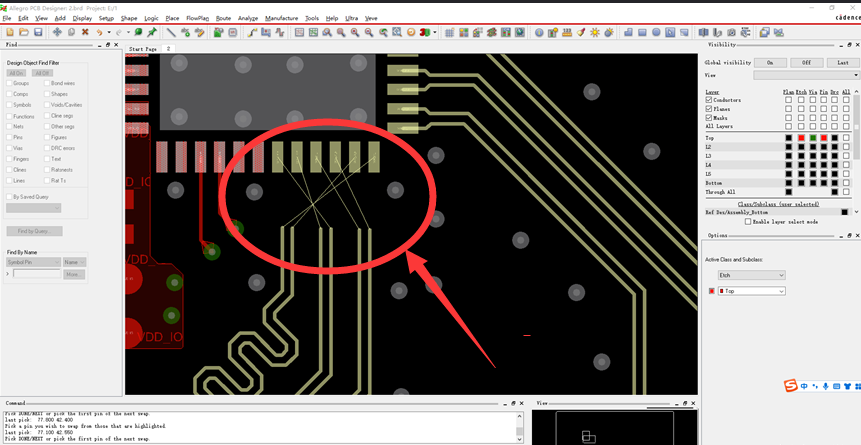

4、特殊封装处理

对于如金手指等特殊封装,根据需求添加Via keep out或Route keep out层,避免不必要的电气连接或布线路径冲突。

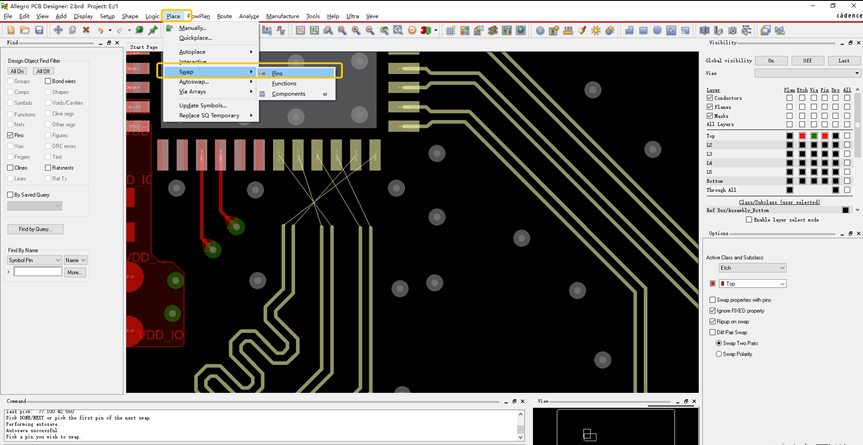

5、创建并保存Symbol

完成封装设计后,务必执行Create symbol操作,生成必要的*.psm文件。这一步是封装能够被Allegro环境正确调用的关键。

6、检查与验证

在最终确定封装前,进行详细的检查与验证,包括尺寸测量、引脚对齐、层间关系等,确保封装符合设计要求及制造标准。

7、版本控制与文档

为封装库建立版本控制系统,并详细记录每个版本的变更说明和适用场景,便于后续维护和升级。

本文凡亿教育原创文章,转载请注明来源!

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表凡亿课堂立场。文章及其配图仅供工程师学习之用,如有内容图片侵权或者其他问题,请联系本站作侵删。

相关阅读

进入分区查看更多精彩内容>

暂无评论