凡亿教育-小辣椒

凡事用心,一起进步打开APP

公司名片DSP系统的硬件降噪技术是如何实现的?

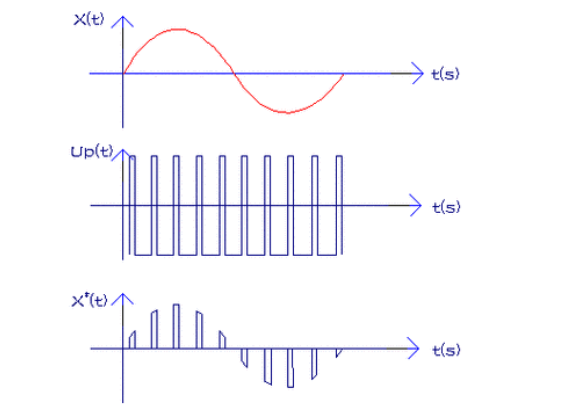

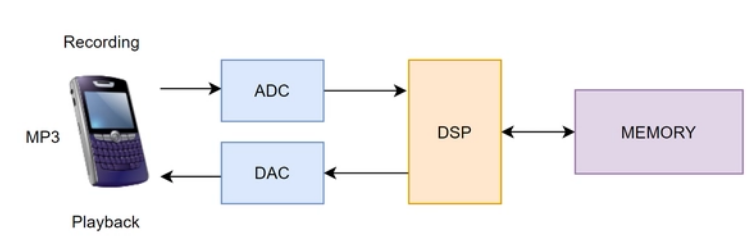

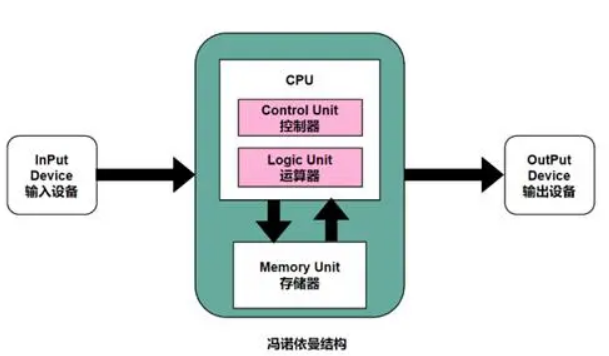

在数字信号处理(DSP)系统中,经常有噪声问题,为了确保信号质量,提高系统性能,很多工程师会选择硬件降噪技术来降噪。那么你知道这个硬件降噪如何实现的吗?

1、板结构域线路布局优化

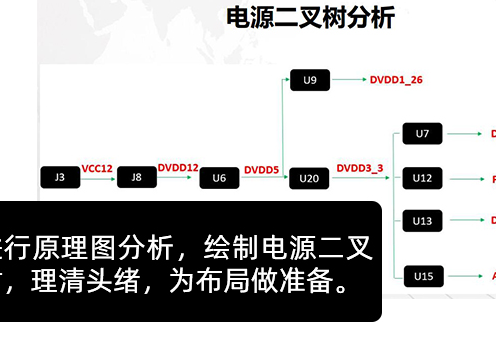

采用大面积地与电源平板:确保电源去耦的低阻抗路径。

窄线条设计:使用4到8密耳线条,增强高频阻尼,减少电容耦合。

分区布局:数字、模拟、接收、发送地/电源线严格分开,按频率和类型分隔电路。

避免PCB切痕:减少不希望的环路产生。

叠层结构设计:控制阻抗,形成稳定传输线结构,密封电源与地板层间线迹。

最小化环路面积:尤其是时钟信号,减少电磁辐射。

高速线路直连:缩短且直接连接,减少噪声耦合。

避免并行高噪声线迹:敏感线迹与高速开关信号线保持距离。

无浮空数字输入:防止不必要的开关噪声。

平行布线:电源、地、信号线平行布置,消除噪声。

2、滤波技术应用

高频低电感电容去耦:每个IC引脚处使用适当容量的陶瓷电容(如14MHz用0.1uF,>15MHz用0.01uF)。

模拟电路旁路:所有电源和基准电压引脚均需旁路。

快速开关器件旁路:减少开关噪声。

多级滤波:衰减多频段电源噪声。

晶振嵌入并接地:减少辐射和耦合。

局部屏蔽:在关键区域或高噪声源周围加屏蔽。

邻近地线布局:增强电场屏蔽效果。

去耦线驱动器/接收器:紧邻I/O接口放置,降低耦合和辐射。

屏蔽与绞合引线:对干扰引线进行处理,消除PCB上耦合。

感性负载保护:加箝位二极管,抑制瞬态电压。

本文凡亿教育原创文章,转载请注明来源!

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表凡亿课堂立场。文章及其配图仅供工程师学习之用,如有内容图片侵权或者其他问题,请联系本站作侵删。

相关阅读

进入分区查看更多精彩内容>

暂无评论