DDR布线技术的重要性

在如今的印刷电路板设计中,双数据速率(DDR)存储器非常普遍。许多设计都会用到DDR存储器配置的不同版本,这需要在布局中使用特定的布线模式。DDR的名称来源于其能够在每个时钟周期内发送和接收两次信号,是原先的单数据速率(SDR)存储器速率的两倍。由于速率增加了一倍,必须在布设DDR存储器的走线时保持更严格的参数,以满足性能规范。

存储器电路设计的关键在于满足其时序规范。每个信号都有时间要求,以便于对应的时钟信号在上升沿和下降沿对其采样。由于数据速率在DDR存储器的每次新迭代中得到提高,时序余裕将变得更窄。这里就需要精确的布线模式来满足时序要求。

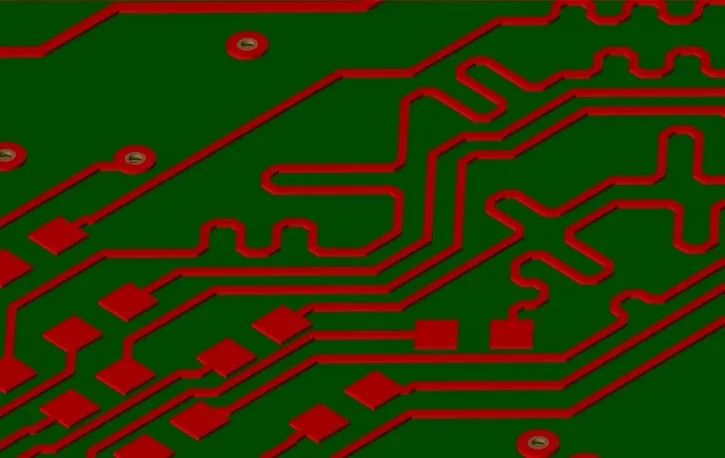

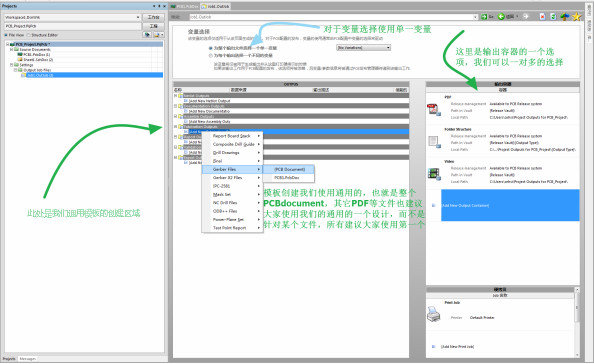

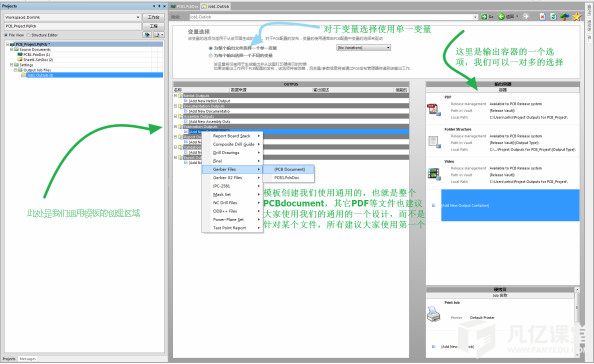

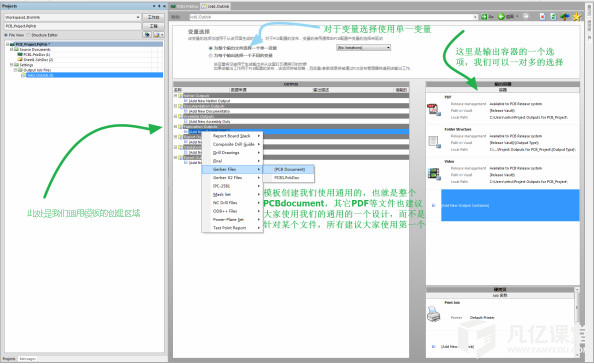

当为匹配长度而调整DDR布线时,像这样的蛇形布线方式非常重要。

走线布设

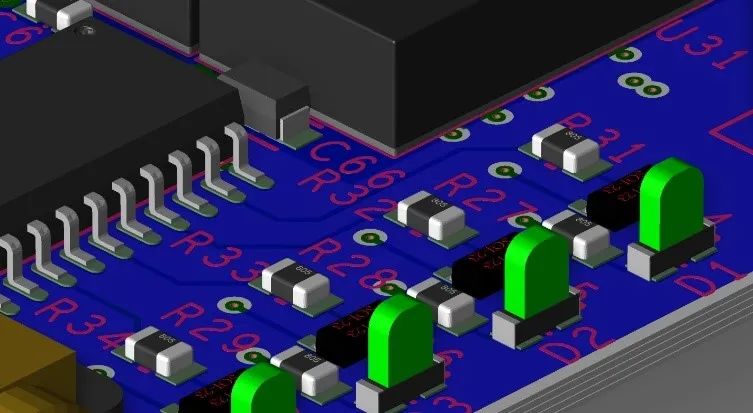

在对DDR进行布线之前,我们仍然需要在布局中遵循高速设计的基本原则。这些原则包括放置器件以重建原理图上规定的信号路径,以及将高速敏感电路与其他可能造成干扰的电路保持隔离。我们还需要在布局中为DDR布线通道和引脚出线留出足够的空间。同时,需要将存储芯片放在一起,并从最低位置的数据位芯片开始,到最高位置的数据位芯片结束,依次进行定位。

在设计DDR时需要注意的另一个布局方面是设计电源分配网络。参考电压在存储器布线的信号完整性方面起到非常关键的作用。参考电压有误会导致错误触发信号,因此需要进行适当滤波以保持其指定的电平。这意味着使用旁路电容器来稳定电源网络,这将在布局中占据其他空间。

DDR电路的布线考虑因素

如前文所说,DDR电路的关键点在于时序。这意味着时钟线将决定存储芯片中数据线的输入时序和输出时序。由于无法对电信号进行加速,因此控制时序的唯一方法是延长走线,以延迟时钟信号的到达。这是通过在布设走线时增加蛇形布设方式来实现的。通过调整时钟信号的到达时间,我们可以对数据线作出类似的调整,从而每位数据都可以在下一时钟周期之前到达并实现稳定。

在对DDR电路进行布线时,通常使用两种不同的布线方法——T型拓扑和Fly-by拓扑:

T型拓扑方法以分支的方式将命令、地址和时钟信号从控制器连接到存储器模块,而数据线则直接连接。这种方法最初在DDR2中使用,但无法适用于具有更高信号速率的DDR3和DDR4。分支对布线来说是一个挑战,但具有能够处理多晶粒组件的高电容负载的优势。

Fly-by拓扑布线方法更像是菊花链拓扑方法,它以链的形式将命令、地址和时钟信号从控制器连接到存储器模块。同样,数据线直接通过控制器和存储器模块连接。该方法通过减少T型拓扑中走线的短截线数量来支持在更高频率下进行操作,这也提高了其信号的完整性。Fly-by拓扑的菊花链结构也比T型拓扑的分支结构更易于进行布线。

同时对所有这些线路进行计时的关键是在布线过程中调整和匹配走线的长度。只有满足时序规范,才能按预期布设DDR的走线。我们可以在数据手册中找到这些规范要求,并应设置高速设计约束来满足这些长度规范。

另一项重要因素是,在电路板的哪一层布线也会影响布线。在内层布线(带状线)和在外层布线(微带)有着不同的性能特征,会影响信号的速度。不能简单地匹配内层和外层上走线的调整。同时,必须对这些走线进行调整,以考虑到不同的层特征。此外,鉴于信号计时随着每个新版本DDR的出现而变得越来越关键,需要在匹配的信号路径总长中考虑到整个飞行时间(TOF)。这意味着还要将内部封装引线的尺寸纳入到走线长度的计算中。

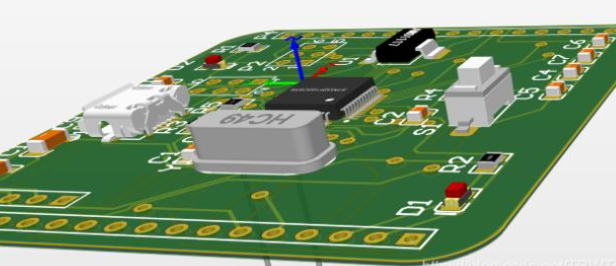

Cadence Allegro等高级PCB设计工具可以让复杂布局变得轻松简单。

未来就在眼前

我们已经看到了DDR存储器的能力和PCB走线布线支持在这些年里稳步发展到目前的DDR4技术水平。现在,我们即将通过DDR5进入到存储器发展的下个阶段。随着DDR5的基本速率达到DDR4的两倍,布线规范可能会更加严格。为了掌握这项先进技术,PCB设计工程师需要布局工具来应对即将遇到的新挑战。设计工程师们将需要DDR布线的流程规划能力,以及内置于在PCB设计工具中的先进走线长度匹配和调整能力。

Cadence公司的PCB设计工具可以为您提供在设计这些先进DDR布线方法时所需的能力和性能。Allegro® PCB Designer工具提供了约束驱动流程,可以简化DDR布线拓扑的设置,让复杂布局变得轻松简单。

暂无评论