凡亿教育-佳佳

凡事用心,一起进步打开APP

公司名片 做原理图最怕遇见哪些问题?盘点一下吧!

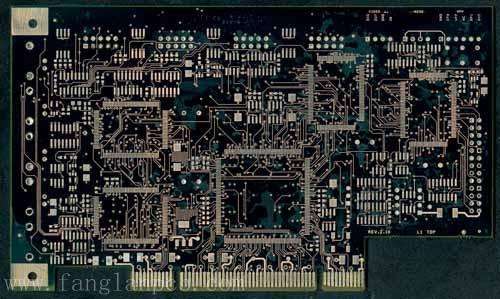

原理图作为电子设计的基础与核心,其准确性与完整性将直接关系到后续PCB布局布线,甚至整个产品的性能与可靠性,但电子小白在设计原理图时会遇见各种各样的问题,今天我们来盘点下有哪些问题是最怕遇见的!

1、ERC报告管脚未接入信号

管脚I/O属性定义错误:创建元件封装时,错误地为某些管脚分配了I/O属性,而实际上它们可能应为电源、地或其他非信号引脚。

连接不上问题:由于网格设置不一致或连线精度问题,导致元件管脚与导线看似相连实则未接通。

引脚方向错误:创建元件时,未注意引脚方向,使得必须连接的引脚端未暴露在外,增加了连线的难度和出错率。

2、元件位置偏移图纸边界

元件创建位置不当:在元件库中创建元件时,没有将其置于图表纸的中心,导致在原理图绘制过程中,元件容易跑出图纸边界,影响查看和编辑。

3、网络表导入PCB问题

Netlist生成选项错误:在生成网络表(netlist)时,未选择全局(global)选项,导致生成的网络表只能部分或错误地导入到PCB设计软件中,影响板级设计的准确性。

4、多部分元件使用不当

避免使用Annotate:当使用自定义的多部分(如符合器件)元件时,应避免使用Annotate功能进行编号,因为这可能导致元件内部的连接关系被打乱,影响原理图与PCB之间的一致性。

本文凡亿教育原创文章,转载请注明来源!

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表凡亿课堂立场。文章及其配图仅供工程师学习之用,如有内容图片侵权或者其他问题,请联系本站作侵删。

相关阅读

进入分区查看更多精彩内容>

暂无评论