PCB(Printed Circuit Board),即印刷电路板,其按照导体层数分类,可以分为只有一面覆铜的单面板,两面都有覆铜的双面板,以及具有多个铜层的多层板。

多层PCB通常由多个双面覆有铜箔的覆铜芯板(Core)与半固化片(prepreg,简称PP)一起按需组合叠层,然后在最外层加上铜箔并加热加压进行压合形成具有多个铜层的多层板,多层板按导电层数分又可以进一步细为4层板、6层板、8层板…以此按偶数层类推。

您会发现一个规律,貌似多层板都是具有偶数层的,这是因为PCB的叠层需要保持对称性,以避免PCB在加工过程中因应力不平衡而发生严重的曲翘变形,造成PCB的报废。

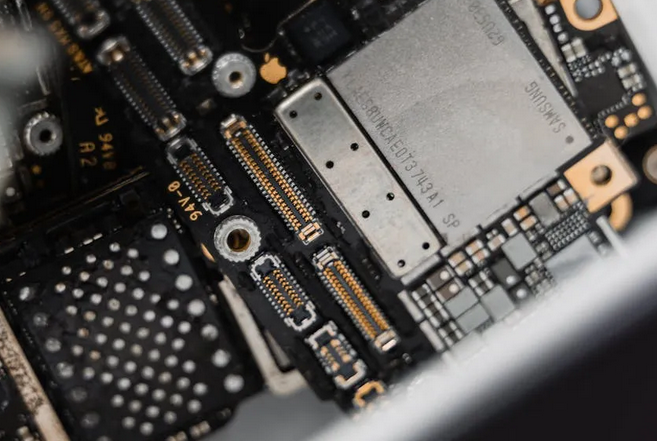

PCB最初是作为容纳电子元件的载体来使用的,并通过蚀刻PCB上的铜箔形成元器件间的互联电路来替代人工焊线的互联方式,从而提升电子产品的生产效率以及可靠性。

在1971 年 英特尔(Intel)公司研制出第一个微处理器 4004之后,集成电路(Integrated Circuit,IC)便朝着大规模集成电路(Large Scale Integration LSI)及超大规模集成电路(Very Large Scale Integration VLSI)的方向发展,随着处理的数据量不断增大,电子元器件间互联信号的传输速率也必须相应提高,同时,IC的封装也需要符合高密度的发展趋势,1970年代,球栅阵列封装(BGA)开始出现。

随着高密度IC封装的发展,以及电子元器件间信号传输速率的提升,都使得PCB不再是简单地充当电子元器件的载体而已,PCB已经演化为具有多个线路层的“多层系统”。

老wu这里指的“多层系统”,它与多层板有什么区别吗,这里强调的这个“多层系统”它当然是多层板,但又不仅仅是比单面板或者双面的多了几个布线层而已,增加布线层以实现把互连线走通是需要考虑的一个方面,但为了满足具有特性阻抗要求的传输线结构,还要仔细考虑不同的叠层设计,为了满足电源目标阻抗的要求,需要利用电源/地平面组成的平板电容,为了抑制EMI,需要考虑把高速信号线在PCB内层布线,这需要多层板的设计来实现。

随着信号速率的进一步提升,关于PCB的这个“多层系统”需要考虑的因素就更多了,比如趋肤效应造成的损耗,要考虑铜箔粗糙度的问题,板材极化造成的损耗,要考虑采用低DK的板材等等,这就需要仔细设计叠层结构以及选用性能合适的板材以满足要求。

1.多层板的常用叠构介绍

刚性PCB通常由三种基本材料组成,分别是编织玻璃布、树脂和铜箔。

编织玻璃布的编织方式很像用于制作衣服的布。

它们有各种各样的样式,从薄到厚有不同的规格,如:

树脂的种类繁多,从简单的环氧树脂到非常复杂的有机化合物,如聚苯醚树酯。这些树脂用于浸透玻璃布,形成结构稳定的芯板,也可以形成半固化状态的粘结片(又称半固化片,Prepreg,PP),PP在多层板中的作用类似于胶水,在多层板的压合过程中,在高温条件下,半固化片的树脂将重新呈现可流动状态并继续发生聚合反应,实现多个芯板或者芯板与外层铜箔之间的粘结。

多层印刷电路板中的各层具有多种功能。其中一些是包含传输线的信号层,另一些层是用于电源/地平面层。电源/地平面的另一个作用是创建一个具有非常低寄生电感的平板电容器,以支持逻辑IC非常快的开关瞬变,同时,在满足所有这些机械和电气性能要求之后,叠层还必须满足板厂的可制造性要求。

对于高层数的PCB或者高速传输线的PCB,我们总是希望用薄一些的PP,特别是高层数的PCB,有多个PP层,PP层越薄,在PCB总厚度一定的情况下,就可以组合更多的覆铜芯板,实现更多的铜层。

但PP也不能无限制地变薄,IPC-4101规则中,可提供的PP厚度最薄为106编织风格,其树脂含量为71%~72% ,厚度为2mil。在叠层设计时考虑采用最薄PP厚度时,还需要考虑额外的限制因数,首先要考虑的是不同极性电路层之间的最小击穿电压。基于环氧或酚醛树脂的层压板的击穿电压至少为每密耳厚度1000伏,而PP最小厚度为2 mil,对于包含逻辑电路的常规产品中,击穿电压要求为DC 1500伏或更低,所以即使选用的最薄厚度的PP片,也可以满足电气强度要求。

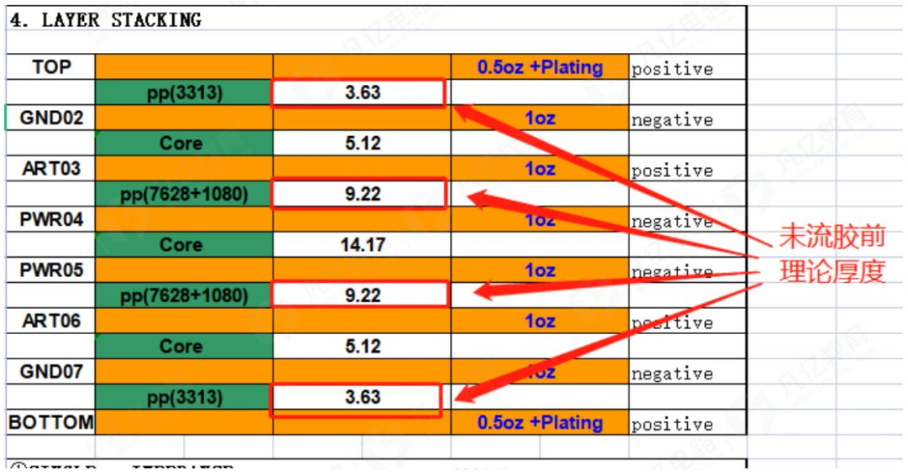

另一个需要考虑的是PP树脂的流动后造成厚度不足,在层压过程中,PP中重新熔化的树脂会流动填充到被蚀刻掉的铜箔空隙中,最终压合后PP的厚度会减小,如果选择的PP厚度过薄,则可能导致不同铜层间出现短路故障。从经验上来看,PP的初始厚度必须至少为3 mil,才能避免这种风险,所以叠层的时候,需要避免单张使用106 的PP,以避免流胶之后PP层厚度不足出现短路故障。

PP片玻璃布编织风格的影响

在设计10Gbps 以上速率的高速互联差分线线时需要注意玻纤效应的影响,上文有提到,刚性PCB的基材通常由树脂以及编织玻璃布交联形成稳定的物理结构。

但树脂的介电常数与玻璃的介电常数不一致,如下图所示,1080编织风格的PP,玻璃纤维之间的编织会形成一个空窗,在与树脂交联的时候,这个空窗区域会被树脂填充,这就造成了信号传输过程中阻抗不一致的情况,会对高数据速率差分信号造成不利影响。

所以,当为10Gbs或更高的数据速率差分线设计叠层时,要避免单独使用106、1080和7628编织风格的PP,可以考虑混合两张不同编织风格的PP,或者使用1067和1086这种新的“扁平化“编织风格的PP。

选择合适的铜箔厚度

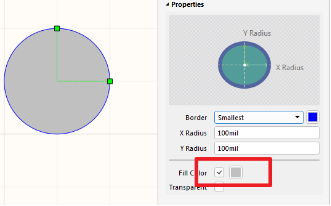

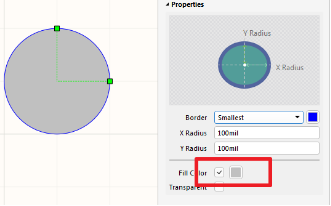

铜箔被用作印刷电路板的导电层,刚性PCB中最常使用的铜箔为电解铜箔(ED铜箔),ED铜箔的制造,首先是将铜原料或废铜线溶解于硫酸溶液中,然后在净化后的硫酸铜/硫酸溶液中,将铜电镀到由不锈钢或钛制作的圆柱形滚筒上。这种工艺产生的铜箔一面相对平滑、 有光泽,另一面较粗糙、无光泽,如下图所示:

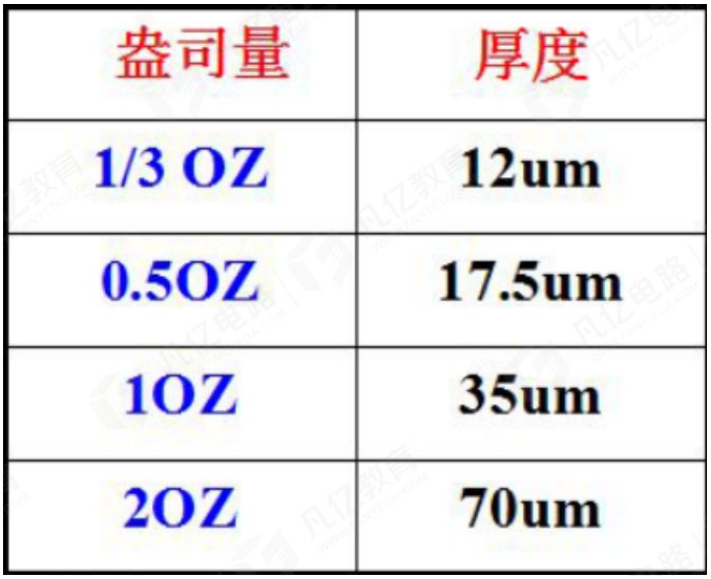

覆铜板上常见的铜厚为0.5盎司、1盎司和2盎司。1盎司约为0.035mm(1.4 mil),但IPC标准里允许板材厂商的覆铜板的厚度有±10%的公差,居于能省一点铜就多一点利润的原则 ,基本上都是负公差,也就是板厂收到的初始板材的铜箔厚度1盎司是低于0.035mm(1.4 mil)的,而且,覆铜板在PCB板厂的工艺过程中,铜箔的预处理之后,还会再减少了 6 微米(0.236 mil)。

铜箔在PCB中有两种用途。一是形成电源/地平面层,另一种是形成信号层。叠层设计时必须平衡铜箔的厚度,使铜的厚度一方面足够厚,以满足载流要求,另一方面又需要足够薄,以满足精确的蚀刻控制,对于信号层的铜厚来说,较小的线宽/线距要求,则需要选择尽可能薄的铜厚。

对于高速信号传输线来说,由于趋肤效应的影响,电流只在铜箔表面附近流动,所以,对于高速信号传输线来说,使用更厚的铜箔并不会带来更好的性能,也就是说,在信号层中使用厚度超过0.5盎司的铜并不能提高信号完整性,反倒是会造成蚀刻的问题。

所以,内层铜厚通常为HOz,也即0.5盎司。

3. 计算阻抗

有几种方法可以计算PCB中传输线的阻抗。其中包括一些在特定条件下适用的计算公式,这些公式允许使用简单的数学运算,在特定条件下的计算结果可以满足±10%的阻抗公差要求,另外还可以使用各种商用软件工具进行计算,这些工具通过求解麦克斯韦方程来精确计算任意形状的传输线阻抗。

基于公式的方法,简单易上手,而且还是免费的,基于场求解器的商用软件工具,功能强大,适用范围广,但要掌握软件的使用方法学习成本高,更重要的是,商用软件的授权费用偏高。

暂无评论