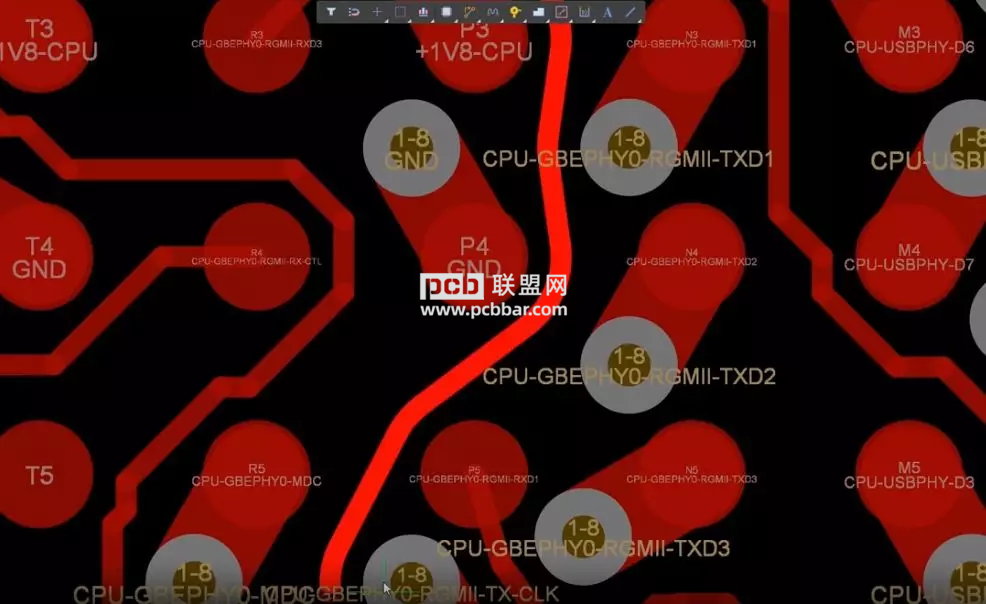

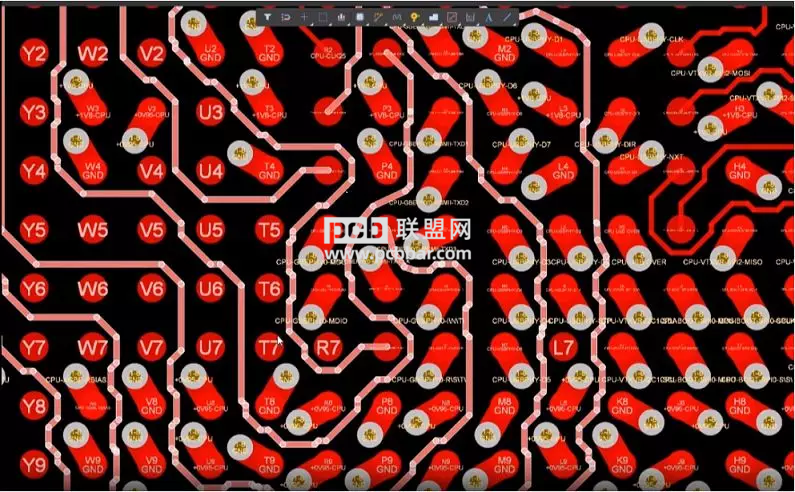

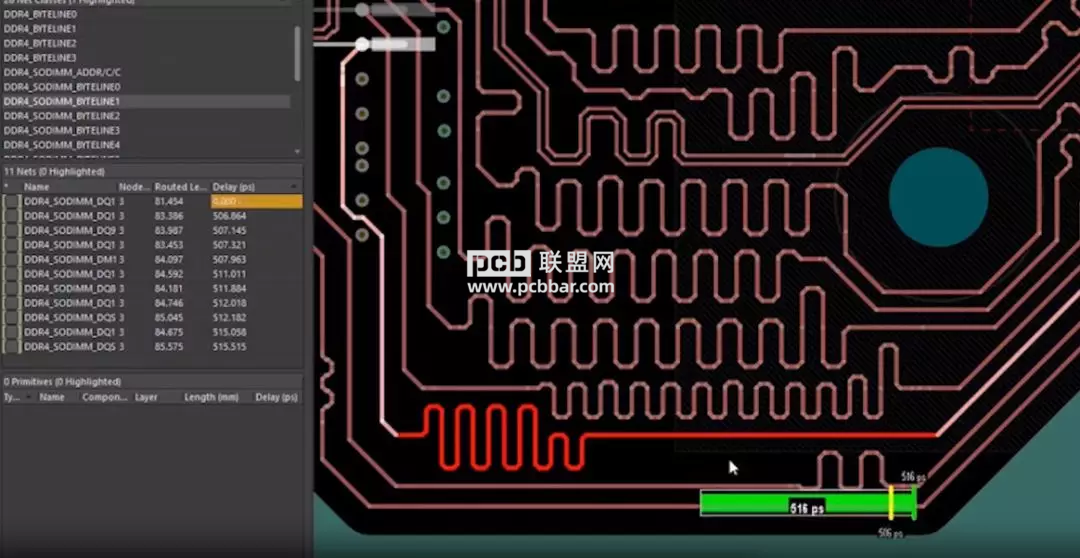

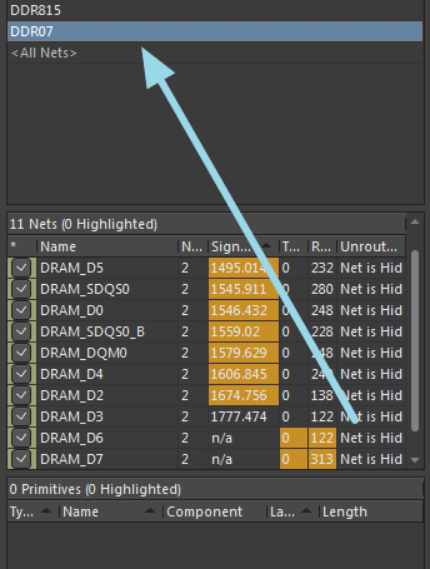

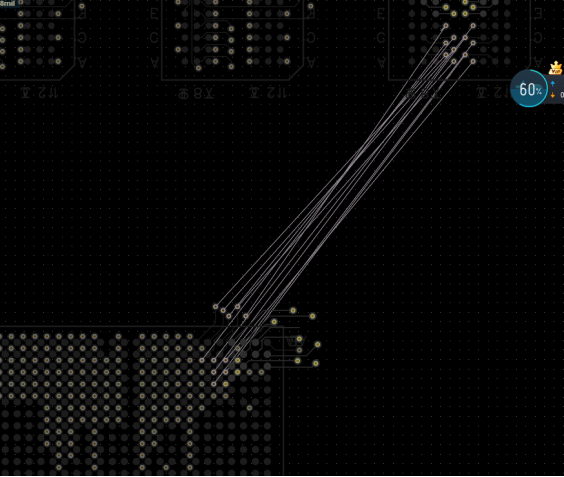

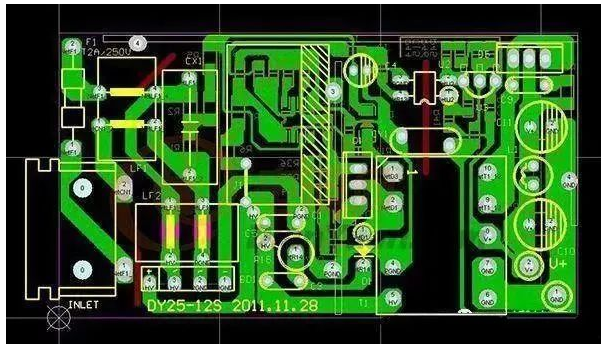

| Altium designer 20已就绪,AD20新功能详解 据美通社消息,2019年12月3日,Altium正式推出了新版pcb设计软件 ——Altium Designer 20。 据悉新的版本将进一步节省布线时间。“Altium Designer 20 改变了PCB设计”,Altium首席技术官Sergey Kostinsky说:“此版本的高级功能使得任何类型,无论是简单还是复杂的电路板设计都变得更加有效率。” 官方也对更多的升级细节做出了解释,为大家罗列Altium Designer 20 的新功能。  任意角度布线 在高密度板上绕开障碍物进行专业操作,并且深入到您的BGA中走线,从而无需额外的信号层。借助智能避障算法,您可以使用切向弧避开障碍物,从而最有效地利用您的电路板空间。    如上图正在走的这根高亮红色线,它从BGA密集的管脚阵列中左冲右突,游刃有余,就像赵子龙在长坂坡七进七出救少主,如入无人之境! 就是这么任性! 不光走线的过程中可以任性地以任意角度走线,自动使用切线和弧线在走线过程中遵守规则保持安全间距,对于之前已经走好的折来折去不够机动灵活的走线可以一键修正。如下图。  先将之前走好需要修整的线选中,然后点一下命令,结果如下图,超赞!  走线的平滑处理 对走线进行编辑以改善信号完整性是很耗费时间的,尤其是当您必须对单个弧线以及蛇形调整线进行编辑的时候。 这就是为什么Altium Designer 20合并了新的布线优化引擎和高级的推挤功能以帮助加快该过程,从而提高生产率的原因。

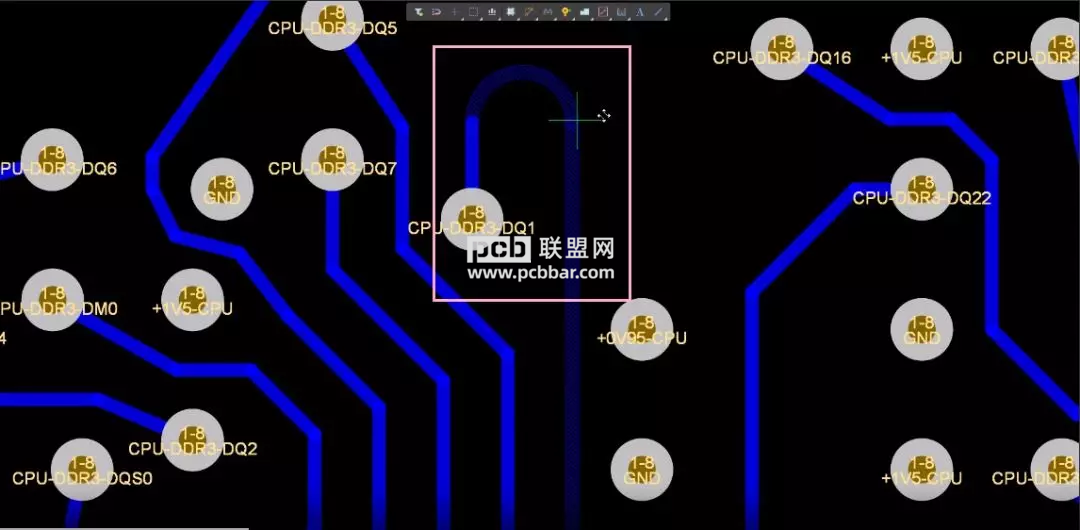

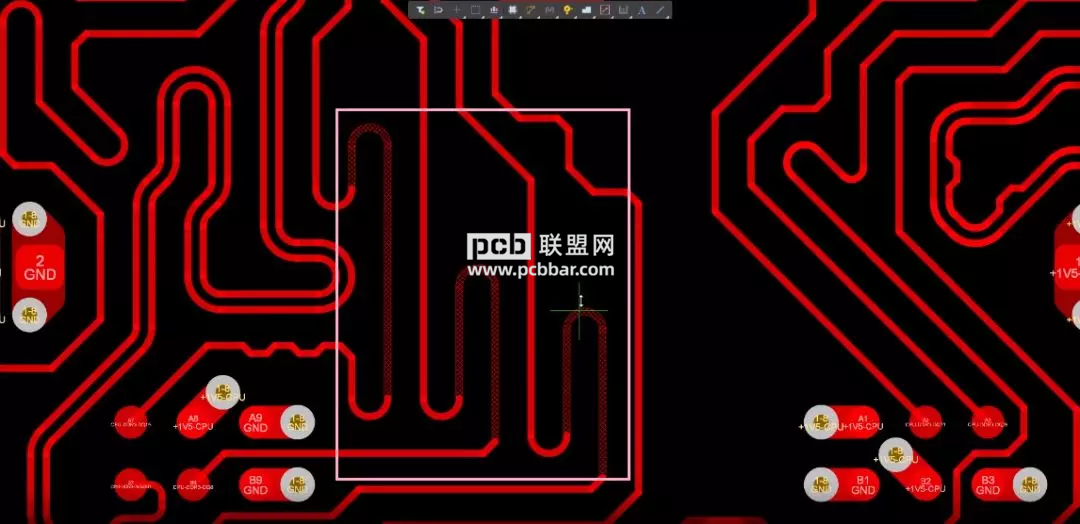

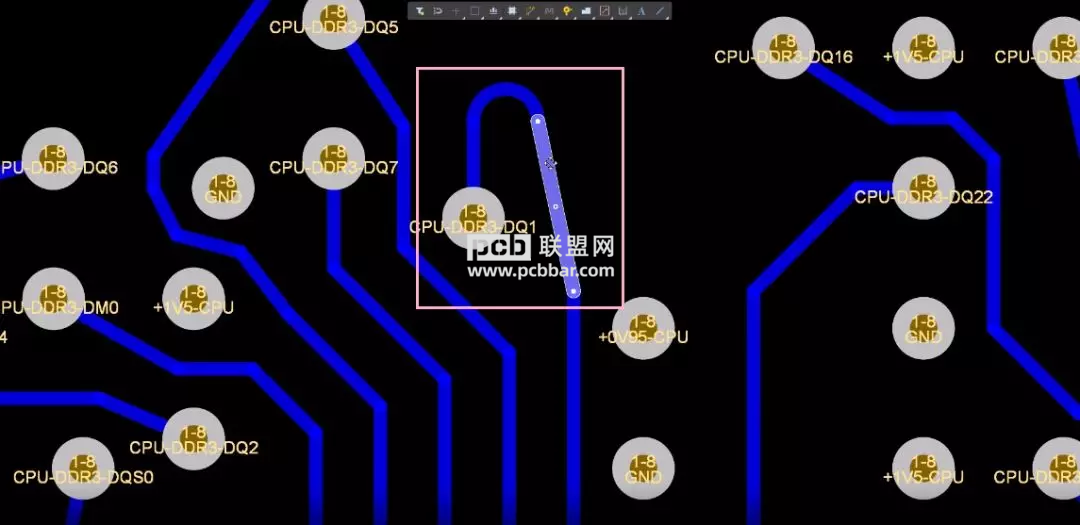

比如上图框框内是想处理的走线,只需要点击要处理的那一段,然后鼠标一拖。如下图。  在修整走线的时候还可以推挤,如下图所示,想要把框框内的一截线拉长些,又不影响其连接。  推挤的过程中会实时处理,遇到障碍物能推挤就推挤,不能推挤惹不起的躲得起,自己闪避。  还可以对多根线同时修整处理。如下图,选取三段圆弧线。  对它们上下移动的过程中,同时推挤。  防止帖子沉了,请回复之后查看全部 本帖隐藏的内容新的原理图增强

来源: 作者:电子工程专辑 |

暂无评论