本次文章给大家介绍一种便宜好用的协议分析工具,逻辑分析仪,首先声明,小飞哥作这篇介绍文章,不是为了打广告哈,实在是因为这个小玩意很好用,有些小伙伴还不太清楚该如何使用!!!废话不多说,下图是我目前用的一种,8通道24MHZ,一般的低速信号分析是足够用了,比较高级的功能也更高级,当然价格也更贵。话不多说,开始对这个小玩意如何使用进行简单的介绍。

实验目标:

1、学会使用逻辑分析仪采集常用协议信号;

2、学会如何分析协议数据;

硬件准备:

1、逻辑分析仪

2、电路板(什么型号无所谓,能正常运行就可以)

一、软件安装及界面介绍

购买时候店家会给你资料包,找到上位机软件,直接根据自己电脑系统安装对应的安装包就可以了。

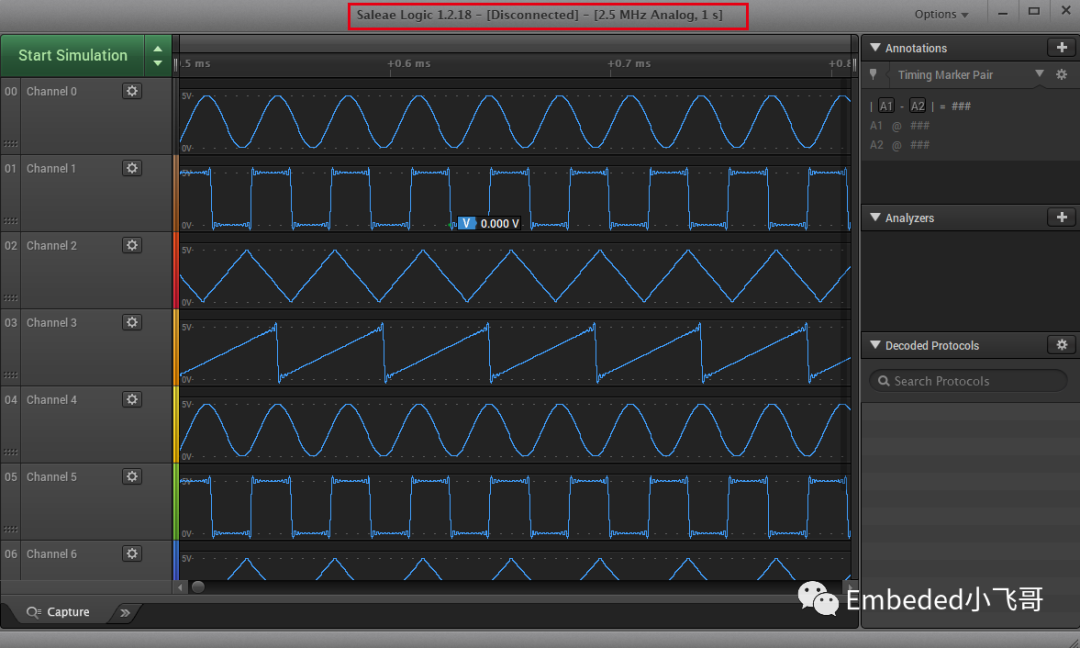

安装完成之后打开界面如下图,无逻辑分析仪的时候显示Disconnected,左边是8个通道,使用时候根据硬件连接选择对应通过进行配置,中间部分是显示我们逻辑波形的区域,右边是添加一些协议数据格式,数据分析区域。

下面先对这几个区域一一进行介绍,懂得自行跳过哈。

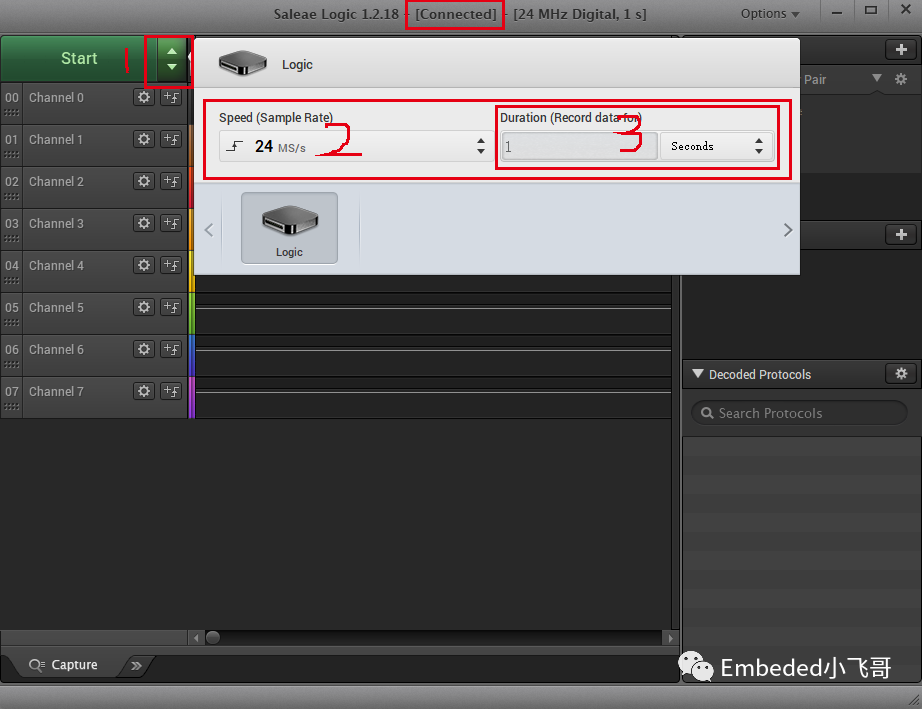

连接上逻辑分析仪可以看到已经显示连接了,接下来,点击标号1处红框,会出现后面的配置项,一般默认是24M,可以不做更改,也可以选择需要的采样率,主要是跟你通讯速率有关系,要大于你的通讯速率,3处是采集的周期,也就是你要采集多长时间的波形,跟示波器的储存深度一个意思。

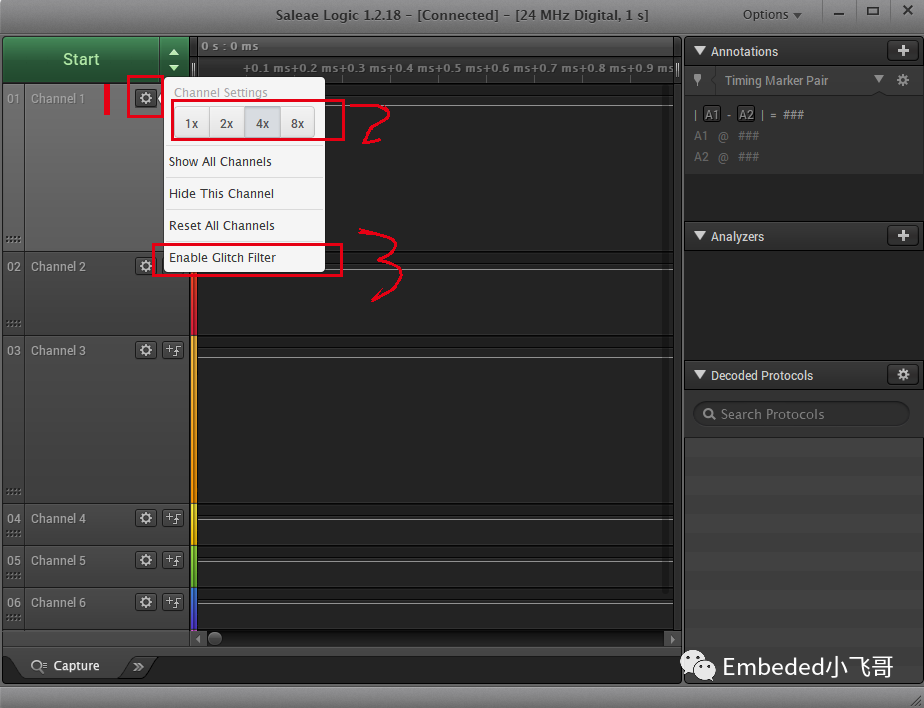

这个是对每个通道的设置,第一项是波形幅值比例,通道0,1,2我调了不同的比例,效果就是这样,3处的是消除毛刺的,一般就默认就可以了,这个功能我也没研究过。

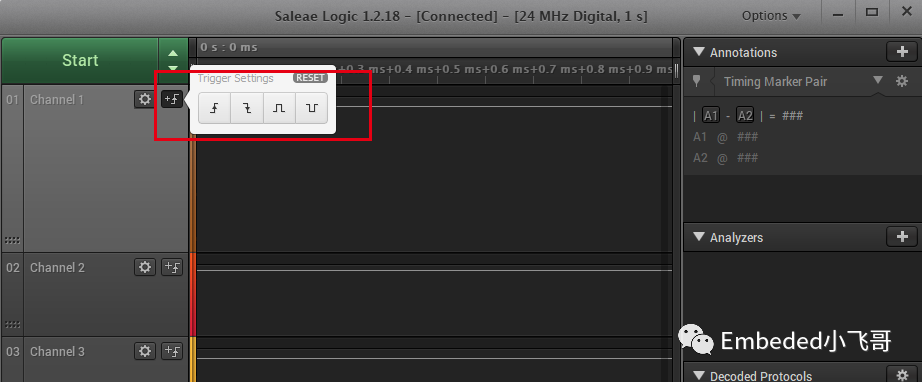

这个是触发方式选择,上升沿、下降沿,双边沿,主要跟协议信号有关系,比如串口接收数据,起始位是低电平,配置为下降沿触发就可以。

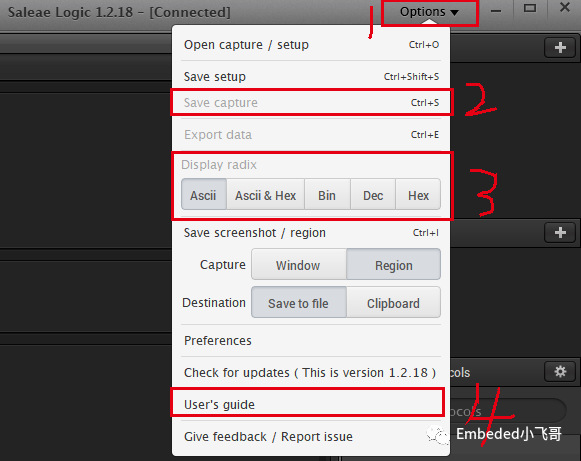

点开标号1,下拉菜单中是一些配置选项,2是保存采集到的波形数据,后面在具体介绍,3是显示的数据格式,根据自己的需要选择,4处是用户指南,伙伴们可以听我啰嗦,也可以查看官网使用说明,英文的,可能不太好打开。

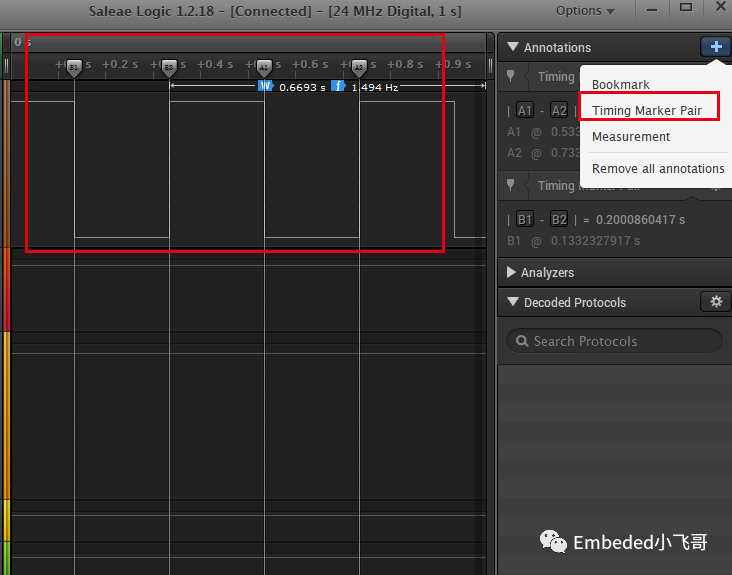

点开Annotations选项,可以增加测量电平时间的组数,此处测量两组,类似示波器测量时间的标线,大家和示波器联系起来就很好理解啦。

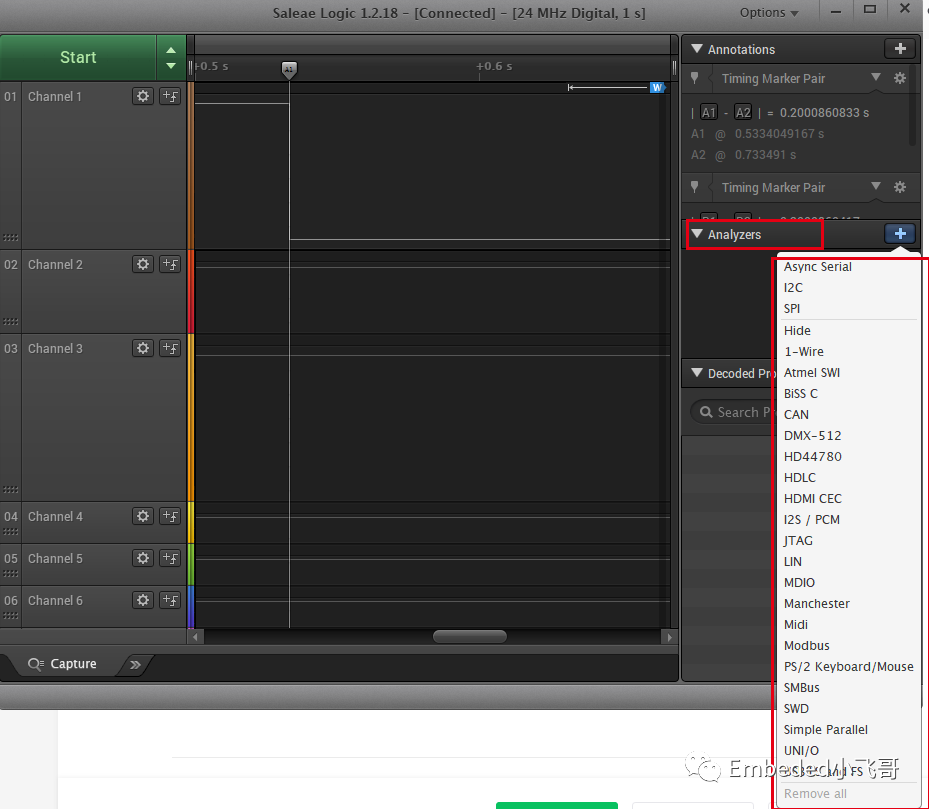

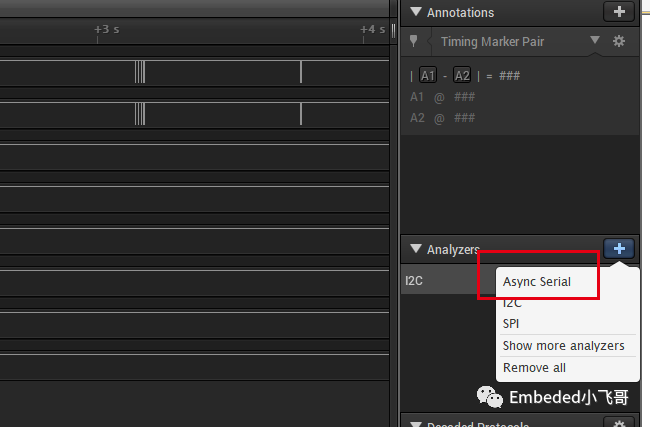

点击Analyzers选项,里面包含了很多协议,常用的串口、SPI、IIC、CAN等等,都可以进行测量。

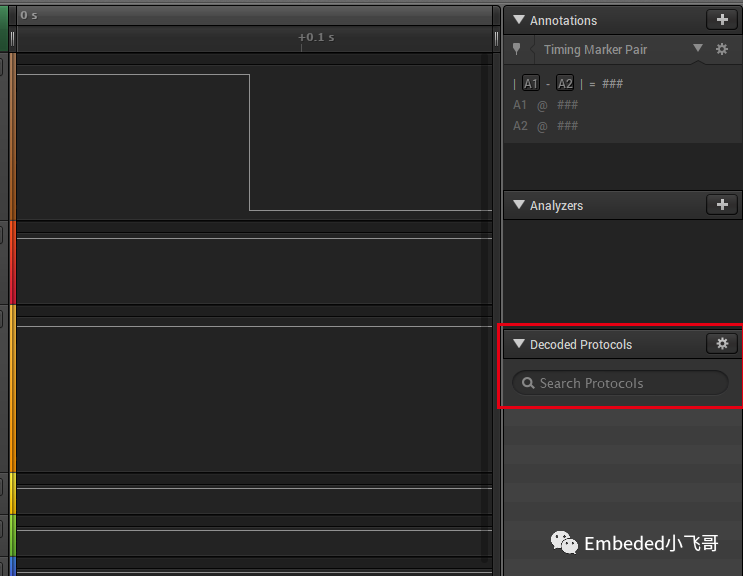

此处是协议解析部分,后面重点会讲,这里不啰嗦,界面的基本介绍就到这里,仅仅是介绍了常用的几种功能,还有些没介绍,如果有说错的大家谅解哈。

二、串口、IIC、SPI数据采集及协议解析

用到STM32F407ZGT6的开发板,主要对IIC,串口、SPI数据解析进行介绍。

1、IIC数据解析

开始之前,以AT24C02读写为例,先对I2C协议进行一点简介,熟悉的大佬自行跳过哈。

IIC(Inter-Integrated Circuit)总线是一种由 PHILIPS 公司开发的两线式串行总线,用于连接微控制器及其外围设备。它是由数据线 SDA 和时钟 SCL 构成的串行总线,可发送和接收数据。在 CPU 与被控 IC 之间、 IC 与 IC 之间进行双向传送, 高速 IIC 总线一般可达 400kbps 以上。

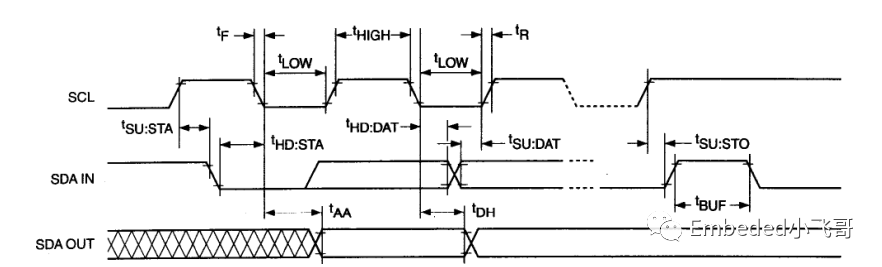

I2C 总线在传送数据过程中共有三种类型信号, 它们分别是:开始信号、结束信号和应答信号。

开始信号:SCL 为高电平时, SDA 由高电平向低电平跳变,开始传送数据。

结束信号:SCL 为高电平时, SDA 由低电平向高电平跳变,结束传送数据。

应答信号:接收数据的 IC 在接收到 8bit 数据后,向发送数据的 IC 发出特定的低电平脉冲,表示已收到数据。CPU 向受控单元发出一个信号后,等待受控单元发出一个应答信号, CPU 接收到应答信号后,根据实际情况作出是否继续传递信号的判断。若未收到应答信号,由判断为受控单元出现故障。

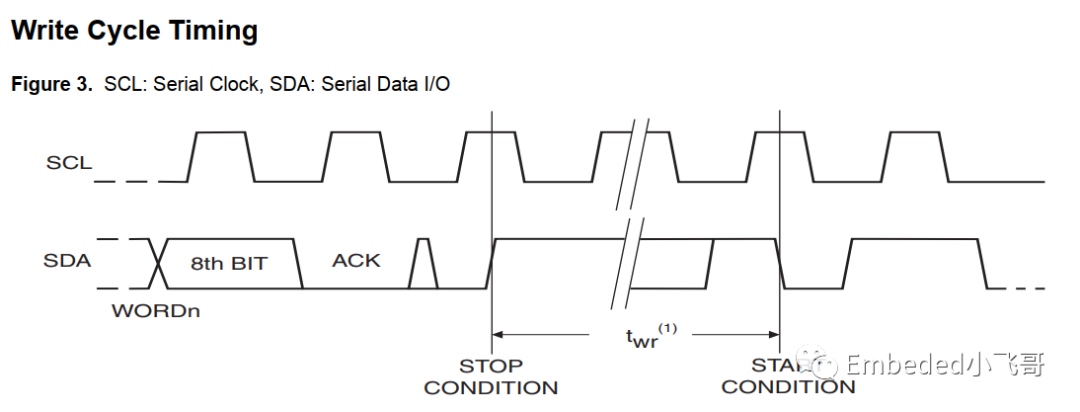

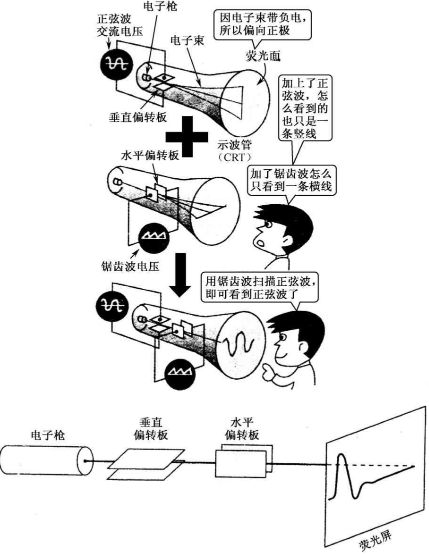

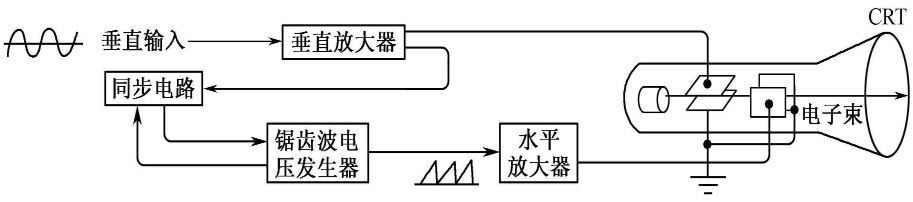

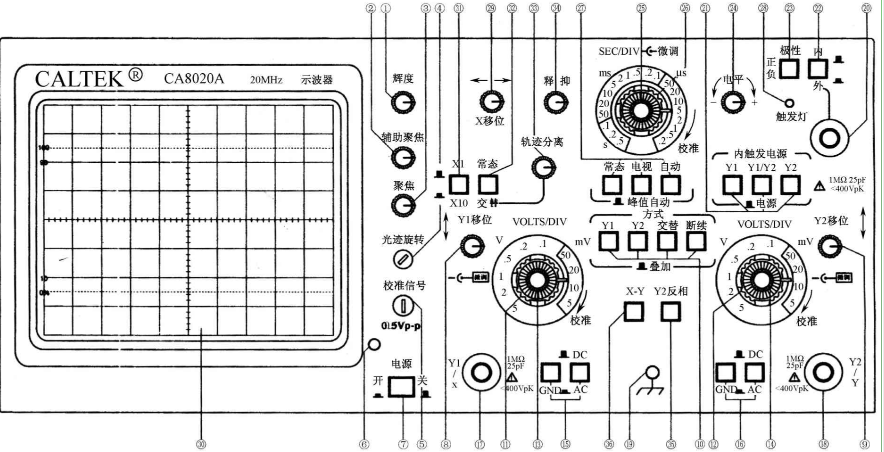

这些信号中,起始信号是必需的,结束信号和应答信号,都可以不要,I2C总线时序图如下面

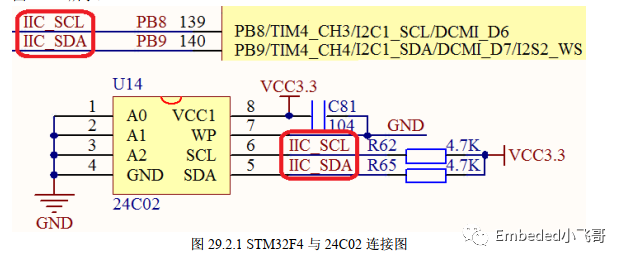

IIC一个主机可以悬挂多个从机,通过地址线A2,A1,A0 可以实行片选的功能,那么WP这个引脚的功能就是当WP悬空或者接地的时候,表示这时的EEPROM既可以读,也可以写,当WP接电源时,则只可以读而不能写。

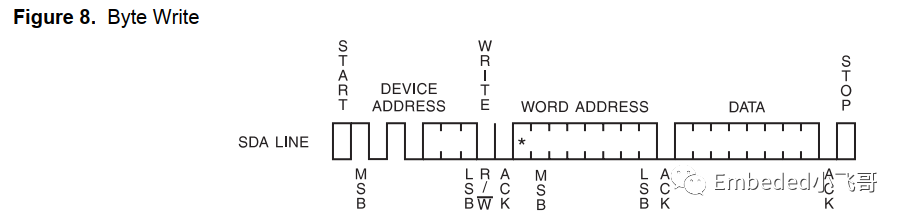

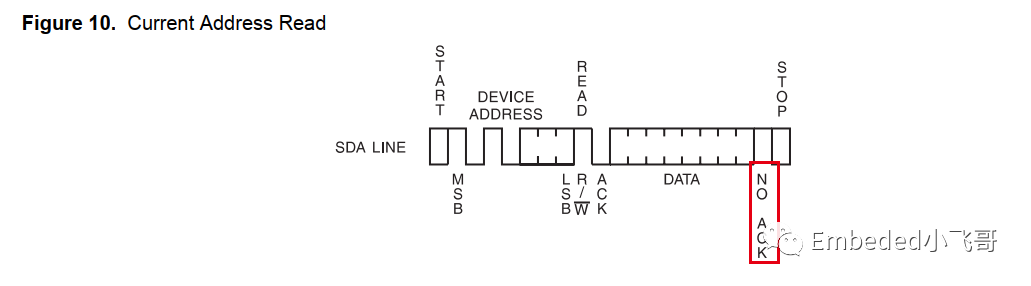

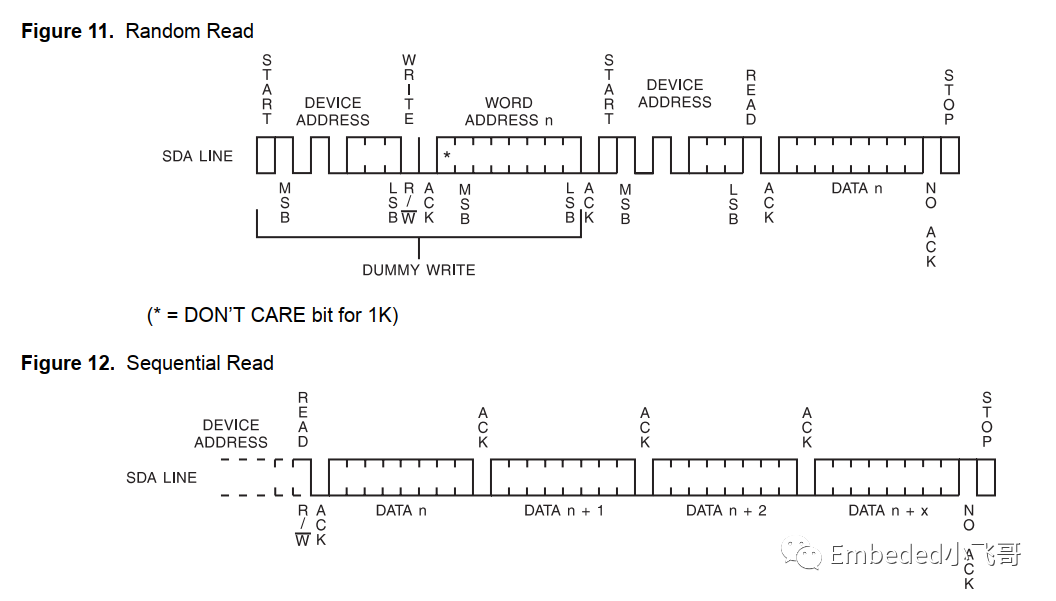

那么,对AT24C02进行读写的时序是怎样的呢,下面是从AT24C02手册摘录而来的时序图,进行简要的分析。

下图是SDA线上的时序图,SCL与SDA时序对应关系,写单字节通讯流程为:

1、发送起始信号

2、发送设备地址,高位在前

3、ACK信号,该信号由从机发出,主机接收

4、发送要操作的eeprom地址,即是要写数据到的地址

5、发送要写入的数据

6、接收从机应答信号

7、发送stop信号,通信结束

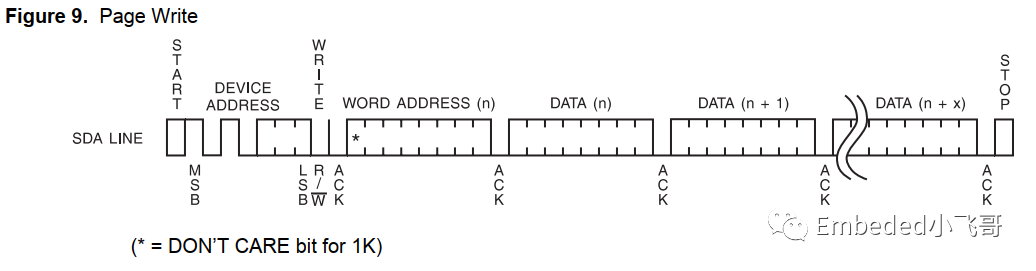

多字节写入,多字节写入与单字节开始、结束相同,只不过中间多了一些数据。

单字节读取,与单字节写基本流程相同,有一点不同是stop前不需要回复ack信号,要注意no ack信号是由主机发出的,多字节读取分为两种,一种是任意地址读取,连续地址读取,任意地址读取的时候,需要先写器件地址,也就是选择从设备,然后在进行读取操作,连续地址就比较简单了,类似于单字节读取数据。

对i2c协议及与AT24c02通讯时序简单介绍完了,如有错误之处,欢迎大家提出,自己注意哈,下面进入正题,通过逻辑分析仪采集数据并解码分析。逻辑分析仪与电路板接线图:

| 逻辑分析仪 | 开发板 |

| CH0 | PB8(SCL) |

| CH1 | PB9(SDA) |

| GND | GND |

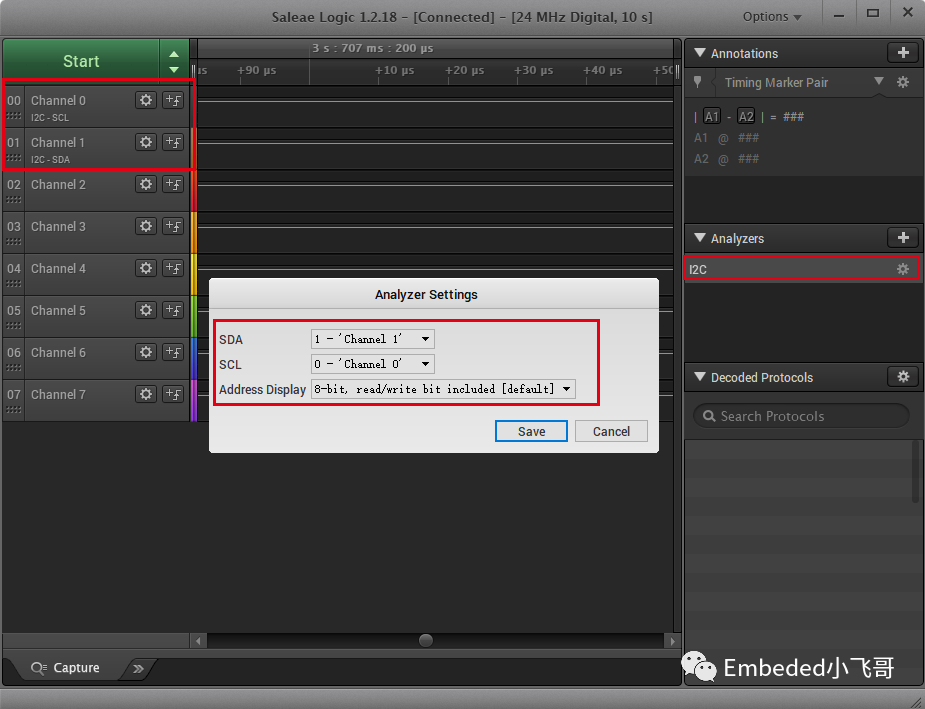

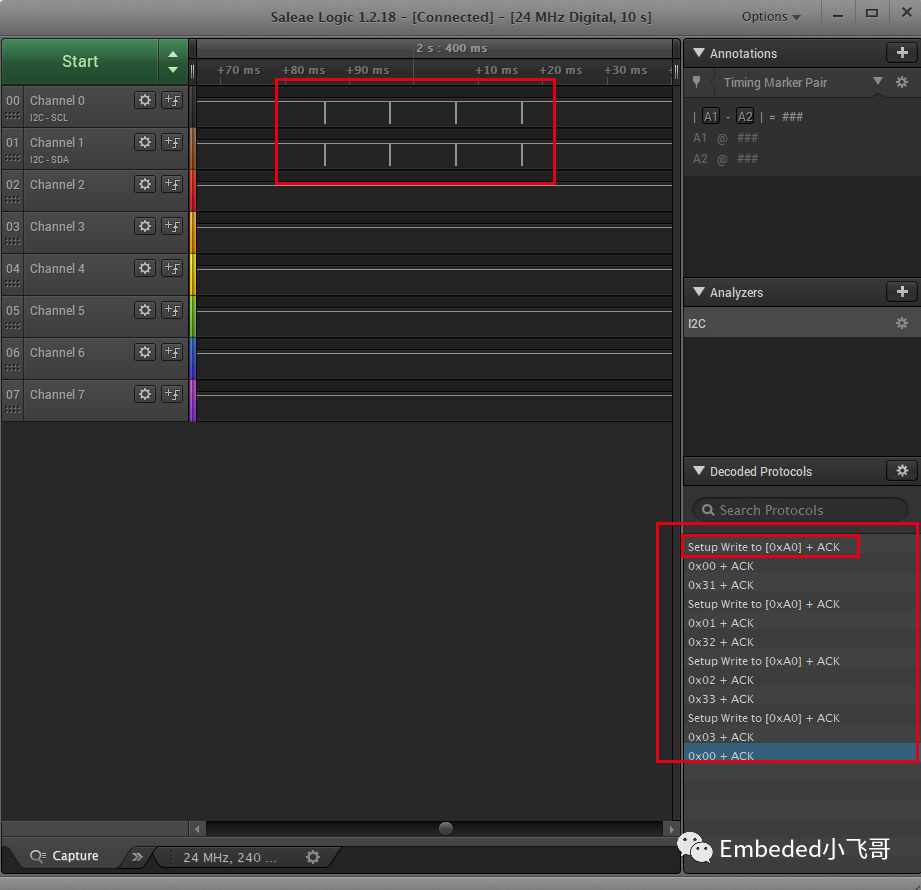

逻辑分析仪的Analyzers选择I2C,配置I2C通道,通道0是scl信号,通道1是sda信号,接下来就可以截取数据啦。

输入写入的eeprom,从地址0开始写,写入1230,16进制也就是0x31,0x32,0x33,0x30,根据解码的数据来看,多字节写入,代码采用的是单字节写入方式,循环调用,跟上面手册提供的有点出入,但也可以实现,接下来对数据进行分析。

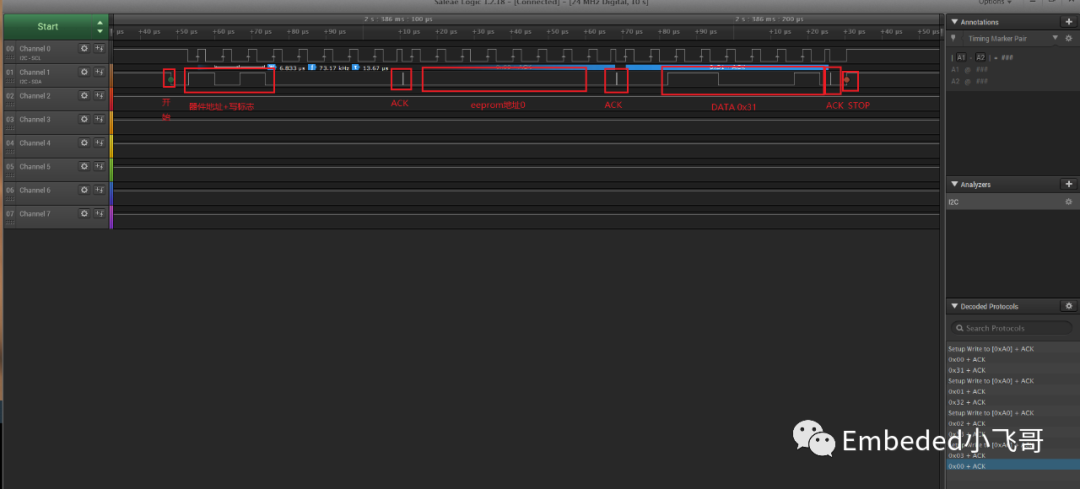

首先是开始信号,接下来是发送器件地址,接收到ack信号,写eeprom地址,接收到从机ack数据,发送要写入的数据,接收到从机ack数据,停止信号,这就是一个完整的通讯周期,小伙伴们明白了嘛。

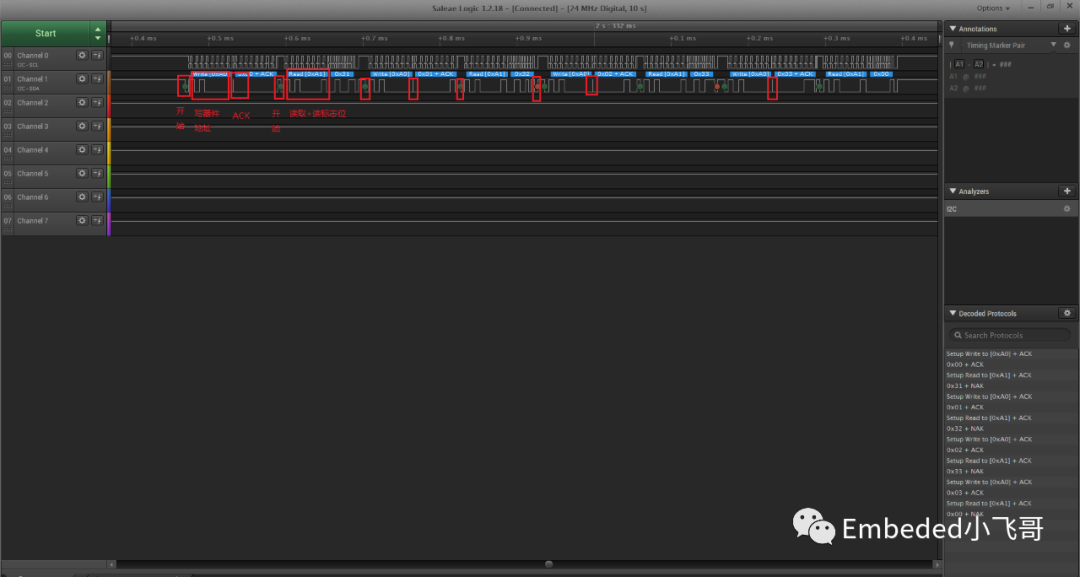

然后我们对刚才写入的数据进行读取,向上面分析的一样,读取数据之后 Nack,我们发现数据读取之后,从机并未回复ACK信号,与我们的分析一致。

由于图片比较大,原图会放在网上,大家可以下载下来,对照着分析一下,熟悉协议后是非常简单的,主要工作是要熟悉i2c通讯协议格式。

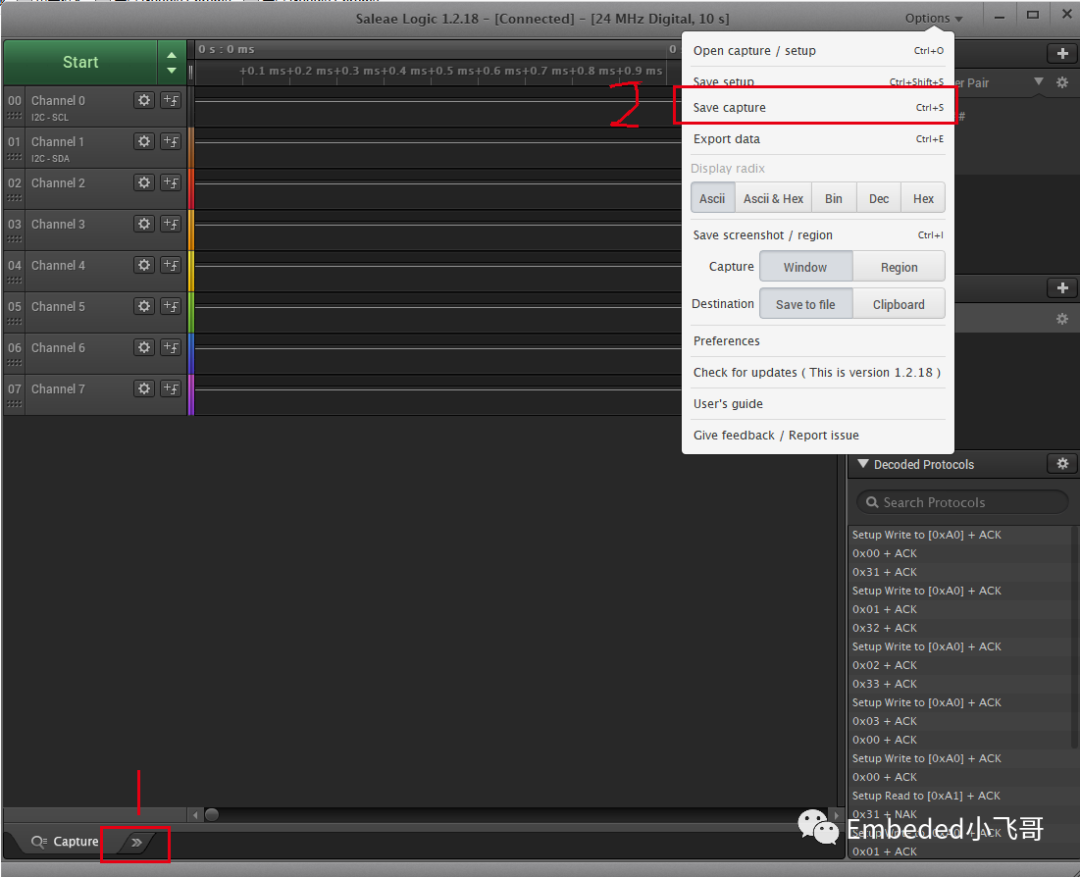

对于数据波形,我们是可以直接保存为逻辑分析仪软件能够打开的格式的,我们可以进行放大等操作,怎么保存呢,只需要点击下面两步就可以啦,是不是很方便呢。

2、串口数据解析

2、串口数据解析

具体介绍网上相信有很多,本次主要是介绍逻辑分析仪的使用,麻烦伙伴们自行去百度一下哈。

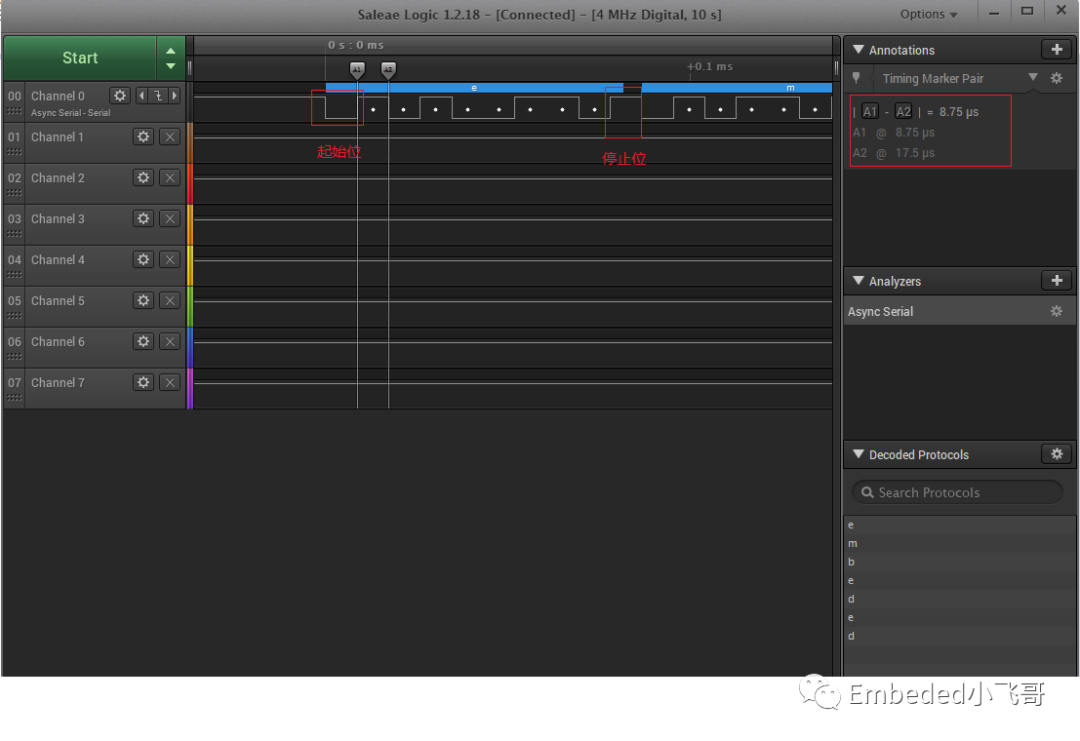

主要介绍一下波特率是怎么计算的,UART通信协议进行一个字节数据的传输时就是在信号线上产生八个高低电平的组合,数据传送速率用波特率来表示,即每秒钟传送的二进制位数。例如数据传送速率为120字符/秒,而每一个字符为10位(1个起始位,7个数据位,1个校验位,1个结束位),则其传送的波特率为10×120=1200字符/秒=1200波特。简单来说就是,如果你配置的波特率为9600,那么你每一bit时间就是1/9600 = 104us,一会通过逻辑分析仪来看下bit时间。

那么进入正题吧,先来设置逻辑分析仪,通道是ch0,有了前面的铺垫,现在添加串口伙伴们应该明白了吧,连线OK后就来截取数据吧。

| 逻辑分析仪 | 开发板 |

| PA9(TXD) | CH0 |

| GND | GND |

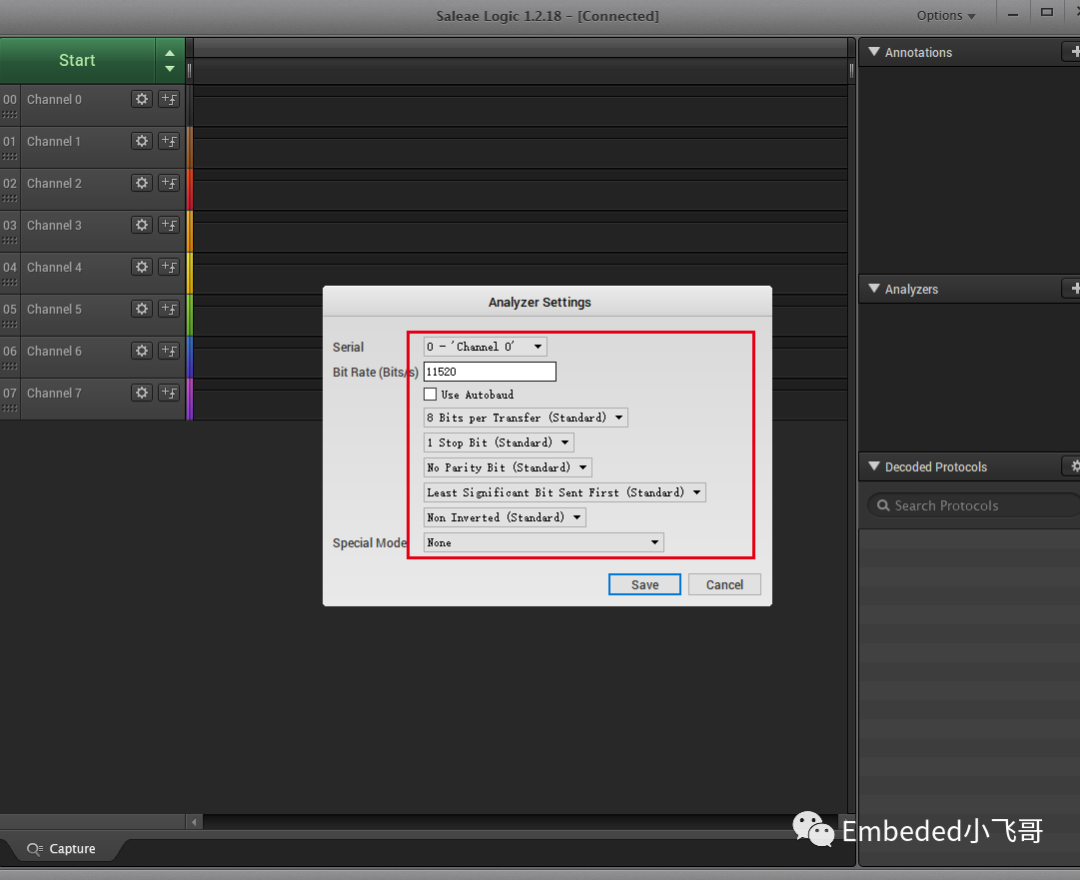

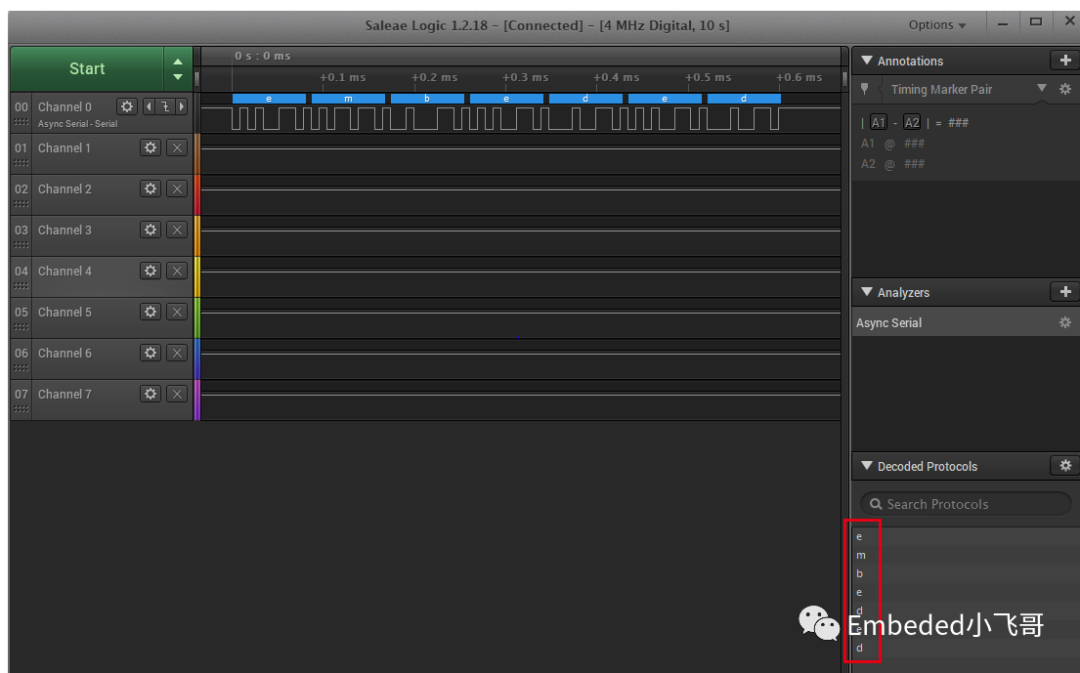

配置项跟串口配置保持一致即可,发送的数据为embeded,接下来对单个字节进行分析

开始是数据起始位,中间8bit数据位,最后一字节停止位,比较简单,单bit时间内为8.75us,我们设置的波特率为115200,1/115200 = 8.68us,可能是逻辑分析仪不好有误差,时间是有点误差的。串口数据的分析就结束啦。

3、SPI数据解析

同样的,我们以SPI读写flash作为实验,来对SPI数据协议进行介绍。SPI 是英语 Serial Peripheral interface 的缩写,顾名思义就是串行外围设备接口。是 Motorola首先在其 MC68HCXX 系列处理器上定义的。SPI 接口主要应用在 EEPROM, FLASH,实时时钟, AD 转换器,还有数字信号处理器和数字信号解码器之间。SPI,是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线,节约了芯片的管脚,同时为 PCB 的布局上节省空间,提供方便,正是出于这种简单易用的特性,现在越来越多的芯片集成了这种通信协议。

以下介绍摘自:https://www.cnblogs.com/deng-tao/p/6004280.html,作者讲得很好,伙伴们可以移步去看看。

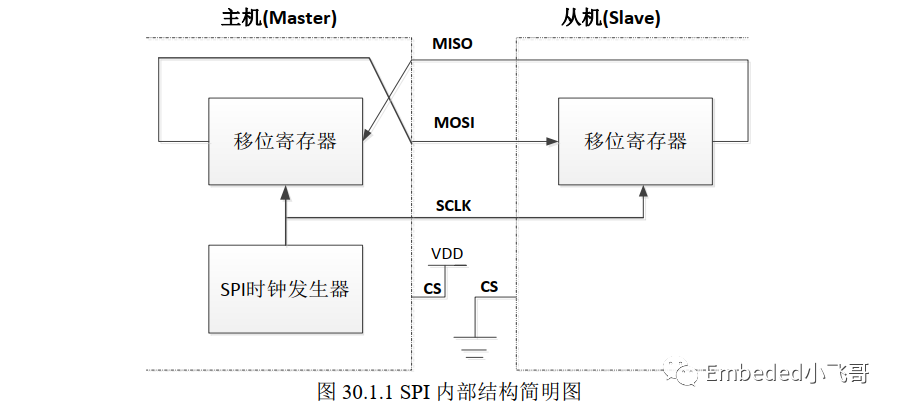

SPI的通信原理很简单,它以主从方式工作,这种模式通常有一个主设备和一个或多个从设备,需要至少4根线,事实上3根也可以(单向传输时)。也是所有基于SPI的设备共有的,它们是SDI(数据输入)、SDO(数据输出)、SCLK(时钟)、CS(片选)。

(1)SDO/MOSI – 主设备数据输出,从设备数据输入;

(2)SDI/MISO – 主设备数据输入,从设备数据输出;

(3)SCLK – 时钟信号,由主设备产生;

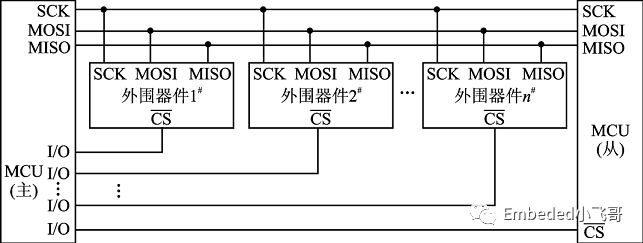

(4)CS/SS – 从设备使能信号,由主设备控制。当有多个从设备的时候,因为每个从设

备上都有一个片选引脚接入到主设备机中,当我们的主设备和某个从设备通信时将需要将从设备对应的片选引脚电平拉低或者是拉高。

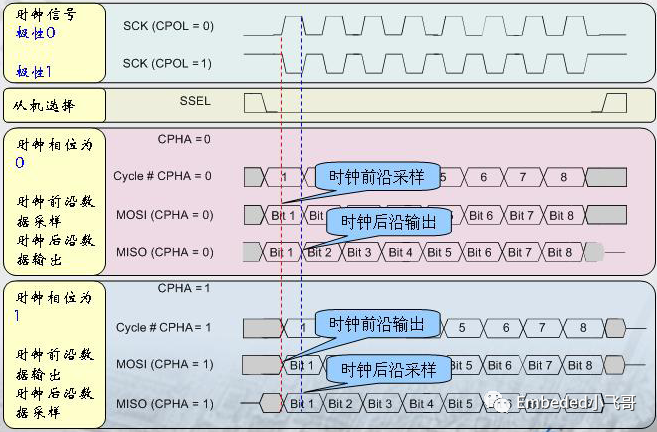

我们SPI通信有4种不同的模式,不同的从设备可能在出厂是就是配置为某种模式,这是不能改变的;但我们的通信双方必须是工作在同一模式下,所以我们可以对我们的主设备的SPI模式进行配置,通过CPOL(时钟极性)和CPHA(时钟相位)来控制我们主设备的通信模式,具体如下:

Mode0:CPOL=0,CPHA=0

Mode1:CPOL=0,CPHA=1

Mode2:CPOL=1,CPHA=0

Mode3:CPOL=1,CPHA=1

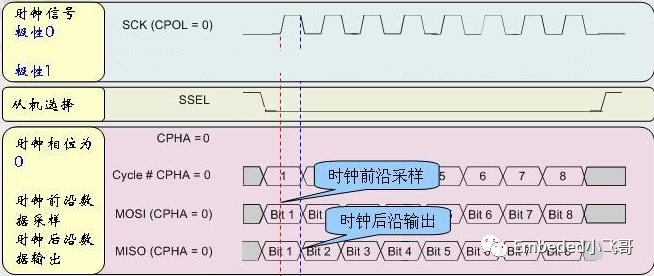

时钟极性CPOL是用来配置SCLK的电平出于哪种状态时是空闲态或者有效态,时钟相位CPHA是用来配置数据采样是在第几个边沿:

CPOL=0,表示当SCLK=0时处于空闲态,所以有效状态就是SCLK处于高电平时

CPOL=1,表示当SCLK=1时处于空闲态,所以有效状态就是SCLK处于低电平时

CPHA=0,表示数据采样是在第1个边沿,数据发送在第2个边沿

CPHA=1,表示数据采样是在第2个边沿,数据发送在第1个边沿

例如:

CPOL=0,CPHA=0:此时空闲态时,SCLK处于低电平,数据采样是在第1个边沿,也就是SCLK由低电平到高电平的跳变,所以数据采样是在上升沿,数据发送是在下降沿。

CPOL=0,CPHA=1:此时空闲态时,SCLK处于低电平,数据发送是在第1个边沿,也就是SCLK由低电平到高电平的跳变,所以数据采样是在下降沿,数据发送是在上升沿。

CPOL=1,CPHA=0:此时空闲态时,SCLK处于高电平,数据采集是在第1个边沿,也就是SCLK由高电平到低电平的跳变,所以数据采集是在下降沿,数据发送是在上升沿。

CPOL=1,CPHA=1:此时空闲态时,SCLK处于高电平,数据发送是在第1个边沿,也就是SCLK由高电平到低电平的跳变,所以数据采集是在上升沿,数据发送是在下降沿。

需要注意的是:我们的主设备能够控制时钟,因为我们的SPI通信并不像UART或者IIC通信那样有专门的通信周期,有专门的通信起始信号,有专门的通信结束信号;所以我们的SPI协议能够通过控制时钟信号线,当没有数据交流的时候我们的时钟线要么是保持高电平要么是保持低电平。

介绍到此结束,下面进行逻辑分析仪的数据分析

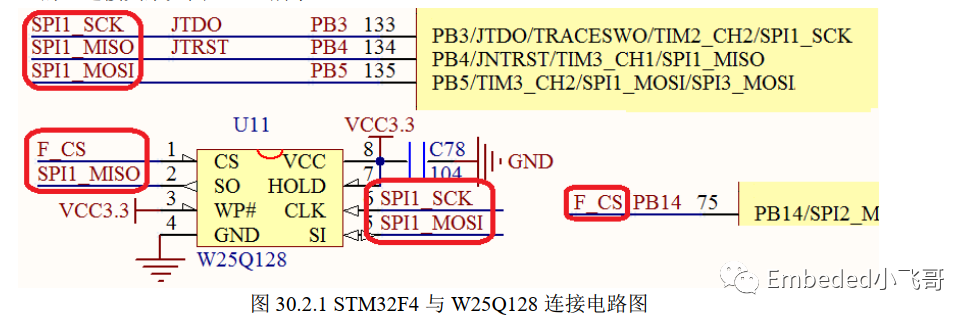

硬件连接:

开发板与逻辑分析仪接线图

| 开发板 | 逻辑分析仪 |

| PB3(CLK) | CH0 |

| PB4(MISO) | CH1 |

| PB5(MOSI) | CH2 |

| PB14(CS) | CH3 |

| GND | GND |

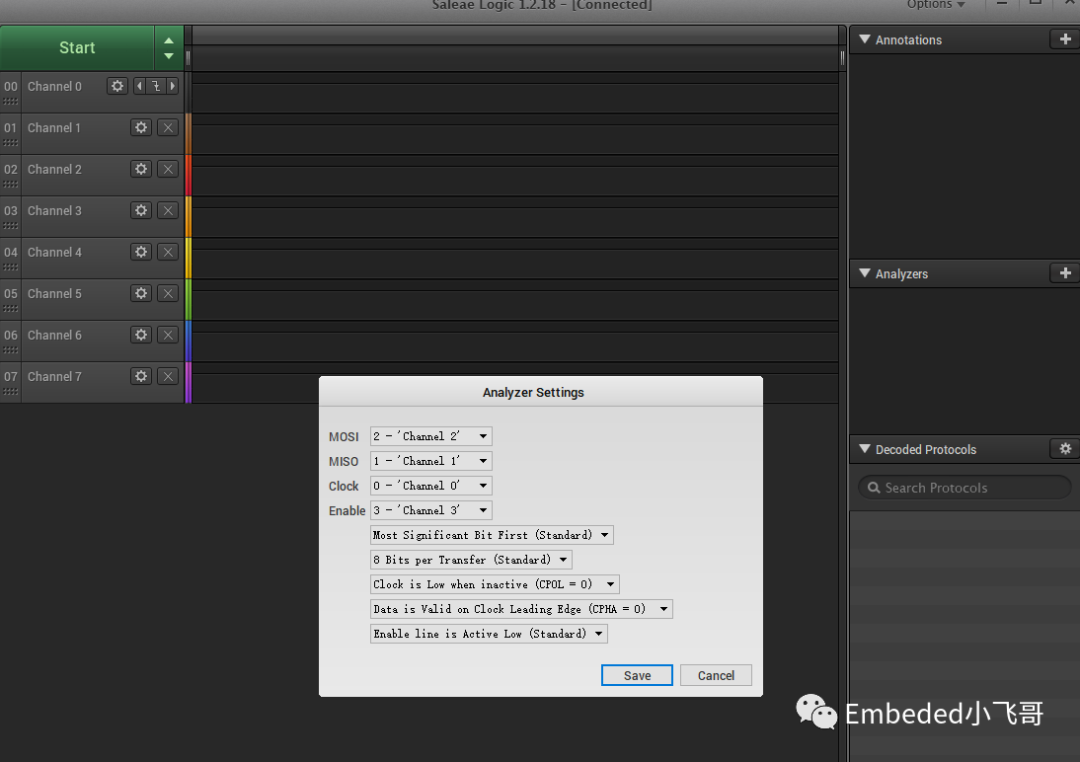

配置也是一样的,跟代码配置保持一致

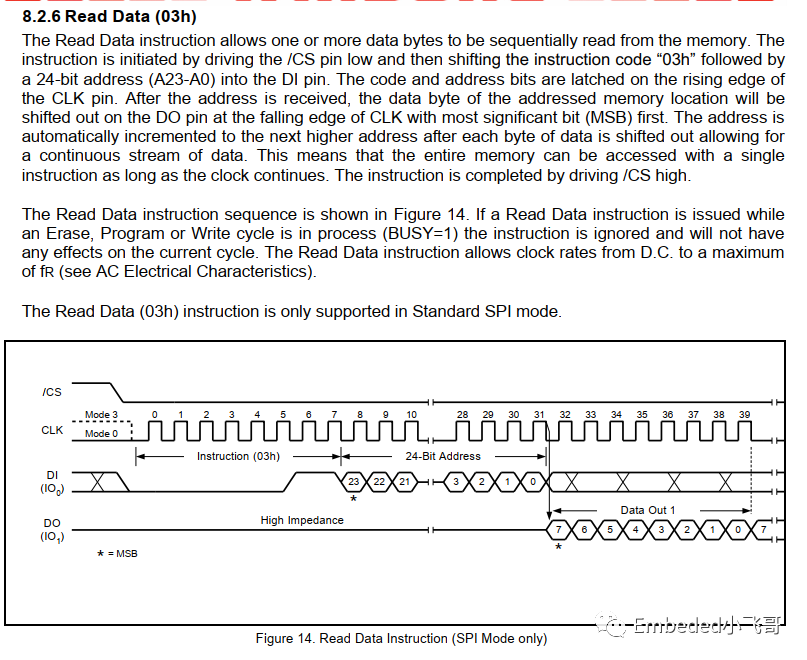

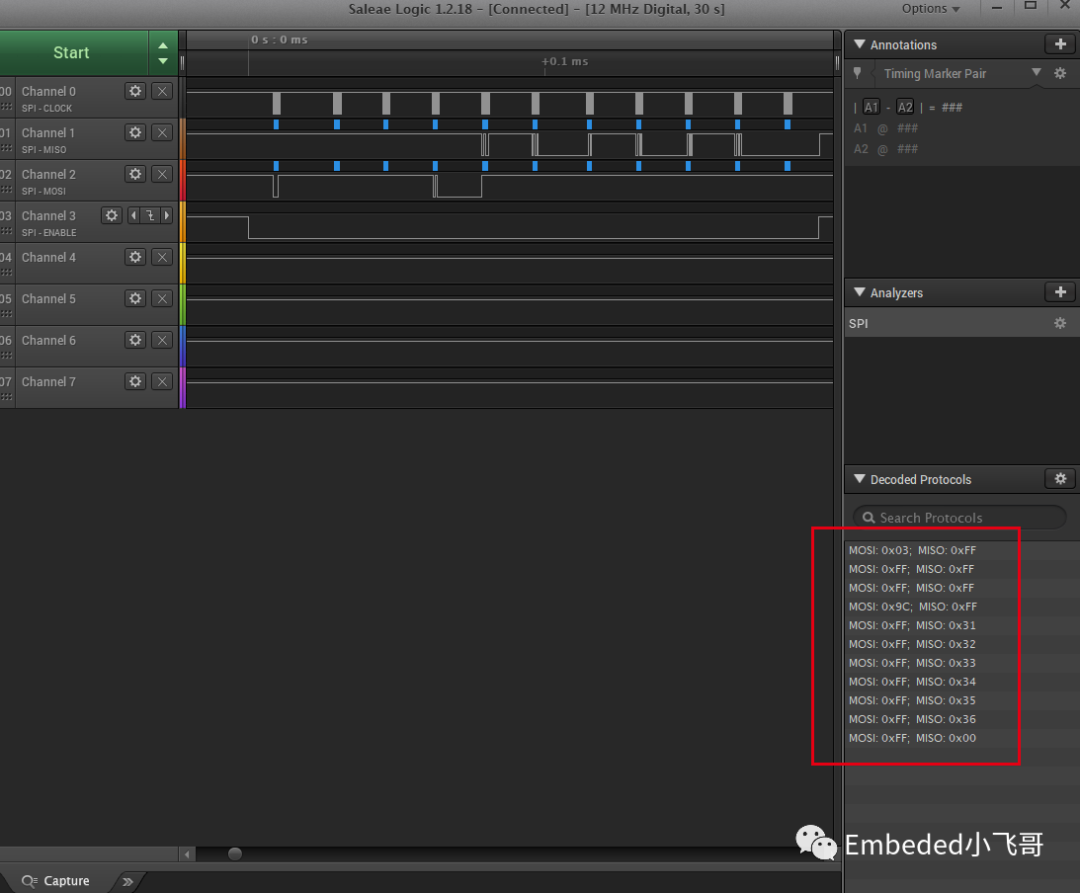

主要对读取flash内容进行分析,flash手册给出的时序如下图,cs引脚拉低使能,发送03H,在发送24bit也即是3字节地址数据,然后数据由MISO引脚输出。

结合时序图对截取到的数据进行分析,可以看到数据正如手册描述的一样,主机发送读取指令03H,接下来发送3字节地址信息,再进行数据的读取,读取数据截图,读出的数据是1234560,也是非常的简单啦。另外,可以看出空闲时间,clk引脚是高电平,至于写数据,也是一样的分析方法,就不再赘述啦。

本次要分享的内容就要结束啦,做的也比较粗糙,希望对大家对于逻辑分析仪的使用有个大概的了解,不足之处,大家多多指教哈。

如果你觉得对自己有帮助的话,给个赞,点个关注,点个在看,感谢前进的道路上有你的陪伴!

暂无评论