埋入式互连装置将帮助拯救摩尔定律。

一段时间以来,每种新处理器产生的废热都比原先的要多。如果芯片还是按2000年代早期的轨迹发展,它们的热功率很快将达到每平方厘米6400瓦,相当于太阳表面的功率通量。

但事情没有变得那么糟糕,工程师们在努力控制芯片功耗。在性能方面,数据中心的片上系统(SoC)设计一直仅次于超级计算机处理器,它们的功耗通常为200至400瓦/平方厘米。智能手机芯片的典型功耗为5瓦左右。

不过,虽然计算机芯片不会真的把口袋烧一个洞(尽管它们产生的热量的确足以煎鸡蛋),但要运行日常的应用程序,它们仍然需要大量的电流。以数据中心的片上系统为例:平均来说,它内部的晶体管功耗大约为200瓦,在约1到2伏的电压环境下,这意味着芯片需要从稳压电源中汲取100到200安的电流。冰箱的电流一般仅为6安。高端手机的功耗是数据中心片上系统的1/10,但即便如此,电流仍然达到了10至20安。也就是说,你的口袋里可能装着3台冰箱!

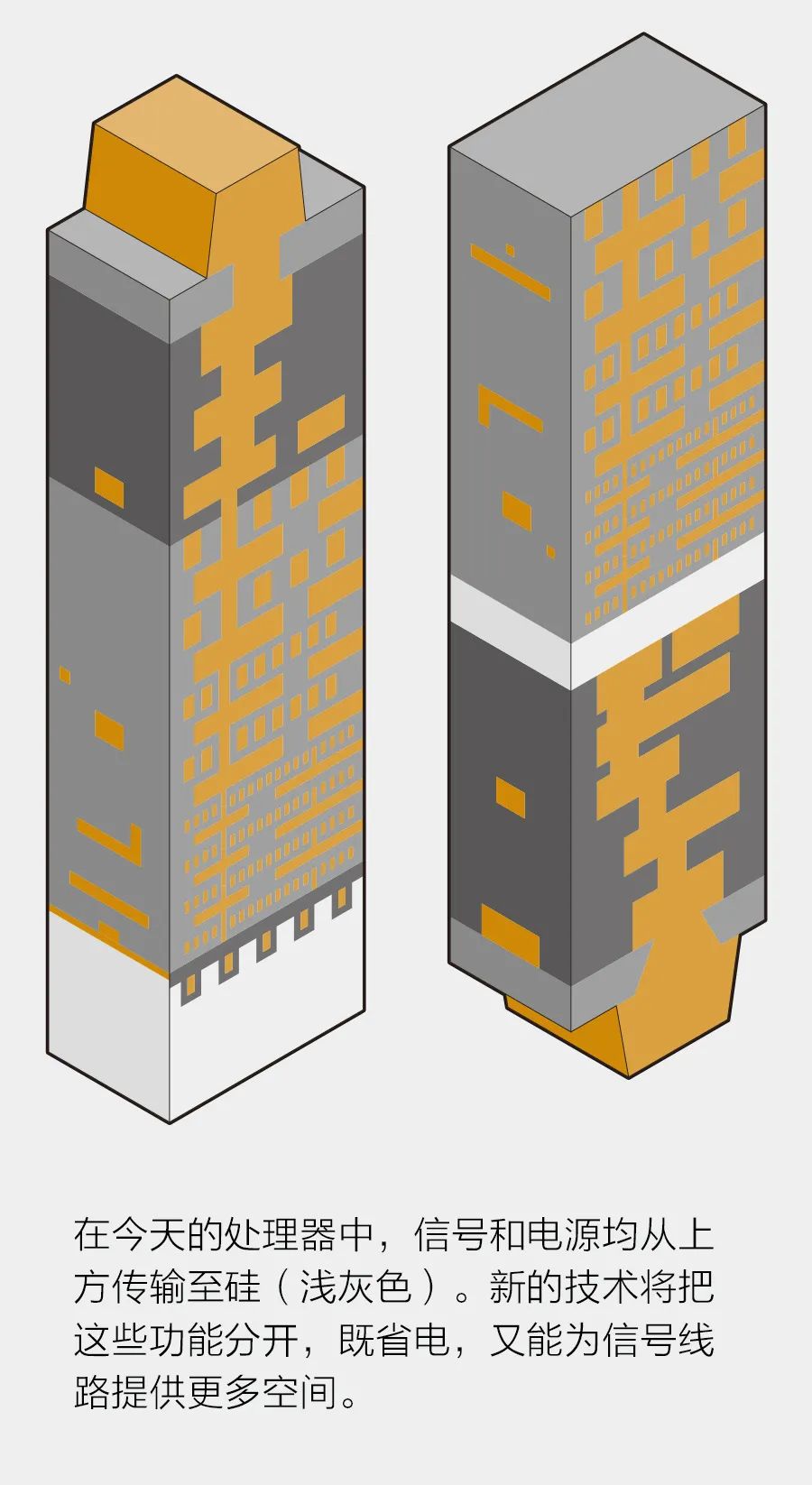

将电流传送至数十亿个晶体管正迅速成为高性能片上系统设计的主要瓶颈之一。随着晶体管不断变小,为其提供电流的互连装置必须封装得越来越紧密,做得越来越小巧,但这会增加电阻和衰减电源。这条路已走不下去:如果不对芯片器件的电子进出方式进行大的改变,无论我们制造多小的晶体管都无济于事。

幸运的是,我们有一个很有希望的解决方案:可以使用长期被忽视的硅的另一面。

从产生电子的电源到用电子进行计算的晶体管,电子要走很长的一段路。在大多数电子设备中,电子沿着印刷电路板的铜线到达片上系统的封装,经过连接芯片与封装的焊锡球进入芯片,然后通过芯片上的互连装置连接到内部晶体管。最后这一步才是真正最重要的。

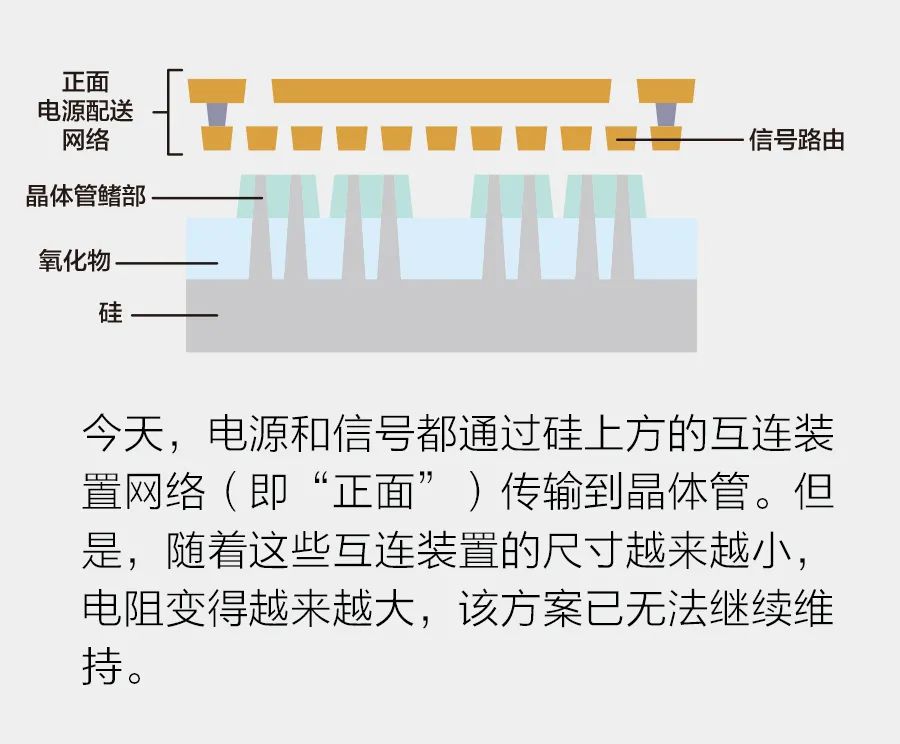

想知道为什么,最好先了解芯片的制造过程。片上系统从一块高质量的晶体硅开始。我们首先在这块硅的最上面做一层晶体管。接下来,用金属的互连装置将晶体管连接起来,形成有计算功能的电路。这些互连装置是一层一层叠起来的,被称为堆栈,要为当今芯片上的数十亿个晶体管提供电源和数据传输,堆栈需要达到10到20层。 为了连接微小的晶体管,最靠近硅晶体管的那几层又薄又小,但随着堆栈高度的上升,它们的尺寸会变大。这些互连装置层越宽,电阻越小,越有利于电源供电。

为了连接微小的晶体管,最靠近硅晶体管的那几层又薄又小,但随着堆栈高度的上升,它们的尺寸会变大。这些互连装置层越宽,电阻越小,越有利于电源供电。

然后,可以看到,为电路——电源配送网络(PDN)——供电的金属位于晶体管的顶部。我们称之为正面电源。我们还看到,电源配送网络会不可避免地与信号传输网络争夺空间,因为它们共享同一组铜资源。 为了使片上系统获取电源和传输信号,我们通常将最上面(离晶体管最远)的金属层连接到芯片封装的焊锡球(也称为“凸点”)。因此,电子要到达任意一个晶体管做有用功,必需穿过10到20层越来越窄且弯弯曲曲的金属层,直至最终到达最后一层的本地连接。

为了使片上系统获取电源和传输信号,我们通常将最上面(离晶体管最远)的金属层连接到芯片封装的焊锡球(也称为“凸点”)。因此,电子要到达任意一个晶体管做有用功,必需穿过10到20层越来越窄且弯弯曲曲的金属层,直至最终到达最后一层的本地连接。 这种电源配送方式肯定是有损耗的。在这条路径的每一阶段,有些电能损失了,还有一些用于控制配送本身。对于今天的片上系统,设计者通常有一个损耗预算,允许封装和晶体管之间的电压降低10%。因此,如果电源配送网络的总效率达到90%及以上,那么我们的设计就是正确的。

这种电源配送方式肯定是有损耗的。在这条路径的每一阶段,有些电能损失了,还有一些用于控制配送本身。对于今天的片上系统,设计者通常有一个损耗预算,允许封装和晶体管之间的电压降低10%。因此,如果电源配送网络的总效率达到90%及以上,那么我们的设计就是正确的。

从历史上看,这种效率可以通过良好的工程设计实现,有些人甚至可能说,与我们今天面临的挑战相比,这很容易解决。对于今天的电子设备,片上系统设计者不仅要管理不断增加的功率密度,而且要管理每一代的功率损失都在急剧增加的互连装置。不断增加的损耗与制造纳米级导线的工艺有关。这一工艺及其使用的材料可以追溯到1997年左右,当时IBM开始用铜代替铝制造互连装置,整个行业也随之转变。在那之前,铝线一直是良好的导体,但随着摩尔定律曲线向前发展,它们的电阻很快变得太高、不可靠。在现代集成电路规模下,铜的导电性更好。但一旦互连装置的宽度缩小到100纳米以下,铜的电阻也开始出现问题。如今,已制成的最小互连装置约为20纳米,电阻已成为一个亟待解决的问题。为了描绘互连装置中的电子,可将它比喻成台球桌上的一副台球。现在想象一下把它们从桌子的一端推到另一端。少数几个球会在途中发生相互碰撞和反弹,但大多数会沿着直线行进。现在再设想一下把球桌缩小一半,那么你会看到更多的碰撞,球的移动也会变慢。接下来,再次缩小球桌,并将台球的数量增加10倍,这就是芯片制造商现在面临的情况。真正的电子不一定会发生碰撞,但它们相互距离足够近时,产生的分散的力会干扰其在导线中的流动。在纳米尺寸下,这会导致导线中的电阻大大增加,引发严重的电源损耗。电阻增大不是一个新挑战,但现在每个后续工艺节点的电阻增大幅度却是前所未有的。此外,管理这种增长的传统方法已不再适用,因为纳米级的制造规则强加了许多限制。为了防止电阻增加,可以任意增加某段导线宽度的日子已经过去了。现在,设计者必须严格遵守导线宽度的特定规范,否则芯片可能无法制造。因此,行业面临双重问题,即互连装置的电阻升高以及在芯片空间的缩小。

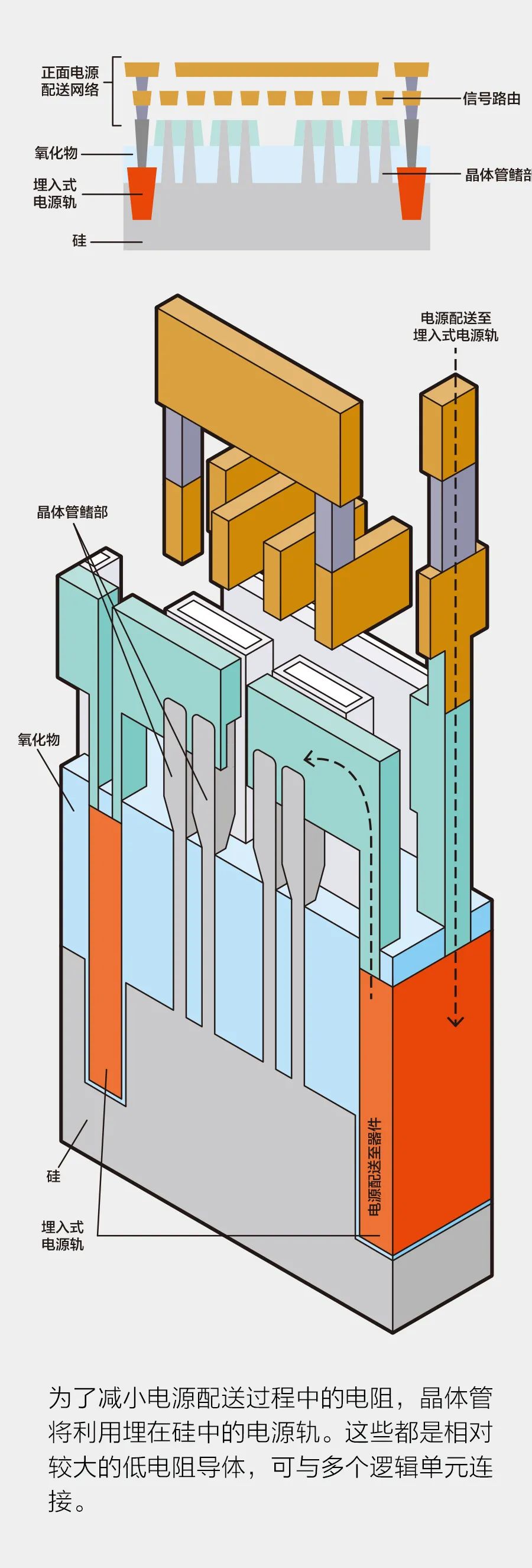

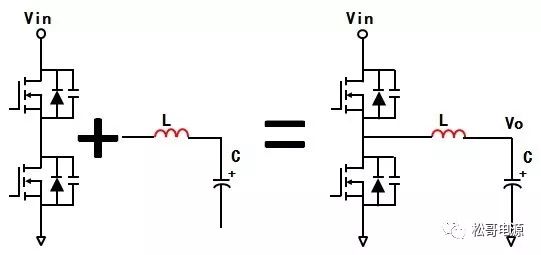

还有一种方法:可以利用晶体管下面的“空”硅。在作者贝恩(Beyne)和佐格拉福斯(Zografos)工作的微电子研究中心(Imec),我们率先提出了一种“埋入式电源轨”(BPR)制造概念。这项技术不是在晶体管上面而是下面建立电源连接,目的是建造更丰满、电阻更小的电源轨道,并为晶体管层上面的信号传输互连装置腾出空间。

要制作BPR,我们首先需要在晶体管下面挖出深槽,然后用金属填充,而且要在制造晶体管之前做这件事。金属的选择也很重要。这种金属需要承受制造高质量晶体管工艺步骤的温度,可达1000℃左右。在这个温度下,铜会熔化,进而污染整块芯片。因此,我们选用熔点更高的钌和钨进行试验。因为晶体管下方有许多未使用的空间,我们可以把BPR沟槽做得又宽又深,非常适合电源配送。与位于晶体管顶部的金属薄层相比,BPR的电阻是前者的1/20到1/30。这意味着BPR能有效地向晶体管配送更多的电源。此外,将电源轨从晶体管顶部移开,可为信号传输互连装置腾出空间。这些互连装置形成了基本的电路“单元”——最小的电路单位,如SRAM内存位单元或者用来构成复杂电路的简单逻辑单元。利用释放出来的空间,我们可以将这些单元缩小16%或更多,最终转化为每块芯片上更多的晶体管。即使特征尺寸保持不变,我们仍然可将摩尔定律推进一步。

遗憾的是,仅埋设局部的电源轨是不够的。我们仍然需要将电源从芯片顶部向下传输到这些电源轨,这会降低效率和损失部分电压。

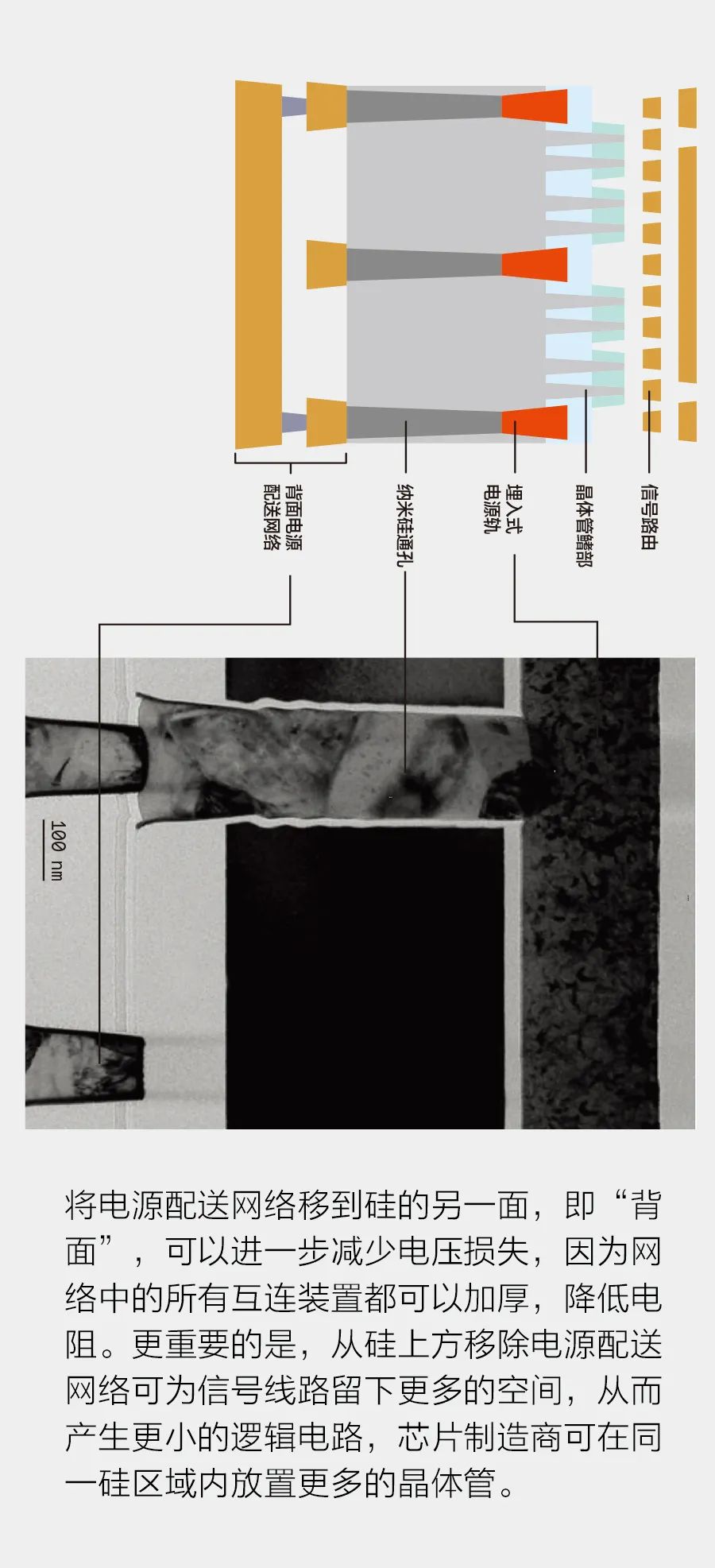

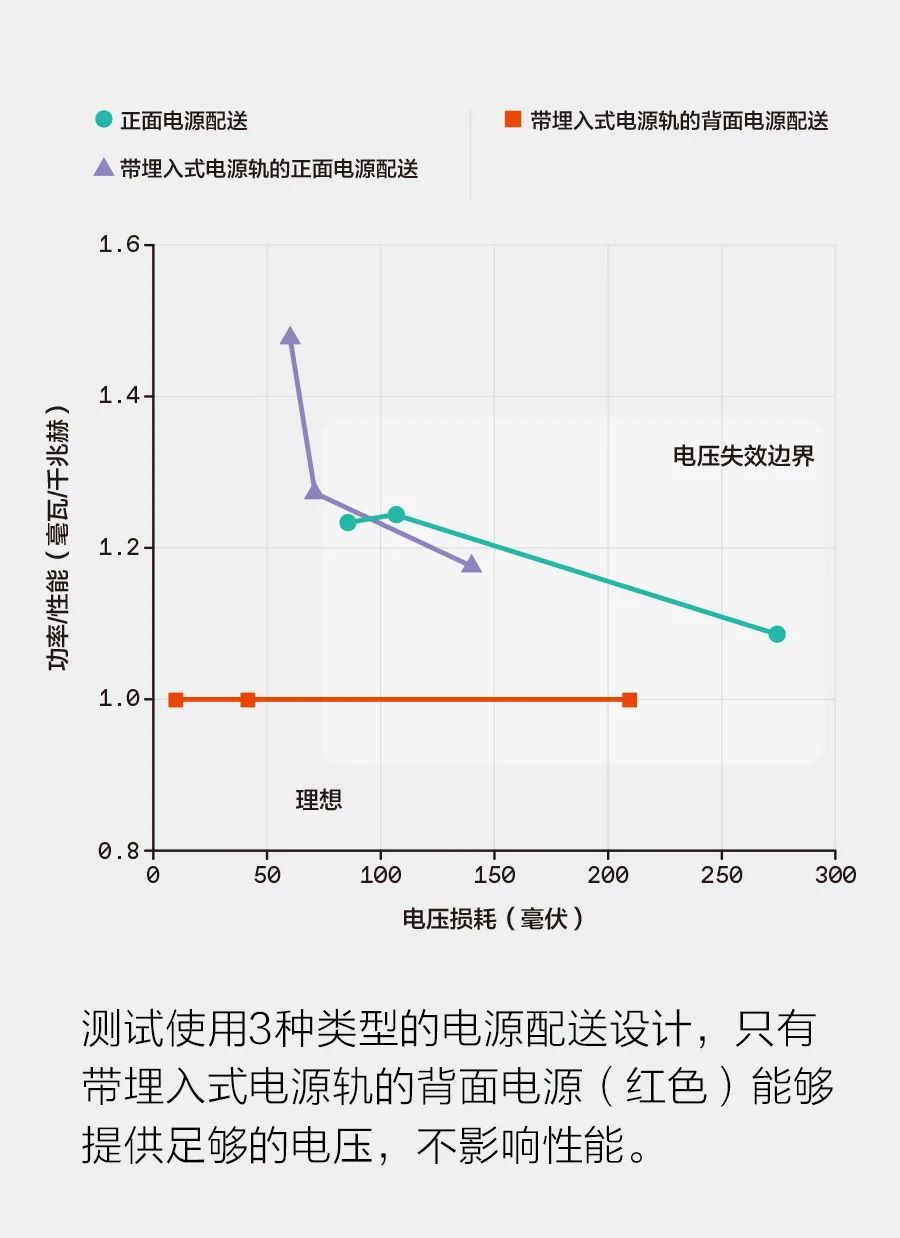

英国ARM公司的研究人员,包括作者克莱恩(Cline)和普拉萨德(Prasad),在他们的一个CPU上进行了模拟,发现BPR构建的电源网络比普通正面电源网络效率高40%。但他们也发现,即使使用正面输电的BPR,传输到晶体管的总电压也不足以维持CPU的高性能运行。幸好,Imec同步制定了一个可进一步改进电源配送的补充方案:将整个电源配送网络从芯片的正面移到背面。这种解决方案被称为“背面电源输送”,或者笼统地说是“背面金属化”。它将晶体管下方的硅减薄至500纳米以下,以打出纳米尺寸的“硅通孔”(TSV)。这些纳米硅通孔是垂直互连装置,可以通过硅的背面连接到埋入式电源轨的底部,就像数百个小型矿井一样。在晶体管和BPR下方创建纳米TSV后,就可以在芯片背面放置更多的金属层,形成完整的电源配送网络。 我们在Arm对之前的模拟进行扩展时发现,只需两层厚的背面金属就足以完成这项工作。只要能将纳米TSV的间距小于2微米,我们就可以设计一种背面电源配送网络,其效率是带有埋入式电源轨的正面电源配送网络的4倍,是传统正面电源配送网络的7倍。

我们在Arm对之前的模拟进行扩展时发现,只需两层厚的背面金属就足以完成这项工作。只要能将纳米TSV的间距小于2微米,我们就可以设计一种背面电源配送网络,其效率是带有埋入式电源轨的正面电源配送网络的4倍,是传统正面电源配送网络的7倍。

背面电源配送网络的额外优势是与信号网络物理分离,这两个网络不再争夺同一金属层资源。每个网络都有更多的空间。这也意味着,金属层特性不再需要在电源路由的偏好(又厚又宽,以获得低电阻)和信号线路的路由(又薄又窄,可连接密集的晶体管)之间寻求折衷。我们可以同时为电源路由调整背面金属层,为信号路由调整正面金属层,两全其美。在Arm的设计中,我们发现无论是传统的正面电源配送网络,还是带有埋入式电源轨的正面电源配送网络,我们都需要牺牲设计性能。但用背面电源配送网络,CPU就能够实现高频,并实现高效的电源配送。 当然,你可能想知道这个方案如何将信号和电源从封装传输到芯片。在这里,纳米TSV也是关键。可以用它们将所有输入和输出信号从芯片的正面传输到背面。这样,电源和I/O信号都可以连接到放置在背面的焊锡球上。

当然,你可能想知道这个方案如何将信号和电源从封装传输到芯片。在这里,纳米TSV也是关键。可以用它们将所有输入和输出信号从芯片的正面传输到背面。这样,电源和I/O信号都可以连接到放置在背面的焊锡球上。

仿真研究是一个很好的开端,它们展示了采用BPR背面电源配送网络的CPU设计水平潜力。但将这些技术应用于大批量制造还有很长的路要走。还有重大的材料和制造挑战需要解决。选择最佳的BPR和纳米TSV金属材料对可制造性和电效率至关重要。此外,制造BPR和纳米TSV都需要的高深宽比(深而窄)沟槽非常难。在硅衬底上可靠地蚀刻间距紧密、深而窄的沟槽,并用金属填充,对于芯片制造业来说是一种相对较新的方法,也是业界需要认真解决的问题。对于开启纳米TSV的广泛应用,开发可靠且可重复的制造工具和方法是必不可少的。

另外,采用电池供电的片上系统,如手机和其他功率受限的设计,已经拥有比我们目前讨论的更为复杂的电源配送网络。现代电源配送将芯片分成了多个电源域,可以在不同的电压下工作,甚至为了省电可以完全关闭(参见可延长电池寿命的电路)。因此,背面电源配送网络和BPR最终必须做更多工作,而不仅仅是有效传输电子。它们要精确地控制电子的去向和到达目的地的电子数量。芯片设计师在芯片级电源设计方面,不希望倒退好几步。因此,我们必须同时优化设计和制造,以确保BPR和背面电源配送网络优于今天的节能集成电路技术,或者至少与之相当。未来的计算取决于这些新的制造技术。无论你担忧数据中心的冷却费用还是智能手机每天的充电次数,耗电量都至关重要。随着我们不断缩小晶体管和集成电路的尺寸,电源配送成为一项重要的芯片挑战。如果工程师能够克服随之而来的复杂性,BPR和背面电源配送网络可能会很好地应对这一挑战。作者:Brian Cline、Divya Prasad、Eric Beyne、Odysseas Zografos

暂无评论