持续了几个月,从零开始,学习其他项目的方案和原理图,阅读相关器件的手册。终于,磕磕绊绊的完成了硬件电路方案和原理图的设计。

与射频datasheet相比,硬件的手册都特别长,短则几百页,长则上千页,硬件和软件知识夹杂在一起。看的时候真的是需要耐心,区分哪些是硬件电路设计需要的,哪些是软件设计相关的。

那硬件电路设计到底应该怎么下手呢?总结了一下,主要是三方面:

l时钟分配

l电源设计

l器件互联

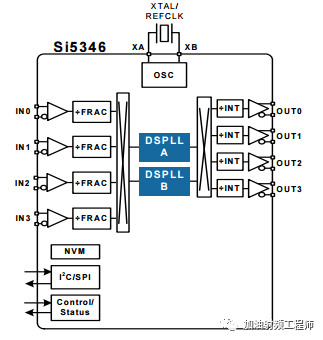

关于时钟分配,核心器件就是时钟管理芯片,如下图所示,其本质上是一个数字锁相环,可以多路输出。和射频锁相环一样,厂家也提供设计软件,协助设计人员进行寄存器配置。所以,时钟分配的难点,在于如何确定各路时钟的频率。

ADC,DAC,SoC上的PS-CLK和GTX等等,都需要时钟。比如说,如果你要选用千兆以太网,PS-CLK选为50MHz,可能是比较合适的。因为FPGA内部的PLL都是整数分频的,选50MHz时,FPGA可以产生PHY芯片需要的125MHz。而ADC,DAC,GTX的时钟选择,相互制约,选择时还需要咨询算法人员(与其符号率、编码方式等有关,这个我也还没搞清楚,直接采用的是算法人员推荐的频率)。

关于电源设计,除给各个器件供电外,还要保证FPGA的上电时序满足要求。FPGA只有按照一定的时序上电,才能保证其消耗最小的电流,且I/O在上电过程中为三态状态。这可以通过单片机控制实现,也可以利用电源芯片的PGOOD功能。

FPGA等芯片的功耗的估计都比较难,因为其和射频器件不一样,它的功耗和其工作状态有很大的关系。而在最后算法等出来之前,可能连FPGA设计人员都不清楚其功耗是怎样。所以,设计时,先用厂家提供的功耗计算软件进行估算。然后,在硬件上做兼容,先按大电流设计,实际过程中按照需求调整,以保证电源效率。

关于器件互联,主要是指FPGA与Flash,DDR,PHY芯片,ADC,DAC等之间的互联。而这些互联都遵循一定的规则,FPGA都有明确的规定,需要仔细阅读FPGA相关的应用文档。

PS:

一直不明白,为什么硬件PCB上的供电,大部分都是用电源平面,而射频,就是用宽度为mm级的线就行了?

我想大致原因,可能是:

数字器件在运行过程中,瞬态电流会很大,而数字器件对其供电误差的容忍度很小,可能只有0.02V左右,所以需要大的电源平面,这样电阻就小,保证电流瞬态变化时,其供电电压仍在误差范围内。当然,这还需要去耦电容的帮忙。

而射频器件,电流就小很多,mA级,而且,对供电误差不太敏感。5V的器件,给个4.8V,可能也能正常工作。

所以,数字PCB需要采用电源平面,而射频只需用微带线连接即可。

暂无评论