在功率Mosfet设计中,许多工程师被要求降低RDS(ON)与栅源偏置电压Vcs,RDS(ON)是Mosfet在导通状态下的电阻,直接影响电子器件的功耗及效率。

1、选择合适的MOSFET器件

低RDS(ON)器件:选择专门设计为低导通电阻的 MOSFET,这些器件通常具有更高的沟道迁移率和更低的导通电阻。

优化沟道设计:选择沟道长度较短、沟道宽度较大的 MOSFET,可以显著降低RDS(ON)。

2、优化栅源偏置电压Vcs

提高Vcs:RDS(ON)通常随着Vcs的增加而减小,因为更高的Vcs会增强沟道导电性。确保Vcs工作在MOSFET的饱和区(通常Vcs接近或略高于阈值电压Vth)。

避免过高的Vcs:虽然提高Vcs可降低RDS(ON),但过高的Vcs会导致栅极氧化层击穿或增加开关损耗,因此需要在RDS(ON)和可靠性之间找到平衡。

3、改进器件结构和材料

使用先进工艺:采用更先进的半导体工艺(如沟槽栅极结构或超级结技术),可以显著降低RDS(ON)。

宽禁带半导体材料:使用碳化硅(SiC)或氮化镓(GaN)等宽禁带半导体材料,这些材料具有更高的电子迁移率和更低的导通电阻。

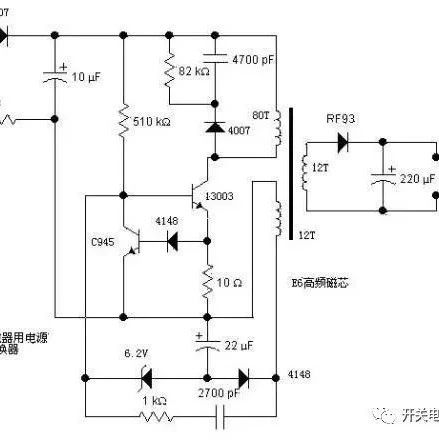

4、优化驱动电路

快速开关驱动:使用高效的栅极驱动电路,确保MOSFET能够快速开关,减少导通和关断过程中的损耗。

降低栅极电阻Rc:减少栅极电阻可提高Vcs的上升速度,从而降低RDS(ON)。

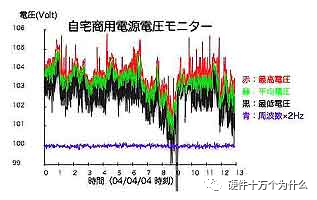

5、温度管理

降低工作温度:RDS(ON)会随着温度的升高而增加,因此良好的散热设计可以降低RDS(ON)。

选择温度系数低的器件:某些MOSFET具有较低的温度系数,可以在高温下保持较低的RDS(ON)。

6、并联MOSFET

多器件并联:将多个MOSFET并联可以降低总导通电阻,但需要注意均流问题,确保每个器件的电流分布均匀。

7、优化布局设计

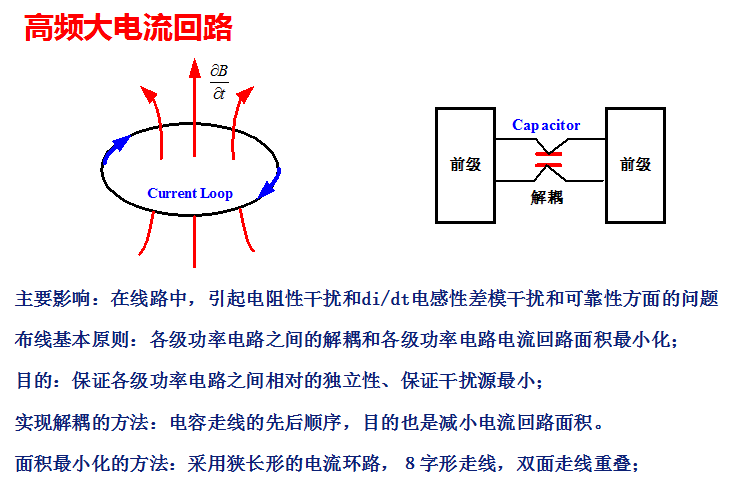

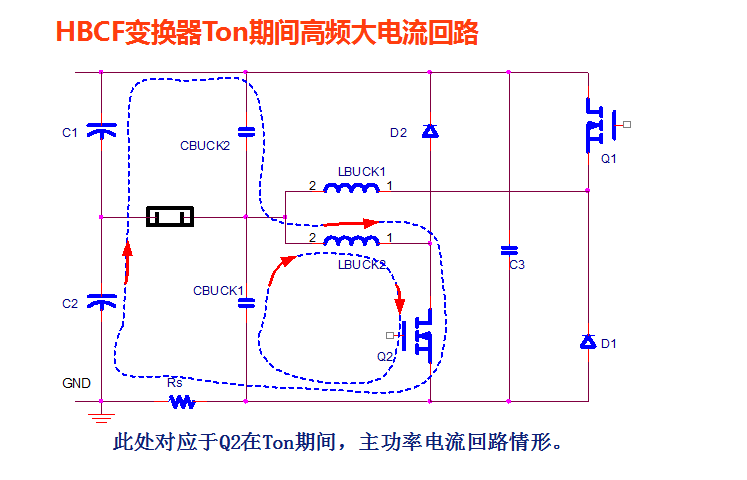

减小寄生电阻:优化PCB布局,减小源极和漏极的寄生电阻(如引线电阻和焊盘电阻),从而降低总导通电阻。

降低电感效应:减少布线电感,避免在高频开关时产生额外的损耗。

8、动态调整Vcs

自适应偏置:在某些应用中,可以通过动态调整Vcs来优化RDS(ON)。

9、仿真与测试

仿真优化:使用仿真工具(如SPICE)分析RDS(ON)与Vcs的关系,找到最佳工作点。

实际测试:通过实际测试验证仿真结果,确保设计的可靠性和性能。

本文凡亿教育原创文章,转载请注明来源!

暂无评论