PA(Power Amplifier,功率放大器)是通信系统的重要组成模块,负责将射频信号的放大与功率输出。PA的性能及可靠性对整个发射系统有重要的影响。

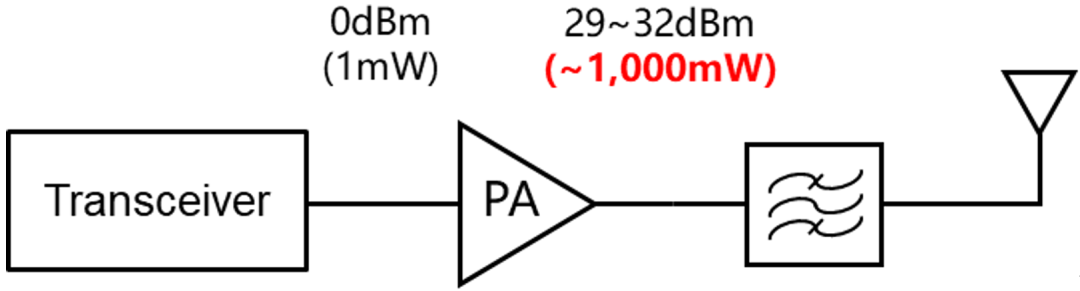

在手机通信系统中,PA的输出信号约为29~32 dBm (约1,000 mW)的大功率,对比收发机芯片0dBm (1mW)左右的功率输出 ,PA输出功率大1000倍。 图1:典型手机通信系统链路

图1:典型手机通信系统链路

高功率、高功耗的应用也对PA可靠性提出挑战。在系统应用中,“烧PA”是工程师讨论中的热点话题。

PA设计常用的半导体工艺为GaAs HBT、GaAs pHEMT、SOI CMOS、Bulk CMOS(体硅CMOS)。其中,GaAs HBT因为其功率密度大,成本低(相较于GaAs pHEMT),成为射频功率放大器功率输出级的首选工艺。

PA设计常用的半导体工艺为GaAs HBT、GaAs pHEMT、SOI CMOS、Bulk CMOS(体硅CMOS)。其中,GaAs HBT因为其功率密度大,成本低(相较于GaAs pHEMT),成为射频功率放大器功率输出级的首选工艺。

HBT器件有三个极限参数,分别为:

集电极最大允许电流Icmax

集电极最大允许热耗散功率

集电极-发射极反向击穿电压BVCEO

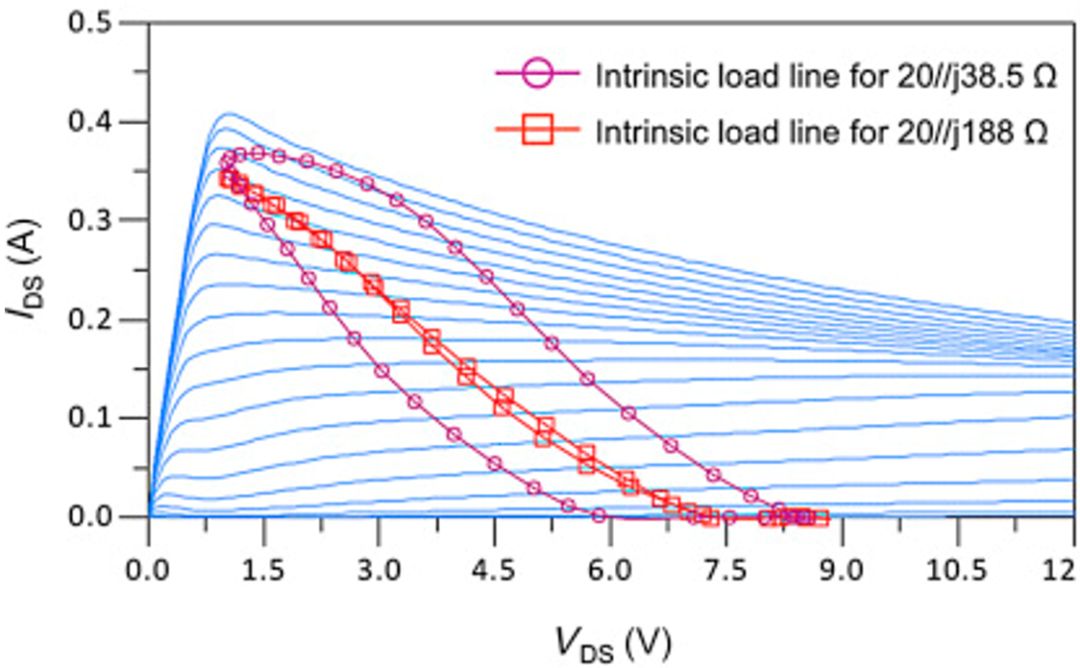

在实际工作中,需要保证器件的最大工作电路、耗散功率、最大电压,在额定范围内。 对于射频PA的HBT器件,输出晶体管的集电极有最大电压及电流摆幅。此点电压与电流之间的摆幅随时间变化,为了更好的表征电压与电流之间的关系,通常用Loadline(负载线)的方式,将电压与电流画在同一幅图中,如图2所示。

对于射频PA的HBT器件,输出晶体管的集电极有最大电压及电流摆幅。此点电压与电流之间的摆幅随时间变化,为了更好的表征电压与电流之间的关系,通常用Loadline(负载线)的方式,将电压与电流画在同一幅图中,如图2所示。 图2:一款PA的典型的动态负载线

图2:一款PA的典型的动态负载线

晶体管的负载线反应了在不同的负载下,晶体管电压与电流间的相互关系,一般画在DC-IV曲线上。在负载线中:

负载线的斜率反应了负载阻抗的大小。

实际电路中,由于负载虚部的存在,会形成电压/电流相位差,可能使得负载线表现为中空的环形。

直流工作点的选择(电压及电流),对负载线的摆幅有影响。

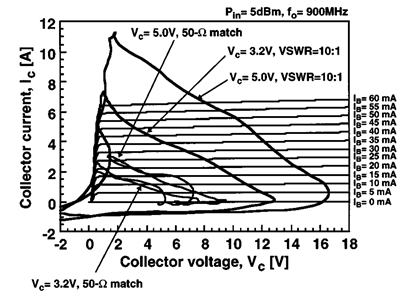

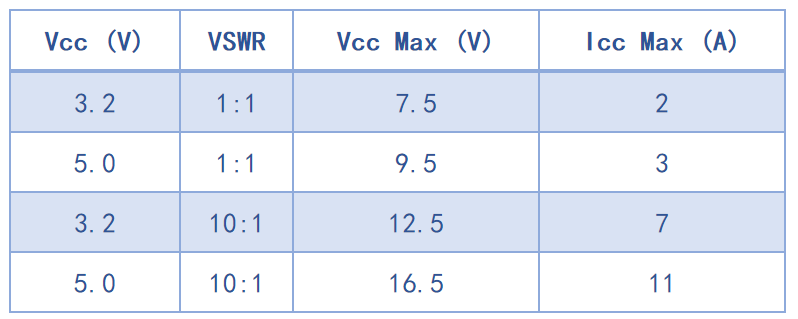

在PA工作中,由于高电源电压、高VSWR的存在,会让PA输出电压、电流摆幅增大。图3为一个典型的功率放大器,分别是在3.2V及5V偏置电压下,50Ω及VSWR=10:1下的动态负载线 [2]。可以看到,在大电压及VSWR下,PA将需要承受更大的电压及电流摆幅。当电压及电流摆幅超过器件的耐受值时,就会造成器件烧毁。

图3:不同电压及VSWR下,PA动态负载线的变化

图3:不同电压及VSWR下,PA动态负载线的变化

PA需要合理设计,确保满足Ruggedness需求。

PA需要合理设计,确保满足Ruggedness需求。

电流设计保障

需要合理设计器件的尺寸,确保在各个条件下,器件所通过的最大电流,小于器件的最大耐受电流。

在对通流的设计中,需要着重注意的是,PA末级并联了多个晶体管器件,需要保证电流均分在整个器件中,而不是所有电流集中于某一个器件,将器件烧毁。

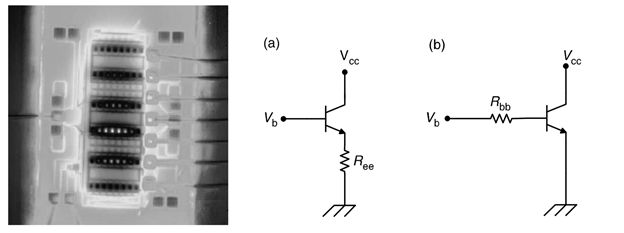

由于HBT器件开启电压随温度升高而降低,过大的电流会降低开启电压,同时使电流进一步增大,直到器件烧毁。这种效应叫做Thermal Run-away,是电流烧毁中一种常见形式。

为了防止Thermal Run-way的发生,需要在晶体管的Base端或者Emitter端加入Ballast电阻。Ballast电阻的存在,使得电流变大的过程中,Vbe电压会减小,防止电流的进一步增大[3]。 图4:PA的热分布不均(左),及Ballast电阻的设计

图4:PA的热分布不均(左),及Ballast电阻的设计

电压设计保障

对于电压防护,一般采用在末级晶体管Collector并联放置二极管串的方式进行稳压,使得输出摆幅稳定在二极管串的开启电压。

在电压防护电路设计中需要注意,一定要保证防护电路放置位置的对称性,确保所有器件的电压摆幅得到保护。

电路设计保障为了保护射频PA工作再合理的工作范围,设计公司还会对PA加入过压保护(OVP)、过流保护(OCP)、过驱动保护(ODP)等保护电路。在电压、电流及输入信号超过额定范围后,对以上参数进行钳位保护。 由于PA可靠性难以靠仿真来准确设计,PA设计完成后,必须通过完整的Ruggedness测试,来确保PA的可靠性。

由于PA可靠性难以靠仿真来准确设计,PA设计完成后,必须通过完整的Ruggedness测试,来确保PA的可靠性。

完整的Ruggedness测试环境如下图所示: 图5:Ruggedness测试环境

图5:Ruggedness测试环境

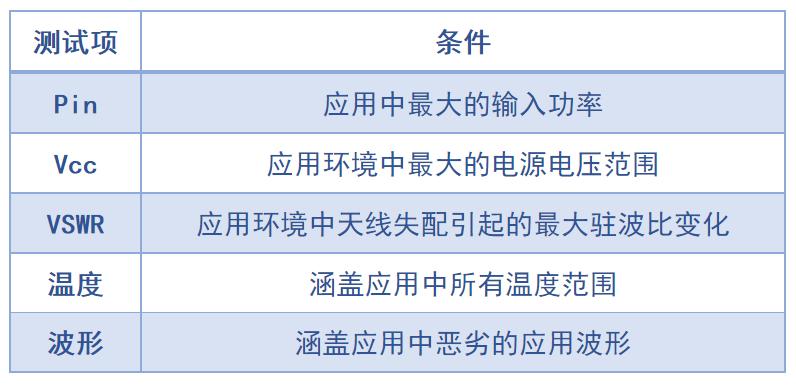

Ruggedness测试需要涵盖以下测试条件:

以上测试项需要交叉组合,确保任意条件下,PA均不会有Ruggedness问题。

由于半导体器件的最大击穿电压BVCEO随温度降低而降低,PA增益随温度降低而升高,一般Ruggedness最恶劣的点发生在低温。所以,一般低温下,最大输入功率、最高电压、最大VSWR下,为Ruggedness最差条件。 虽然合格的PA在出厂前,进行了完整的Ruggedness测试,但在应用中仍然需要对应用环境加以注意,确保Ruggedness在应用中得到保障。应用中需要的主要保障如下:

虽然合格的PA在出厂前,进行了完整的Ruggedness测试,但在应用中仍然需要对应用环境加以注意,确保Ruggedness在应用中得到保障。应用中需要的主要保障如下:

适当控制电源电压

由图3所示,PA在低电压应用时,有较小的电压及电流摆幅,PA的Ruggedness将得到较好的保障。所以在应用中,适当控制电压电压,尽可能使用较低的电源电压,有助于提升器件的Ruggedness。

适当控制输出功率

大功率输出时,PA输出将有更大的电压电流摆幅。在应用允许范围内,适应控制输出功率,将有助于Ruggedness提升。

注意电源完整性及信号时序

手机是一个相当复杂的系统,涉及到多个模块之间的联动。在应用中,需要着重注意电源完整性(是否有过高的电压脉冲)、偏置控制信号的时序、输入信号的大小及时序,来确保PA是被工作在正常的状态。

PA Ruggedness设计是一个复杂工程,与器件物理、电路设计、系统应用均相关。在PA设计中,一定要对Ruggedness仔细设计,才可以确保手机在各种环境应用中,均不会出现“烧片”。

暂无评论