凡亿教育-小羊

凡事用心,一起进步打开APP

公司名片晶振电路的PCB走线规范指南,必看!

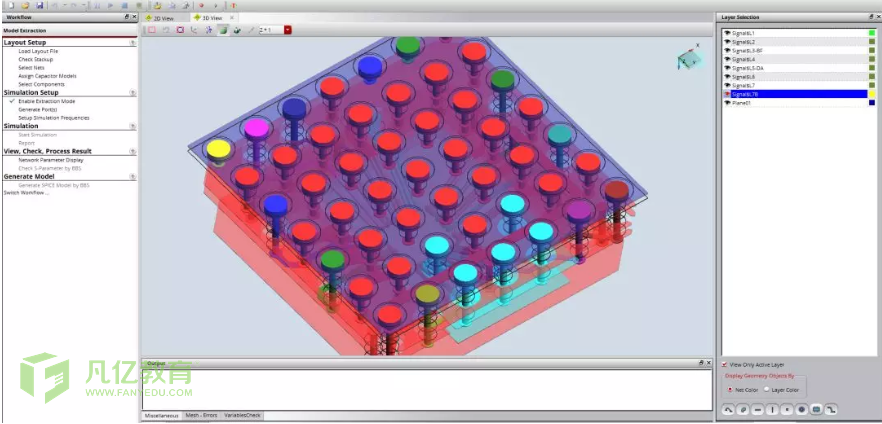

在高频电路设计中,晶振电路的PCB走线布局直接影响信号完整性与系统稳定性。工程师需要学习,设计出良好的PCB走线,以此确保晶振电路的正常运行。下面将简短说说走线规范,帮助你规避常见缺陷。

1. 晶振输入/输出端走线

XTLI/XTLO引脚:走线长度≤15mm,避免锐角(弯折角度≥45°),减少分布电容与电磁干扰。

XTLO特化:因驱动电流大,需优先缩短路径,降低寄生电感。

2. 电容地线设计

无地线层双面板:电容地线使用≥20mil宽短线,直接连接至晶振最近DGND引脚,过孔≤1个。

禁止共享地线:晶振电容地线不得与电源地、数字地混用,避免地弹噪声。

3. 晶振外壳接地

物理接地:晶振外壳通过金属化过孔或短线直接连接至PCB地平面,屏蔽外部干扰。

避免悬空:未接地外壳可能导致辐射超标,影响EMC性能。

4. XTLO引脚匹配电阻

阻值选择:在XTLO与晶振/电容节点间串联100Ω电阻,抑制振荡信号反射,匹配驱动器输出阻抗。

位置优化:电阻靠近XTLO引脚放置,缩短寄生电感路径。

5. 晶振电容接地路径

直接连接:电容地线直接焊至Modem的GND引脚,禁止通过地线区域或走线连接。

路径长度:接地路径≤5mm,减少地弹对晶振频率稳定性的影响。

本文凡亿教育原创文章,转载请注明来源!

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表凡亿课堂立场。文章及其配图仅供工程师学习之用,如有内容图片侵权或者其他问题,请联系本站作侵删。

相关阅读

进入分区查看更多精彩内容>

暂无评论