其实我们对 DAQ 的要求是既要,又要,还要,但是物理的限制是,这个不行,那个不能,其实 DAQ设计 就是这样平衡或者是妥协的艺术。我敢写是因为有 TI 的一篇文章打底,而且在我的研究中确实发现是这样的用的,其实就是在使用了 FPGA 里面的时钟缓冲器。 其次就是尽量在允许的范围内是多使用 MCU,MPU 这些处理器,尽量不碰 FPGA,其实纯粹是因为 FPGA 不是那么熟悉下妥协的结果。(🤣)

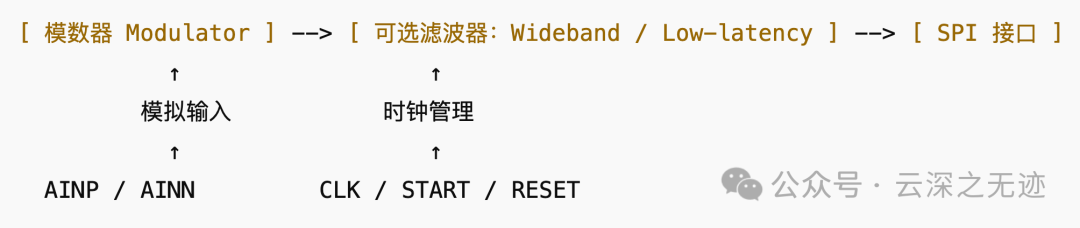

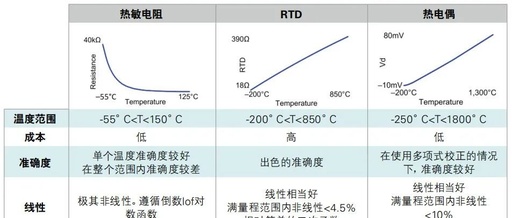

其次就是尽量在允许的范围内是多使用 MCU,MPU 这些处理器,尽量不碰 FPGA,其实纯粹是因为 FPGA 不是那么熟悉下妥协的结果。(🤣) 这个片子其实在大众的视野里面出现的不多,不是非常明星的赶脚,但是内部设计以及相关的文档支持是把它放在了一个非常有用的等级,至少是我看到的这样。我想先介绍一下我们常见和常用的 ADC:分别是逐次逼近型ADC(SAR ADC)和Σ-Δ ADC是两种常见的模数转换器架构,它们在设计原理、性能特点和应用场景上有显著差异。逐次逼近型ADC(SAR ADC)采用二进制搜索算法,通过逐次比较输入电压与参考电压,逐步逼近最终数字值;使用了比较器、逐次逼近寄存器(SAR)、数模转换器(DAC)。流程:采样→保持→逐次比较→输出结果。Σ-Δ ADC(Sigma-Delta ADC)基于过采样和噪声整形技术,将高频量化噪声推至目标频段外,通过数字滤波提取有效信号;调制器(Modulator)、数字滤波器(如Sinc滤波器)。典型流程:过采样→噪声整形→数字滤波→抽取(降低数据率)。

这个片子其实在大众的视野里面出现的不多,不是非常明星的赶脚,但是内部设计以及相关的文档支持是把它放在了一个非常有用的等级,至少是我看到的这样。我想先介绍一下我们常见和常用的 ADC:分别是逐次逼近型ADC(SAR ADC)和Σ-Δ ADC是两种常见的模数转换器架构,它们在设计原理、性能特点和应用场景上有显著差异。逐次逼近型ADC(SAR ADC)采用二进制搜索算法,通过逐次比较输入电压与参考电压,逐步逼近最终数字值;使用了比较器、逐次逼近寄存器(SAR)、数模转换器(DAC)。流程:采样→保持→逐次比较→输出结果。Σ-Δ ADC(Sigma-Delta ADC)基于过采样和噪声整形技术,将高频量化噪声推至目标频段外,通过数字滤波提取有效信号;调制器(Modulator)、数字滤波器(如Sinc滤波器)。典型流程:过采样→噪声整形→数字滤波→抽取(降低数据率)。 SAR 的最大优势我觉得是采样率,为什么华为之前出的 ADC,那么多人关注,就是因为 SAR 构架做到了 2M(当然 ADI 早就做出来)。华为海思新发ADC:24bit 2M SAR构架ADC其次就是成本低,只是说位数的时候:

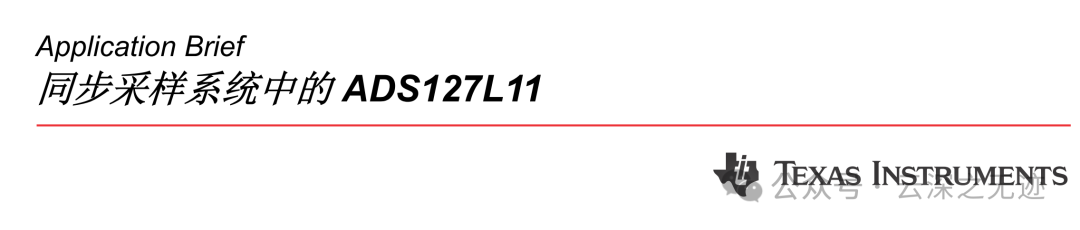

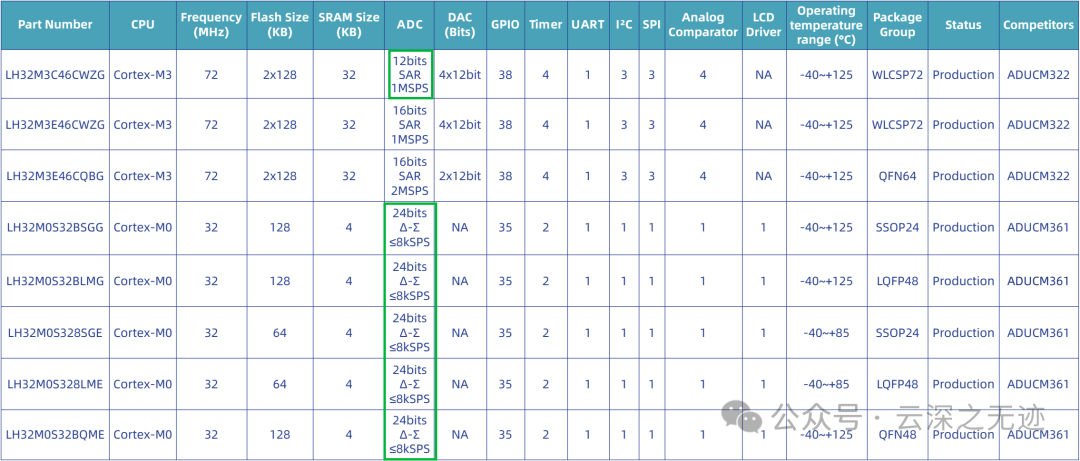

SAR 的最大优势我觉得是采样率,为什么华为之前出的 ADC,那么多人关注,就是因为 SAR 构架做到了 2M(当然 ADI 早就做出来)。华为海思新发ADC:24bit 2M SAR构架ADC其次就是成本低,只是说位数的时候: CW32 以及所有的 M0 都是 SAR

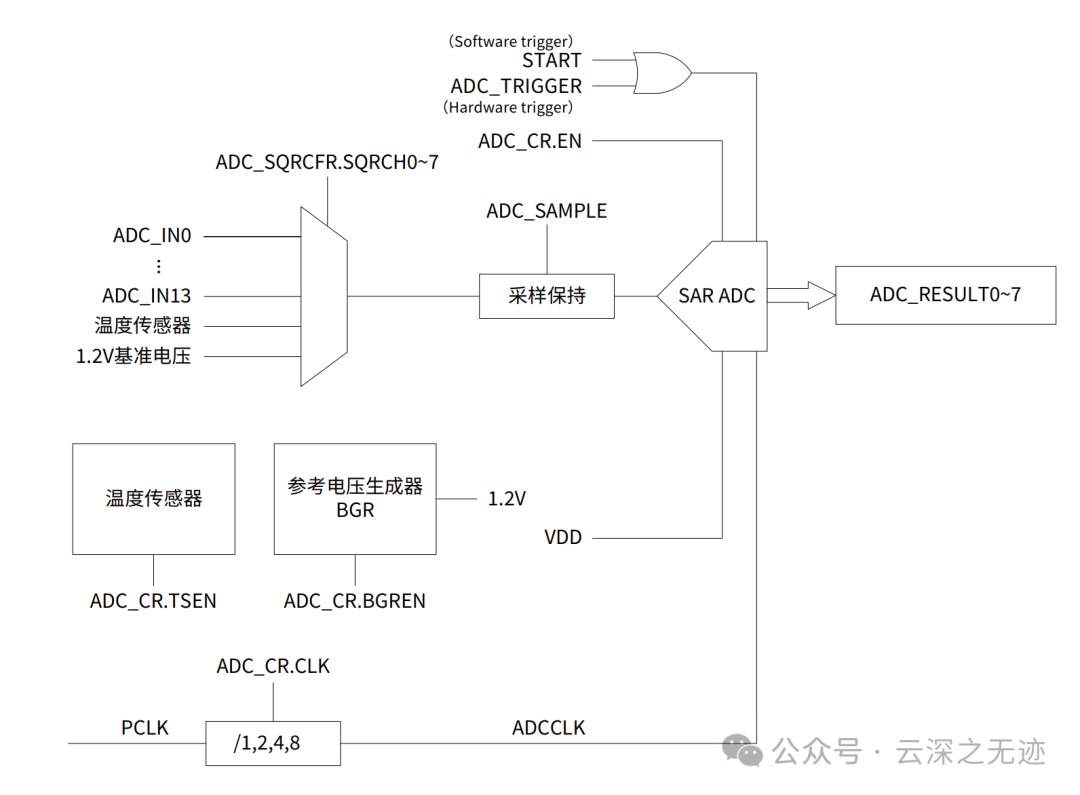

CW32 以及所有的 M0 都是 SAR 当然还有一些是想要一个高精度的ADC 产品,就像领慧的这个就是,内置的是积分 ADC,ADI 的想不起来了。

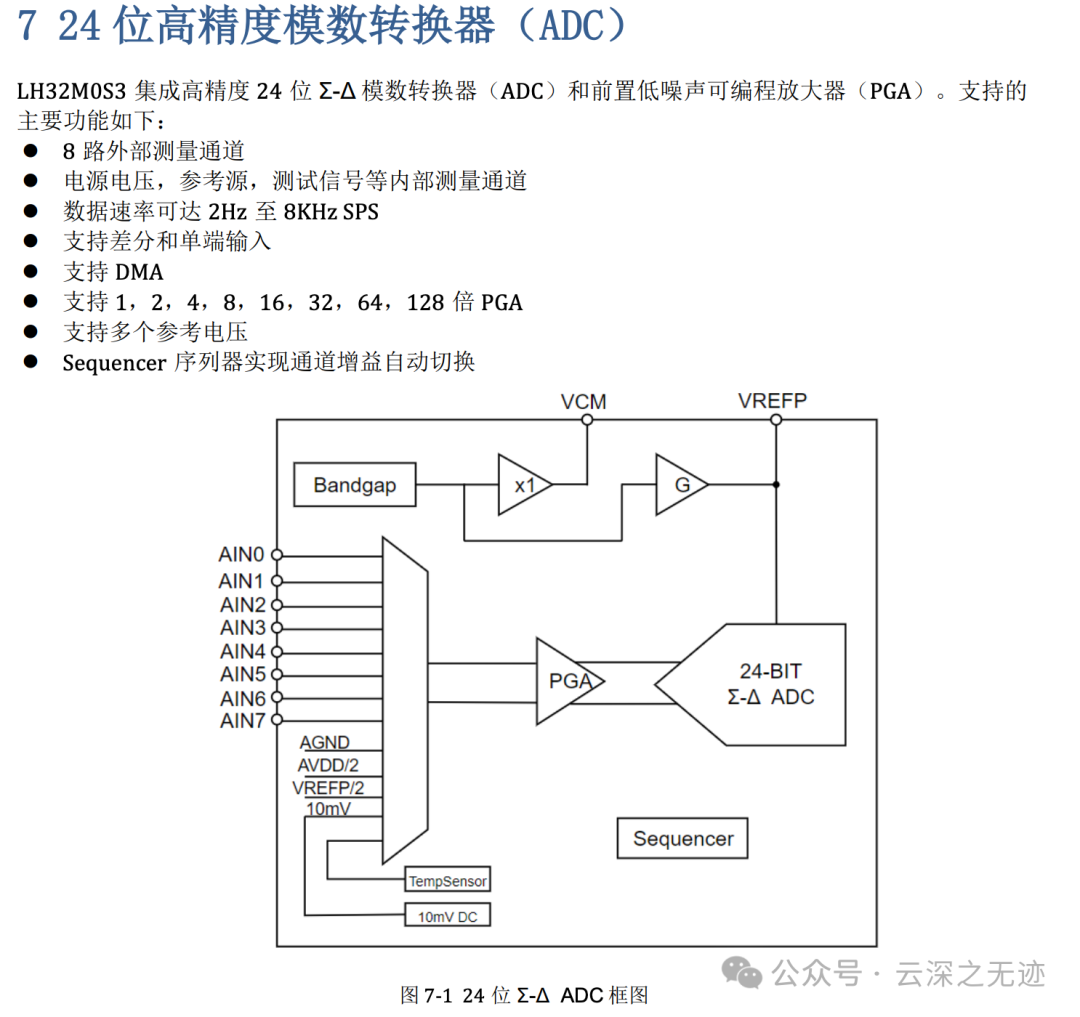

当然还有一些是想要一个高精度的ADC 产品,就像领慧的这个就是,内置的是积分 ADC,ADI 的想不起来了。 找到了

找到了 总之就是 SAR 的位数和速度之间有取舍超高分辨率需求:精密传感器测量(如称重、压力传感器)。低频信号处理:温度、湿度、气体传感器(通常输出低频信号)。抗噪声能力:工业现场存在强电磁干扰的环境。直接接口传感器:无需复杂前端调理(部分Σ-Δ ADC内置PGA)。以上就是积分 ADC 的优势了,若需16位以上高分辨率(如传感器直接接口),选择Σ-Δ ADC。若12-16位足够且需高速采样,选择SAR ADC。更多的我就不写了,总之是各有千秋。

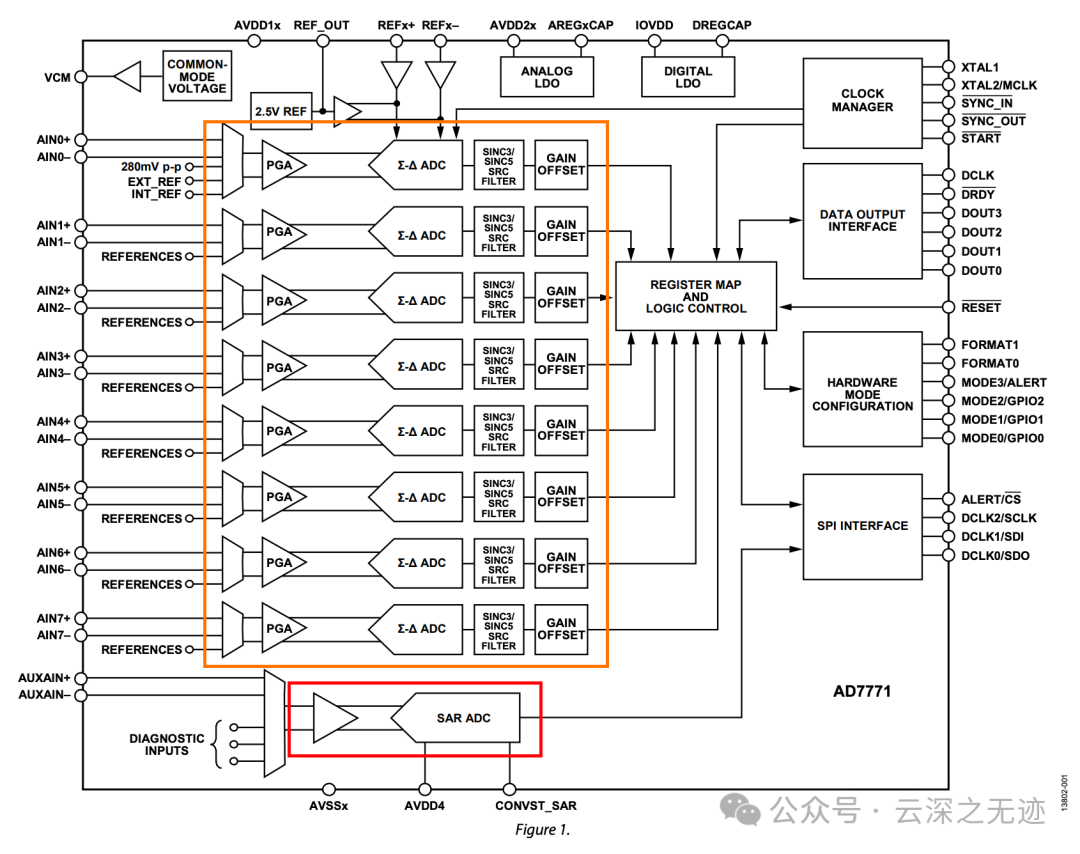

总之就是 SAR 的位数和速度之间有取舍超高分辨率需求:精密传感器测量(如称重、压力传感器)。低频信号处理:温度、湿度、气体传感器(通常输出低频信号)。抗噪声能力:工业现场存在强电磁干扰的环境。直接接口传感器:无需复杂前端调理(部分Σ-Δ ADC内置PGA)。以上就是积分 ADC 的优势了,若需16位以上高分辨率(如传感器直接接口),选择Σ-Δ ADC。若12-16位足够且需高速采样,选择SAR ADC。更多的我就不写了,总之是各有千秋。 比如 AD7771,为了伺候好积分 ADC 还加了一个 SAR 来做监测,也算是物尽其用了。

比如 AD7771,为了伺候好积分 ADC 还加了一个 SAR 来做监测,也算是物尽其用了。

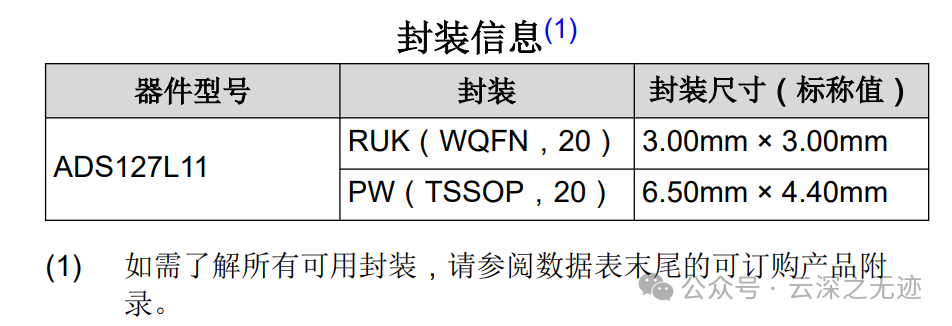

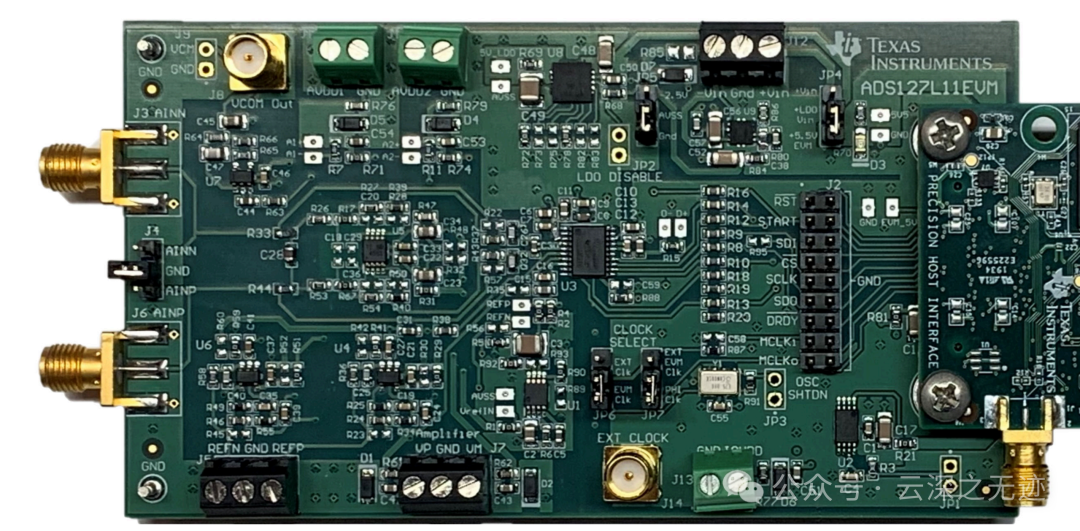

我们今天的主角就是这个死样子

我们今天的主角就是这个死样子 还有个小的,如果让我用,我会选大的,小的太😖了。

还有个小的,如果让我用,我会选大的,小的太😖了。 好拉线

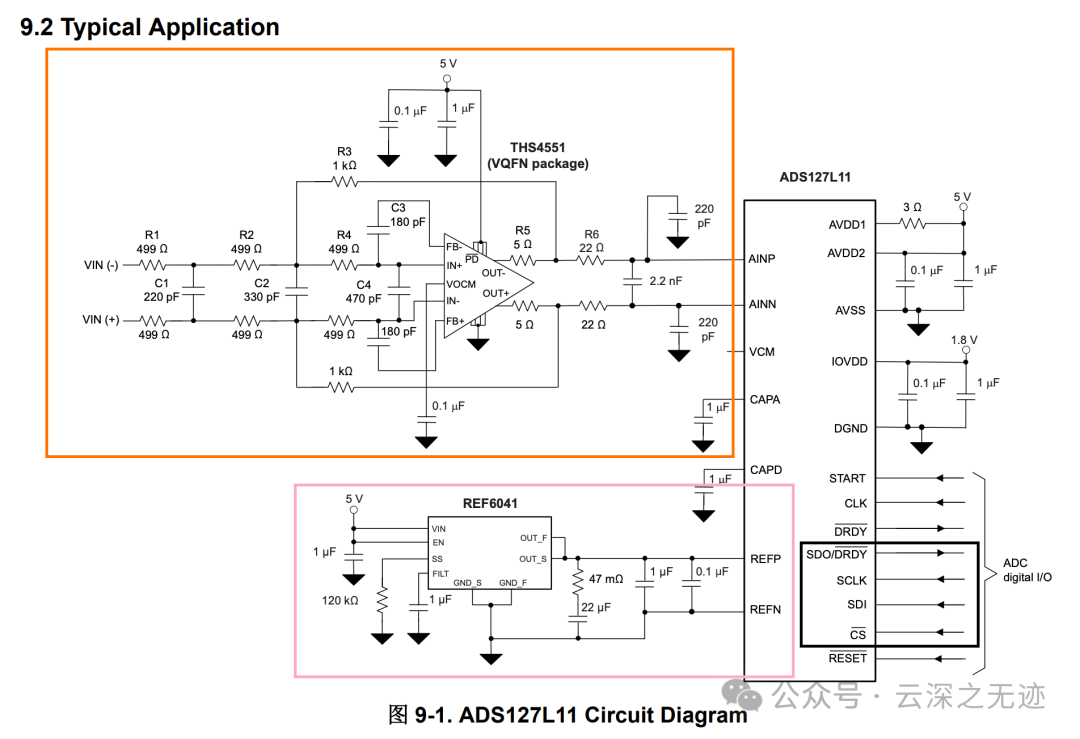

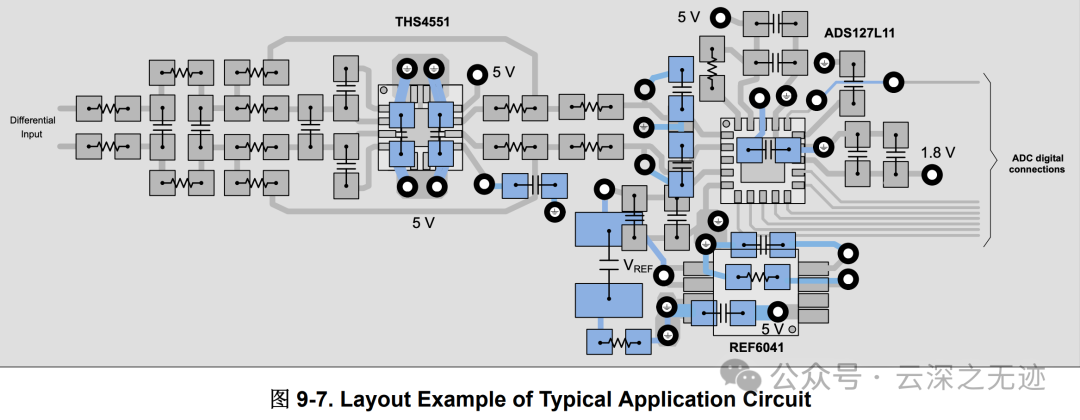

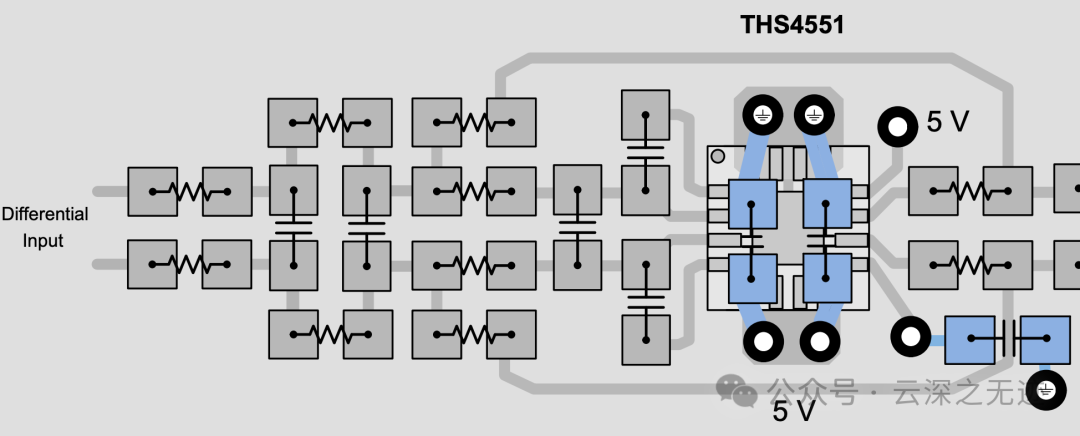

好拉线 顶级大厂的 Layout 实力,爱死

顶级大厂的 Layout 实力,爱死 非常的对称

非常的对称 做一个!

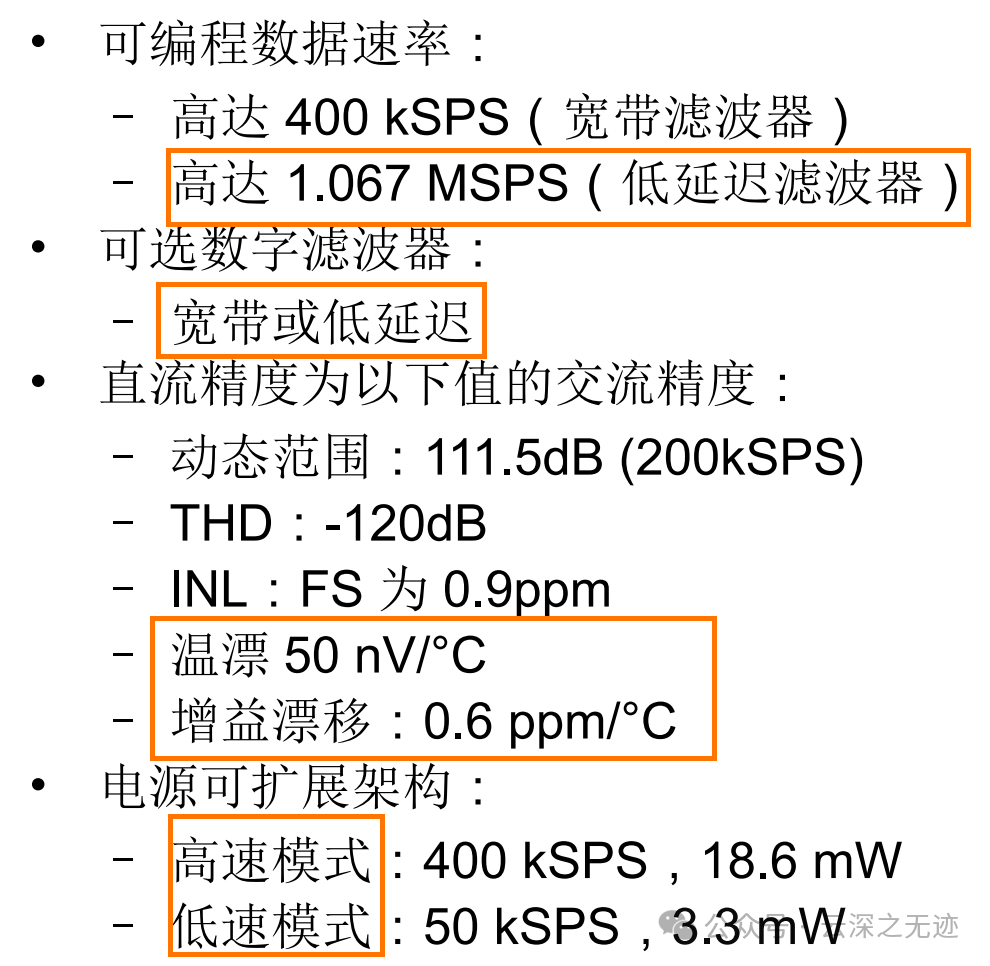

做一个! 它的参数是好看的,甚至有点小超频的感觉到 1M。后面装逼的名词是:

它的参数是好看的,甚至有点小超频的感觉到 1M。后面装逼的名词是: 需在“低功耗待机”与“高精度采样”间切换时,这种架构非常有价值。反正就是又要准又要省电,因为ADC 最耗电就是要看转换时的消耗。

需在“低功耗待机”与“高精度采样”间切换时,这种架构非常有价值。反正就是又要准又要省电,因为ADC 最耗电就是要看转换时的消耗。 构架也是流式的

构架也是流式的 从前到后

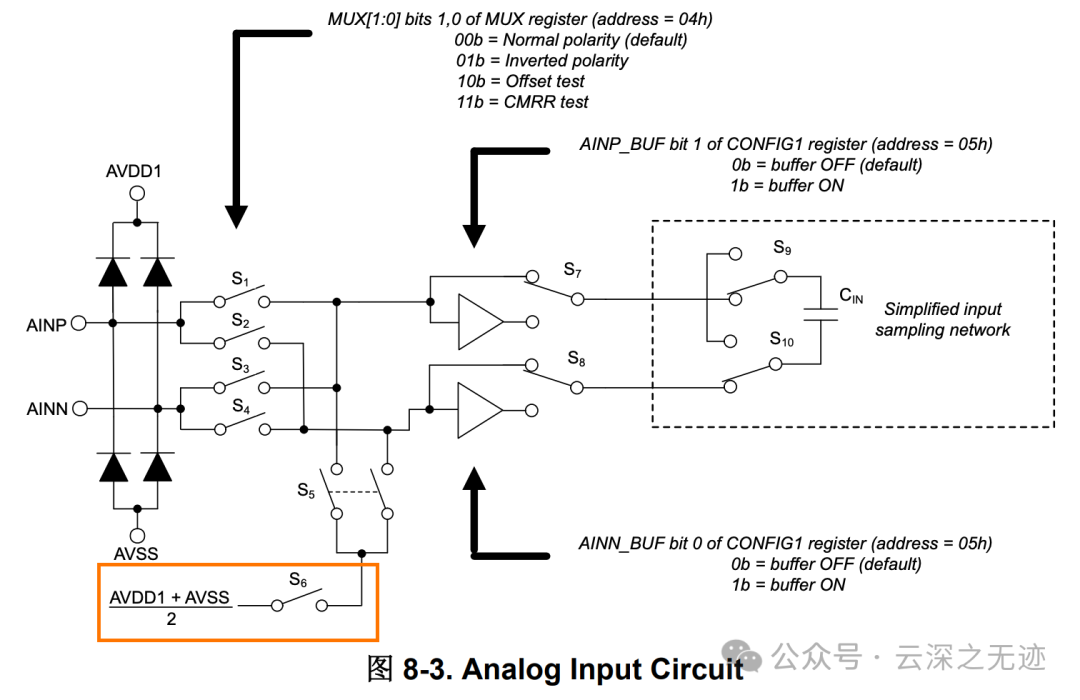

从前到后 有些信号不好调理还设计了 VCM,可以把电平托举到合适的位置。终于开始了!同步要求:所有 ADC 需使用同一时钟源(保证采样时间一致)

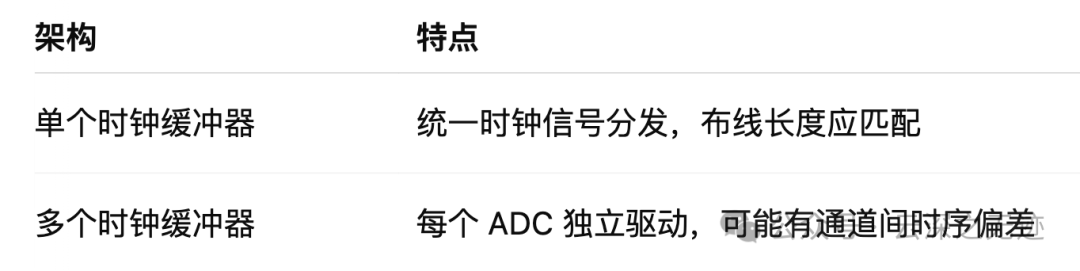

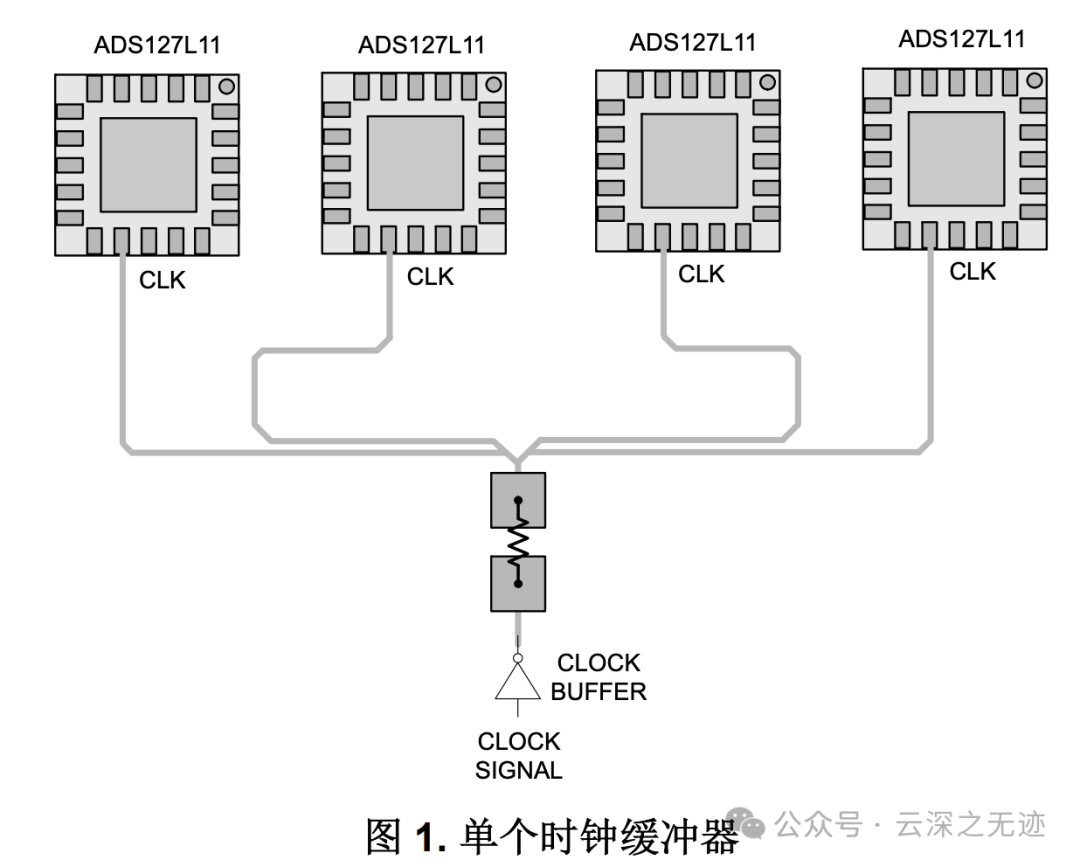

有些信号不好调理还设计了 VCM,可以把电平托举到合适的位置。终于开始了!同步要求:所有 ADC 需使用同一时钟源(保证采样时间一致) 单个系统简单,第一种是主流

单个系统简单,第一种是主流

多个器件也是有细微的同步差别在布线的时候也要一致:时钟线长度匹配至 ±1inch(150ps 精度);时钟上升沿越快,采样偏差越小(推荐 < 1ns);必要时加源端匹配电阻(阻尼振铃)。会因为工艺差异引起调制器延迟微小不同,上升时间 < 1ns 有助降低偏差。积分 ADC 内部的 抗混叠模拟滤波器(AAF)有群延迟;因为数字滤波器为线性相位(恒定群延迟),所以AAF 可能引入通带内非线性群延迟,影响高频同步精度。由于芯片内部电路的制造差异,多个 ADC 在上电之后并不会自动保持“完全一致的采样时刻”。

多个器件也是有细微的同步差别在布线的时候也要一致:时钟线长度匹配至 ±1inch(150ps 精度);时钟上升沿越快,采样偏差越小(推荐 < 1ns);必要时加源端匹配电阻(阻尼振铃)。会因为工艺差异引起调制器延迟微小不同,上升时间 < 1ns 有助降低偏差。积分 ADC 内部的 抗混叠模拟滤波器(AAF)有群延迟;因为数字滤波器为线性相位(恒定群延迟),所以AAF 可能引入通带内非线性群延迟,影响高频同步精度。由于芯片内部电路的制造差异,多个 ADC 在上电之后并不会自动保持“完全一致的采样时刻”。

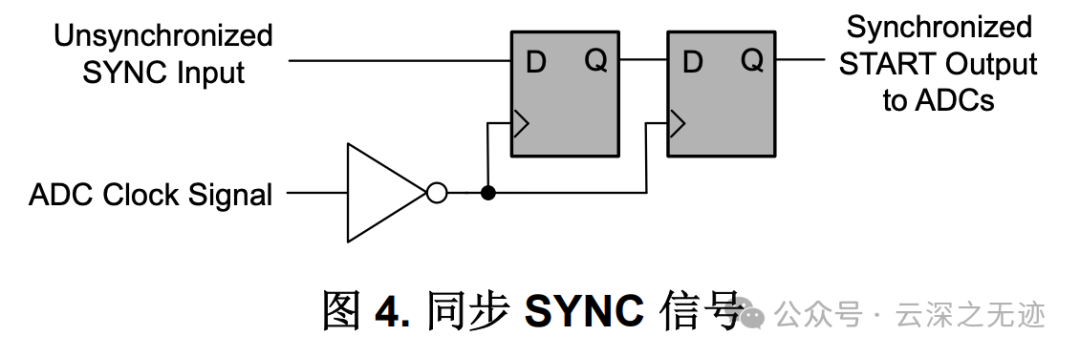

所以,在实际应用中,必须手动同步它们 —— 否则多个通道的数据是“错位”的。使用 START 引脚 控制同步:把多个 ADC 的 START 引脚连接在一起,外部用一个控制信号线拉高 START。当 START 被拉高后,ADC 会在 下一个时钟上升沿 启动采样,从而完成同步。为了避免由于“时钟边沿”模糊导致的误差,一定要在“时钟的下降沿”把 START 拉高,这样时钟的上升沿来临时,采样启动时间才“干净整齐”。另外START 引脚之间布线长度差异没关系太大,只要差异小于 ½ 时钟周期,因为它会在下一个时钟沿重新锁存对齐。 还有一种异步 SYNC 信号同步方案(用 D 触发器同步)。有时候你的同步控制信号(比如 MCU 输出)不是和 ADC 使用的时钟同步的。如果你直接把这个异步信号连到 ADC,可能会造成采样误差高达 一个完整时钟周期,因为它不是精确对齐的。所以推荐用 SN74AUP2G79 这样的 D 型触发器:把异步信号送入触发器用 ADC 的时钟来驱动触发器触发器输出的信号就跟 ADC 的时钟对齐了,确保所有 ADC 精确同步到同一时钟周期。START 引脚并联 → 使用统一控制脉冲同步所有 ADC;START 信号应在时钟下降沿被置高,避免不确定延迟。数据拿到了,传出去,SPI菊花链,所有 ADC 共享 4 条 SPI 线(CS/SCLK/SDI/SDO),这样可以节省主控 IO 资源。

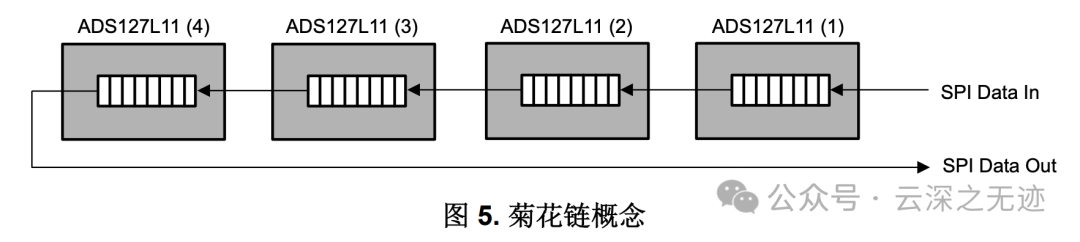

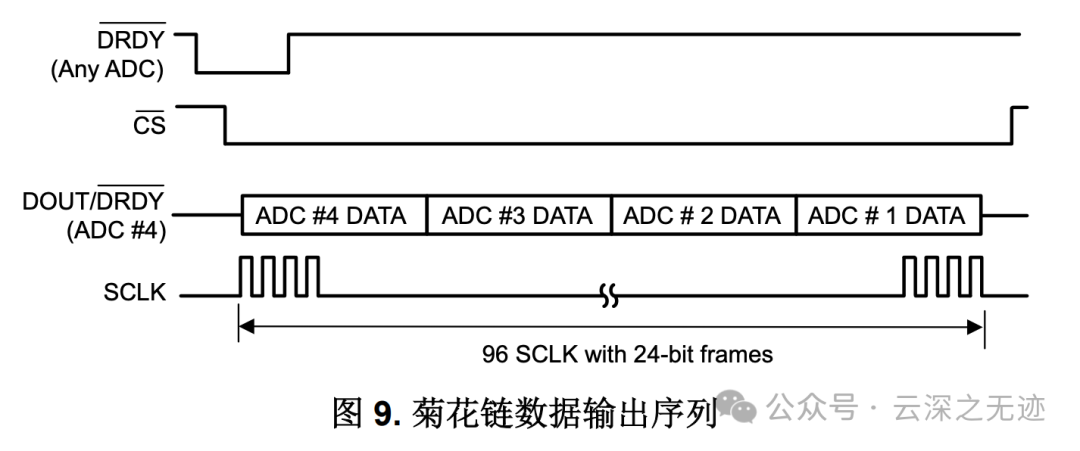

还有一种异步 SYNC 信号同步方案(用 D 触发器同步)。有时候你的同步控制信号(比如 MCU 输出)不是和 ADC 使用的时钟同步的。如果你直接把这个异步信号连到 ADC,可能会造成采样误差高达 一个完整时钟周期,因为它不是精确对齐的。所以推荐用 SN74AUP2G79 这样的 D 型触发器:把异步信号送入触发器用 ADC 的时钟来驱动触发器触发器输出的信号就跟 ADC 的时钟对齐了,确保所有 ADC 精确同步到同一时钟周期。START 引脚并联 → 使用统一控制脉冲同步所有 ADC;START 信号应在时钟下降沿被置高,避免不确定延迟。数据拿到了,传出去,SPI菊花链,所有 ADC 共享 4 条 SPI 线(CS/SCLK/SDI/SDO),这样可以节省主控 IO 资源。 写入时:最先发送链尾 ADC 的数据(ADC#4 → ADC#1);读取时:SDO 首先输出链尾 ADC 的数据(ADC#4 开始)

写入时:最先发送链尾 ADC 的数据(ADC#4 → ADC#1);读取时:SDO 首先输出链尾 ADC 的数据(ADC#4 开始) 但是菊花链链接不是无限的,最大 ADC 数 = ⌊fSCLK / (fDATA × 每帧位数)⌋。

但是菊花链链接不是无限的,最大 ADC 数 = ⌊fSCLK / (fDATA × 每帧位数)⌋。

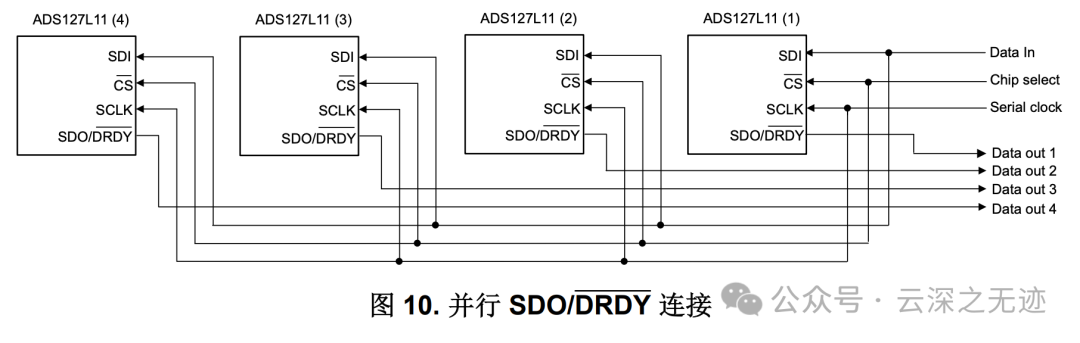

比如SCLK = 20MHz,fDATA = 100kSPS,24bit → 最多支持 8 个 ADC 当采样速率较高(如 1MSPS)时,推荐:所有 ADC 的 SDO 引脚并联至主控多个输入口,重要SCLK 使用 >25MHz,满足读取 24 位数据带宽要求。

当采样速率较高(如 1MSPS)时,推荐:所有 ADC 的 SDO 引脚并联至主控多个输入口,重要SCLK 使用 >25MHz,满足读取 24 位数据带宽要求。

https://www.ti.com.cn/cn/lit/ab/zhcabx6/zhcabx6.pdf?ts=1746006732704

https://www.ti.com.cn/cn/lit/ug/zhcuac3/zhcuac3.pdf?ts=1746066062456

暂无评论