核心要点

受控阻抗布线通过匹配走线阻抗来防止信号失真,从而保持信号完整性。

高速PCB设计中,元件与走线的阻抗匹配至关重要。

PCB材料的选择(如低损耗层压板)对减少信号衰减起关键作用。

受控阻抗布线如何保障信号完整性

为实现电路信号完整性,需遵循以下设计规范:避免直角走线、隔离时钟信号与电源信号、保持元件间最短距离。

受控阻抗布线通过调整走线尺寸和环境参数,使其特性阻抗与设计目标匹配,从而确保信号传输过程中的完整性。随着信号速度提升(甚至达到GHz级且面积缩小),信号完整性成为关键考量。该技术能维持信号强度,使其从源端到终端的传输过程保持稳定。

受控阻抗布线在电路中的行为

电路中除源端和负载外还存在大量元件。能量从元件输出引脚经走线流向负载时会产生失真和损耗。若能量未被负载完全吸收,会反射回源端,引发叠加或抵消效应(如振铃现象),导致信号完整性受损。

阻抗不匹配时,电路可能表现异常。通过匹配走线阻抗可抑制信号反射。当源端与负载阻抗匹配时,能量沿走线传输效率最高,实现从源端到走线、再从走线到负载的高效耦合。这种基于阻抗匹配的布线技术称为受控阻抗布线,可有效消除失真、振铃和信号丢失。

受控阻抗布线设计方法

1. 元件阻抗匹配

首先需匹配电路中元件的阻抗。输入引脚的高阻抗与输出引脚的低阻抗会导致失配,通过在输入/输出引脚间添加端接元件可实现阻抗匹配。

2. 走线阻抗匹配

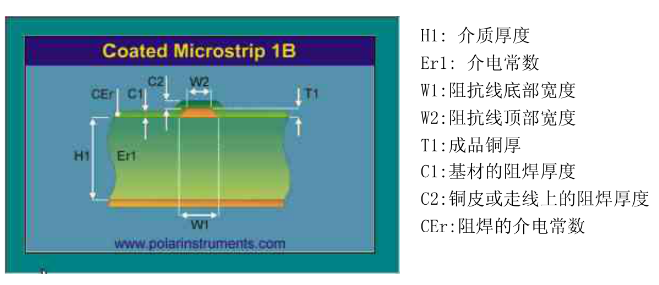

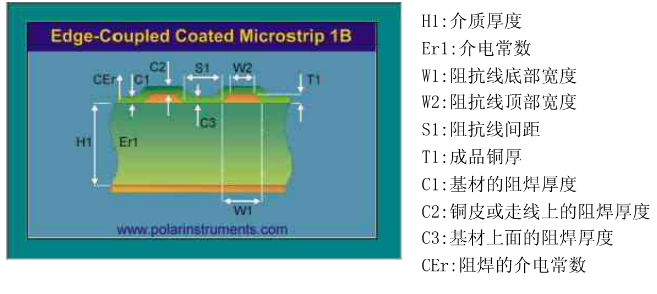

通过调整走线几何尺寸(长、宽、厚度)及环境参数(如介质常数)实现目标阻抗。走线特性阻抗由电阻、感抗、容抗和电导共同决定。设计良好的受控阻抗布线可使阻抗在跨层传输时保持恒定(典型值范围:25–125 Ω)。

PCB材料的介质常数和介质厚度影响走线阻抗。高速设计优先选用低介电常数、低损耗角正切的层压板材料,以提升信号性能,减少失真和相位抖动。低损耗材料制造的PCB能显著改善高频设计的信号完整性。

PCB中的受控阻抗设计实例

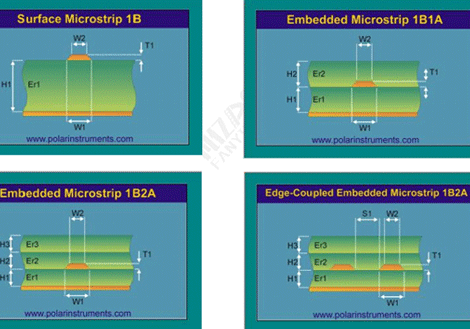

在多层电路板中,走线位于层间,需通过两侧层压板厚度实现阻抗匹配。以下是多层PCB中常见的受控阻抗结构示例:

微带线类型 | 描述 |

嵌入式微带线 | 走线夹于平面层间,一侧为平面层,另一侧为层压板与空气介质组合。 |

偏移带状线 | 走线两侧完全由层压板覆盖。 |

边缘耦合偏移带状线 | 两条受控阻抗走线置于两平面层之间。 |

OrCAD X 24.1版本优化了阻抗与耦合设计流程,提供更高效的受控阻抗布线支持。

在OrCAD X 中应用受控阻抗布线

OrCAD X 提供了一套全面的工具,专门用于帮助设计人员实现受控阻抗布线。这些功能允许精确控制 PCB 走线的阻抗。

功能 | 描述 | 对受控阻抗布线的支持 |

叠层设计配置 | 定义PCB叠层结构,指定材料属性、层数与厚度。 | 通过控制信号走线与参考平面间距,确保阻抗一致性。 |

设计规则定义 | 设置电气、物理及制造约束(如阻抗、线宽、过孔尺寸) | 严格遵循阻抗规范,降低信号完整性风险。 |

实时阻抗分析 | 设计过程中即时反馈阻抗值。 | 快速识别并修正阻抗失配,确保最终电路符合电气性能标准 |

设计内耦合分析 | 评估相邻走线间的耦合效应。 | 调整走线间距与布局,减少串扰并维持阻抗稳定。 |

| 高速布线与SI分析集成 | 结合信号完整性分析优化高频信号走线。 | 通过阻抗匹配减少反射与信号衰减,提升高频信号质量。 |

在处理高速、高频关键信号时,信号完整性必须全程保持。受控阻抗布线是PCB设计的核心实践,可确保信号从源端到负载的无损传输。当走线阻抗匹配时,信号完整性失效概率将降至最低。

暂无评论