在USB电路设计中,电源信号(VBUS)的走线质量直接影响设备充电稳定性与数据传输可靠性。要想电源信号好,良好的走线质量是必不可少,下面就开课讲讲!

1、线宽与载流能力

强制参数:VBUS走线宽度≥50mils(1.27mm),铜厚≥2OZ。

物理依据:2OZ铜厚下,50mils线宽可安全承载1.5A电流(USB 3.0标准),避免线宽不足导致的压降和发热。

验证手段:使用PCB计算器(如Saturn PCB Toolkit)验证线宽-载流关系。

2、走线长度控制

总长红线:VBUS总走线长度≤18英寸(457.2mm)。

风险规避:长距离走线会增加电源噪声和电压降,优先从连接器直连至芯片电源引脚。

补偿策略:若必须绕线,需在路径中增加去耦电容(0.1μF陶瓷电容,靠近电源引脚)。

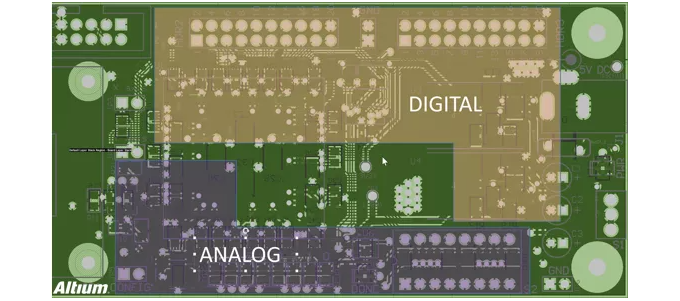

3、空间隔离与层叠设计

隔离标准:VBUS与高速信号线(如D+/D-差分对)间距≥50mils(1.27mm)。

特殊场景:空间受限时,可在相邻层铺铜屏蔽,但需保持VBUS参考平面完整。

层叠要求:VBUS优先布在内层,参考GND或Power平面,避免跨分割区域。

4、过孔与焊盘设计

过孔规范:VBUS过孔数量≤2个,焊盘直径≥30mils,孔径≥15mils。

物理优势:大过孔降低寄生电感,避免电源完整性(PI)恶化。

禁忌操作:禁止在差分对下方放置VBUS过孔,防止阻抗突变。

5、去耦电容布局

电容放置:在VBUS入口处并联10μF电解电容+0.1μF陶瓷电容,距离芯片电源引脚≤50mils。

关键细节:陶瓷电容需靠近引脚,电解电容可放置在板边,通过电源层连接。

验证手段:使用示波器观察电源噪声,确保纹波≤50mV。

6、拓扑与工艺规范

走线形态要求:

禁止90°折弯,统一使用45°或圆弧转角,弯曲半径≥3倍线宽。

避免VBUS与GND形成环路,防止天线效应导致EMI超标。

测试点放置:距离VBUS末端≥50mils,避免破坏载流能力。

本文凡亿教育原创文章,转载请注明来源!

暂无评论