凡亿教育-小米

凡事用心,一起进步打开APP

公司名片网表的生成

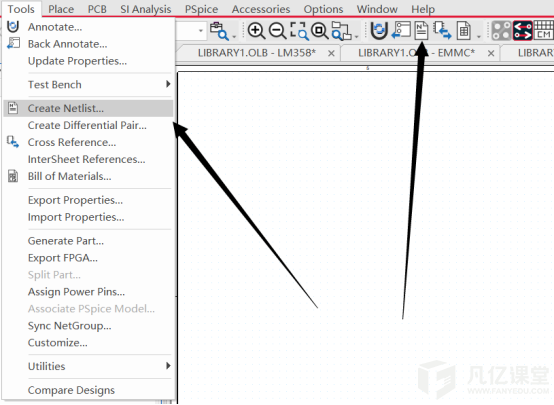

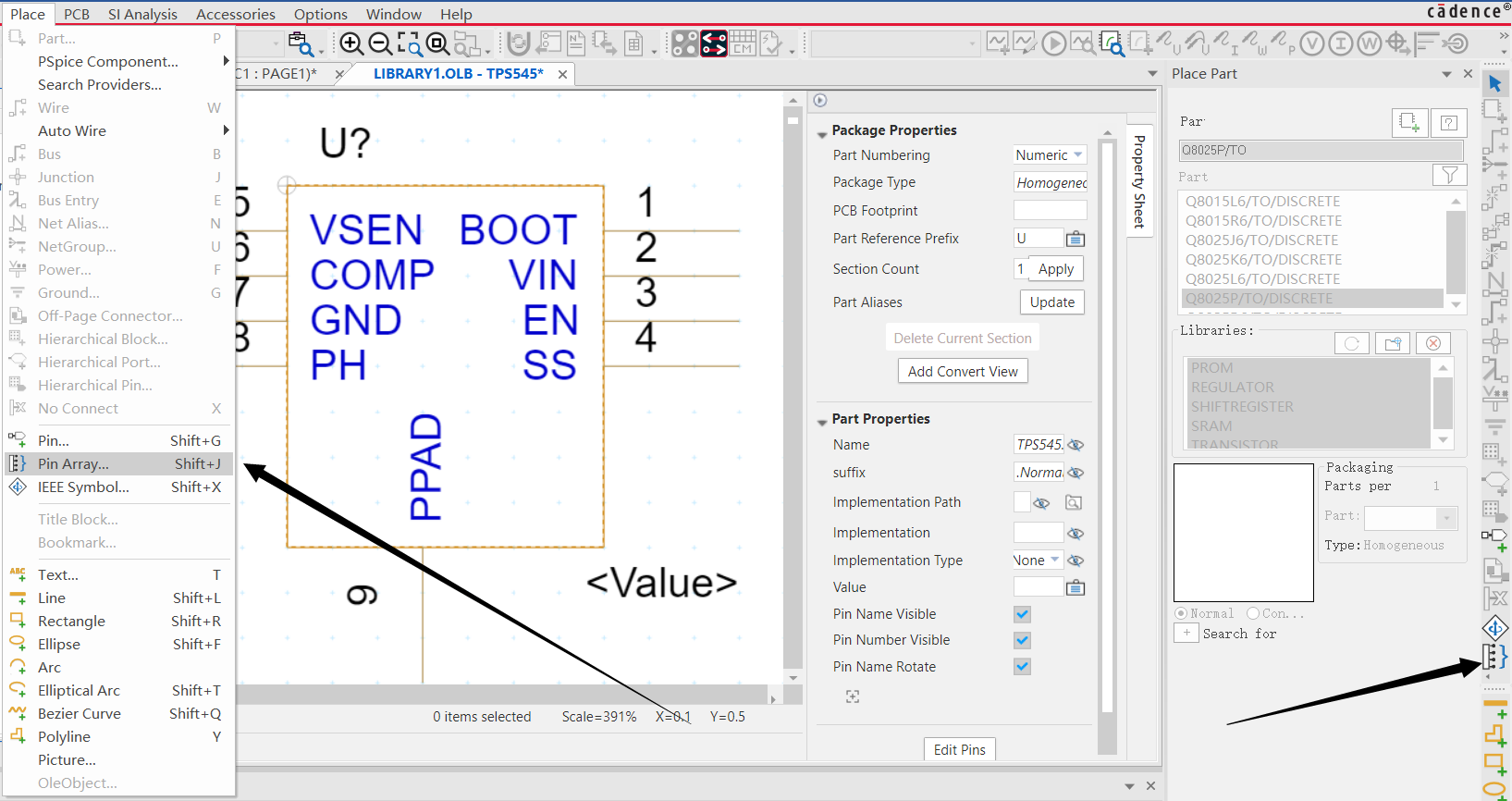

第一步,选择原理图的根目录,执行菜单命令Tools—Create Netlist,或者直接点击![]() 图标,调出产生网表的界面,如图2-107所示。

图标,调出产生网表的界面,如图2-107所示。

图2-107 产生网表示意图

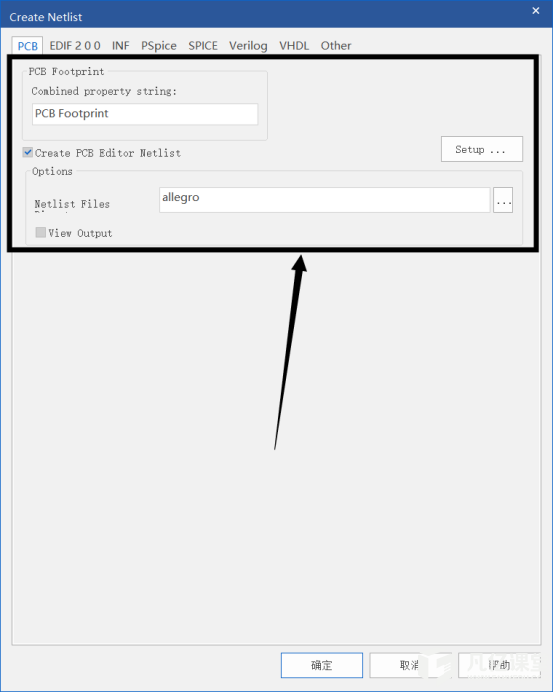

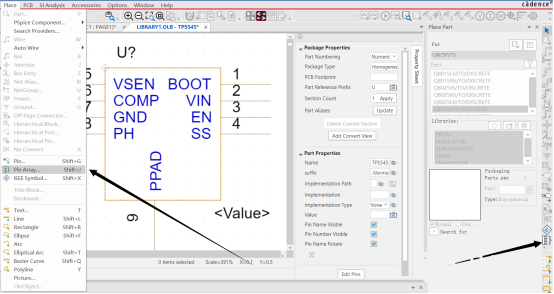

第二步,在弹出的Create Netlist对话框中选择PCB ,产生Cadence Allegro的第一方网表,如图2-108所示。

图2-108 Cadence Allegro第一方网表参数设置示意图

第三步,输入Cadence Allegro第一方网表时需注意下面几个地方:

(1)需要勾选Create PCB Editor Netlist,才会生成网表。

(2)下面的Nestlist Files是输出网表的存储路径,不进行更改的话,在当前原理图目录下会自动产生Cadence Allegro的文件夹,里面就是输出的网表。

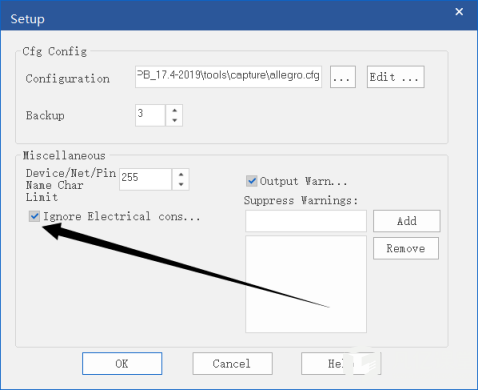

(3)点击右侧的Setup按钮,如图2-109所示,勾选Ignore Electrical Constraints选项,则忽略原理图中所添加的规则。

图2-109 输出网表设置示意图

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表凡亿课堂立场。文章及其配图仅供工程师学习之用,如有内容图片侵权或者其他问题,请联系本站作侵删。

相关阅读

进入分区查看更多精彩内容>

暂无评论