凡亿教育-小辣椒

凡事用心,一起进步打开APP

公司名片AD 如何添加PIN delay

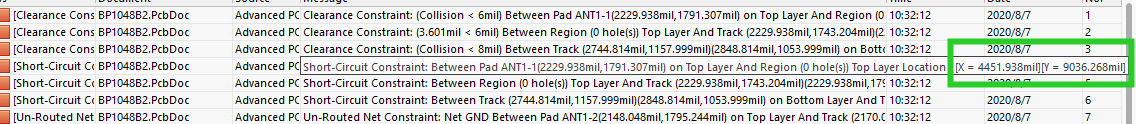

在每一个超过500 MHz的高速设计中,连接介质,或连接到模具上的电线,都会给信号带来延迟。这种在设备中的延迟称为引脚延迟.即使从设计和PCB的角度来看,两个设备是完全兼容的,不同设备的封装延迟时间也会不同,所以它们需要考虑Pins信息。

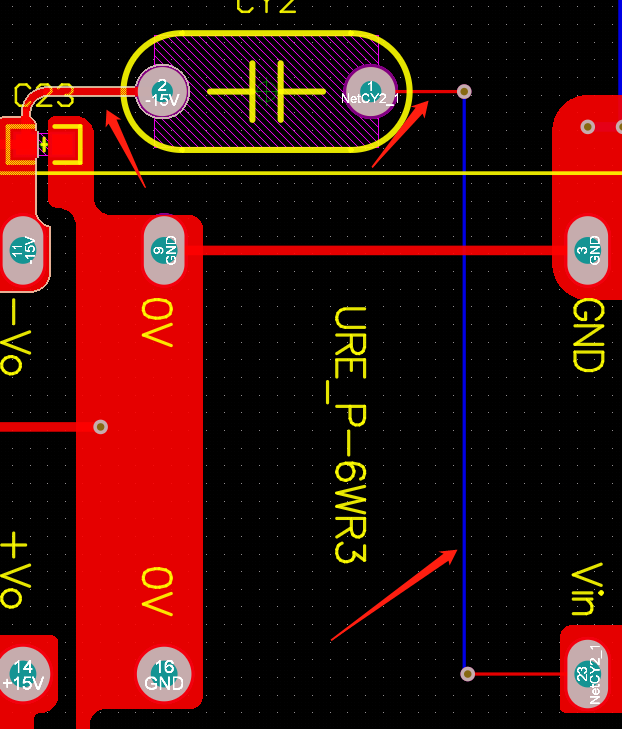

1、原理图里面的管脚延迟定义,单位可以自行输入。

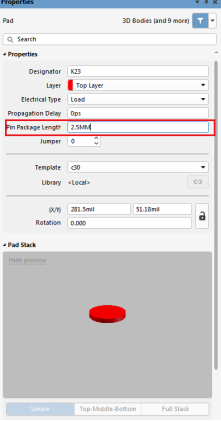

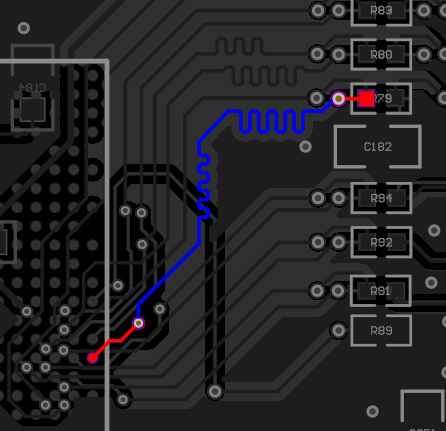

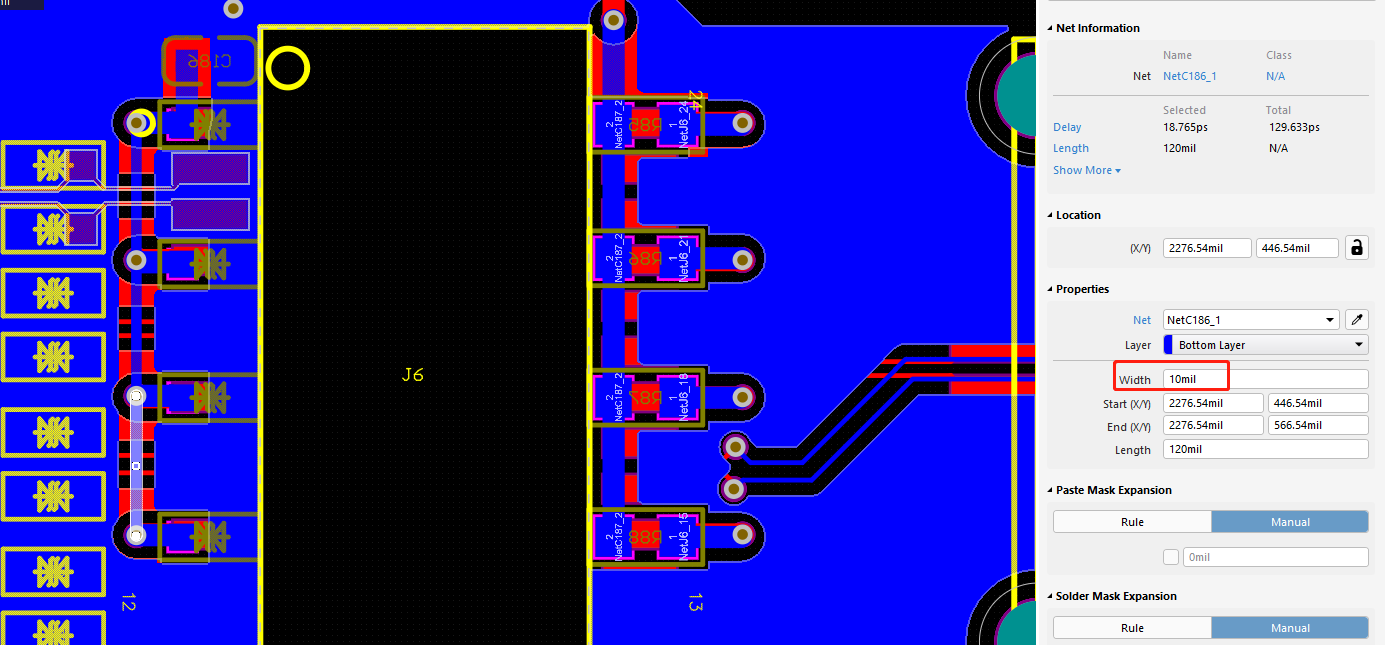

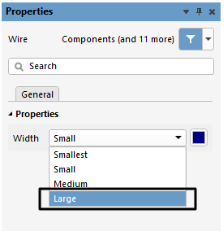

2、在PCB封住管脚中添加管脚延迟。

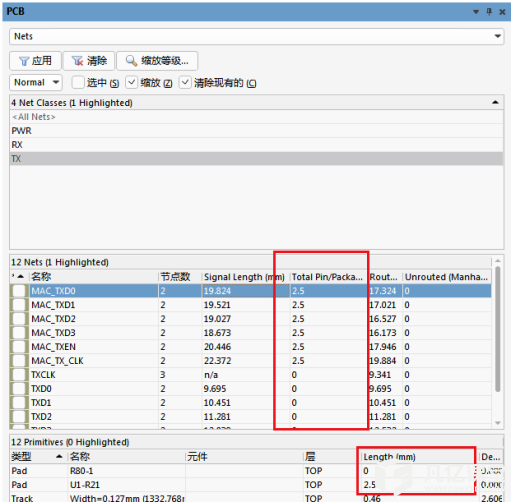

3、添加完成之后添加xSignals等长时,会对应到等长模型里面。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表凡亿课堂立场。文章及其配图仅供工程师学习之用,如有内容图片侵权或者其他问题,请联系本站作侵删。

相关阅读

进入分区查看更多精彩内容>

暂无评论