一、滤波电容在EMC中的功能

电容在PCB的EMC设计中,是使用最为广泛的器件。按照功能的不同,电容可以分为三种:

去耦(Decouple):打破系统或电路的端口之间的耦合,以保证正常的操作。

旁路(Bypass):在瞬态能量产生的地方为其提供一个到地的低阻抗通路。是良好退耦的必备条件之一。

储能(Bulk):储能电容可以保证在负载快速变到最重时电压不会下跌。

二、电容自谐振问题

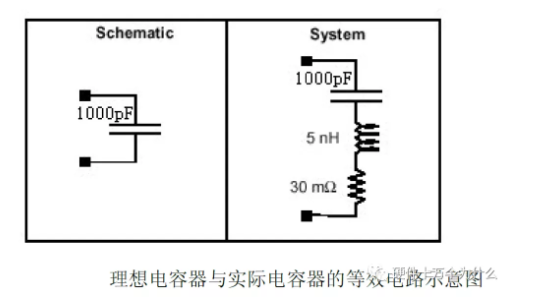

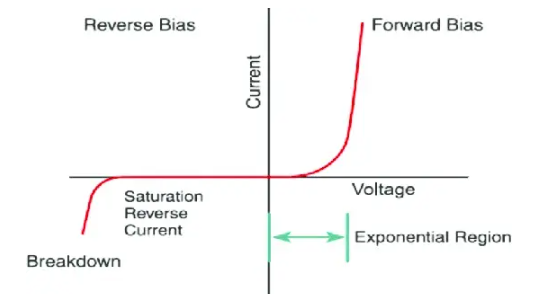

我们用来滤波的电容器并不是理想的电容器,在系统中实际表现为理想电容与电感和电阻的串联,如下图所示:

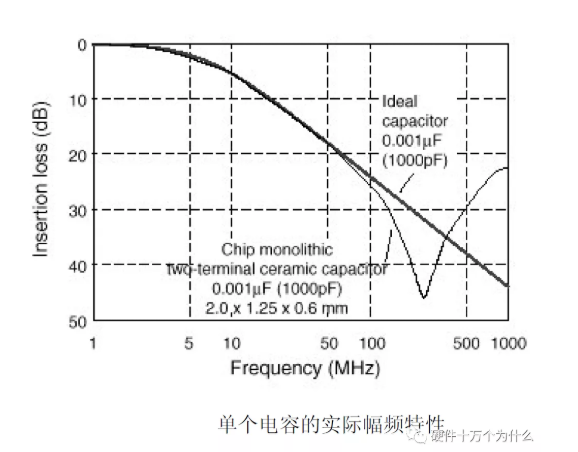

多层电容器(Muti-LayerCapacitor)在装配到PCB板上时会产生将近5nH的寄生电感,再加上约30m欧的引线电阻,其频率特性表现为如图所示的曲线。滤波电容将不是理想的低通滤波器,实际的插入损耗特性表现为以自谐振点为中心的带通滤波电路。

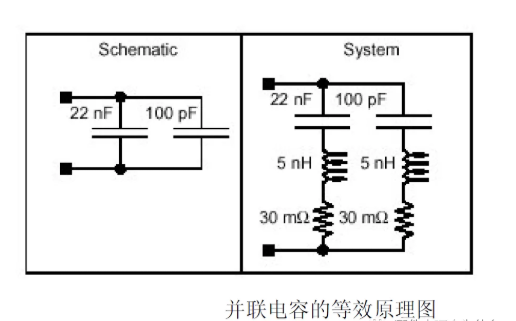

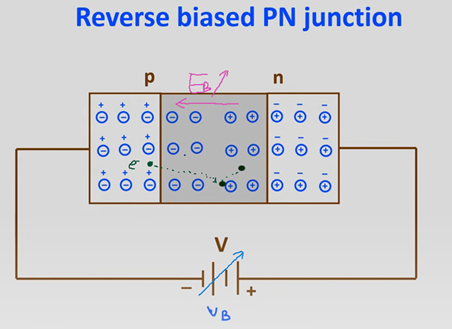

两个电容串联时,由于ESL(等效串联电感)和ESR(等效串联电阻)的存在,会产生反谐振问题。下图给出了电容并联的等效原理:

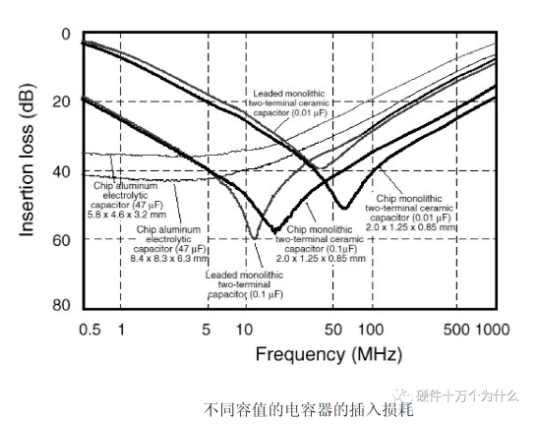

下图给出了它们的真实的幅度-频率特性:

在将近15MHz到175MHz的一个较宽的频带内,并联电容的阻抗比单独一个大电容的阻抗要来的大,由于两电容产生了谐振,在150MHz处产生了一个阻抗的峰值,系统其他部分在该频率范围内产生的能量只能有很少的一部分被旁路到地平面。

三、ESR对并联电容幅频特性的影响

阻抗的峰值与电容器的ESR的值成反比,随着单板设计水平与器件性能的提高,并联电容的阻抗的峰值将会随着ESR的减小而增加,并联谐振峰值的形状与位置取决于PCB板的设计与电容的选择。有几条原则应该了解:

随着ESR的减小,谐振点的阻抗会减小,但反谐振点的阻抗会增大;

n个相同电容并联使用时,最小阳抗口能小干ESRIn;

多个电容并联时,阻抗并不一定发生在电容的谐振点;

对于给定数量的电容器,比较好的选择是电容值在一个较大的范围内均匀展开,各个电容值的ESR适中:比较差的选择是仅有少量的电容值,而且电容的ESR都非常小。

四、ESL对并联电容幅频特性的影响

电容封装和结构不同,ESL也不同,几种典型封装电容的ESL如表所示:

电容的ESL与电容值一起决定电容器的谐振点与并联电容器的反谐振点的频率范围。在实际的设计中,应该尽量选用ESL小的电容器。

五、电容器的选择

对于RF设计而言,陶瓷电容器、聚酯纤维电容器和聚苯乙烯薄膜电容器都是很好的选择。

对于EMI滤波器来讲,对电容器的介质材料要求并不高,常见的X7R、Y5V和Z5U等松散介质都是不错的选择:通常绝对的电容值、电容器的温度系数、电压变化系数等并不重要。不同种类、不同容值的电容滤波范围是不同的,下面是典型的插入损耗比对效果:

由上图可以看出,同为0805封装的贴片陶瓷电容,001UF的电容比0.1UF的电容具有更好的高频滤波特性;建议板极工作频率高于50MHZ的单板(如传输、MUSA的多数单板)全部使用0.01UF的滤波电容,而不是我们目前大量采用的0.1UF的滤波电容。

六、去耦电容与旁路电容的设计建议

1、以供应商提供的产品资料上的自谐振特性为基础选择电容,使之符合设计的时钟速率与噪声频率的需要。

2、在所需要的频率范围内加尽可能多的电容。例如,22nF的电容的自谐振频率将近为11MHz,有用的阻抗(Z1欧姆)范围为6M~40MHz,你可以在该频带范围内加尽可能多的电容,以达到需要退耦的水平。

3、在尽可能靠近IC每个电源管脚的地方,至少放一个去耦电容器,以减小寄生阻抗。

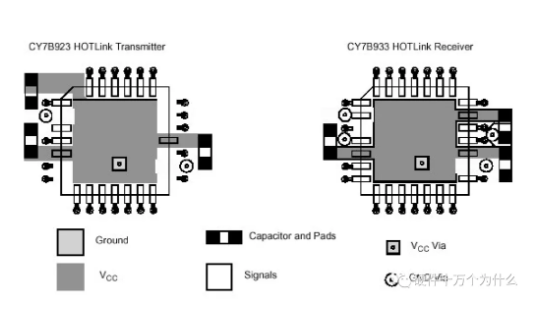

4、旁路电容与IC尽可能放在同一个PCB平面上。有一个需要特别注意的地方:在两种布局中,Vcc网络都只有一个点连到Vcc平面。这样做可使IC内外的噪声都必须通过这个唯一的过孔走到电源平面上去,过孔的附加阻抗帮助避免了噪声向系统其余部分的扩散。

5、对于多时钟系统可以将电源平面作图3-14所示的分割,对每一个部分使用一种正确容值的电容器,被狭缝分隔的电源平面将一部分的噪声与其他部分的敏感器件分隔开来,同时提供了中容值的分离。

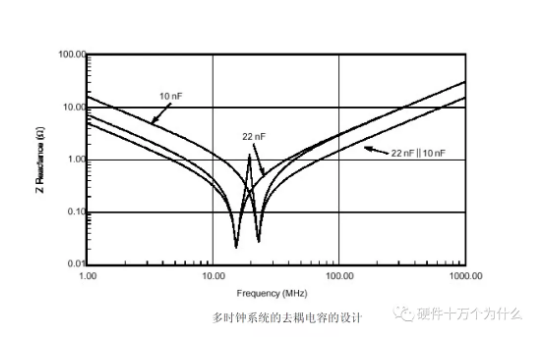

6、对于时钟频率在一个较宽的范围内变化的系统,旁路电容的选择甚为困难。一个较好的解决方法是将两个容值上接近2:1的电容并联放置。

这样做可以提供一个较宽的低阻抗区,和一个较宽的旁路频率,下面这张图可以看到,阻抗峰值仍然产生了,但却小于15欧,而可用的频率范围(阻抗小于15欧)则扩展到将近3.25MHz到100MHz的范围,这种多退耦电容的方法只在一个单独的IC需要一个较宽的旁路频率范围而且单个电容无法达到这一频带时才使用。而且,容值必须保持2:1的范围内,以避免阻抗峰值超过可用的范围。

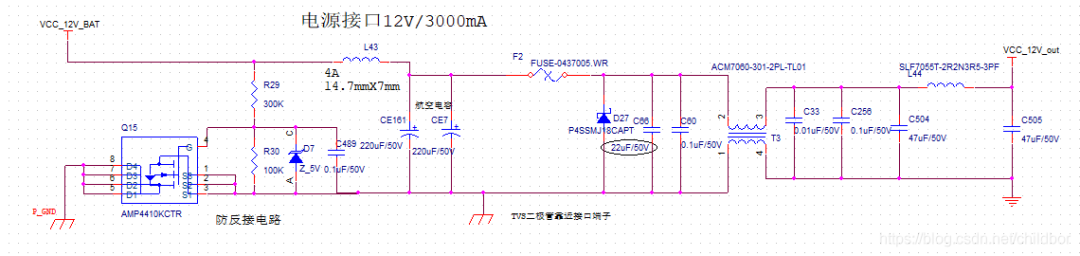

七、储能电容的设计

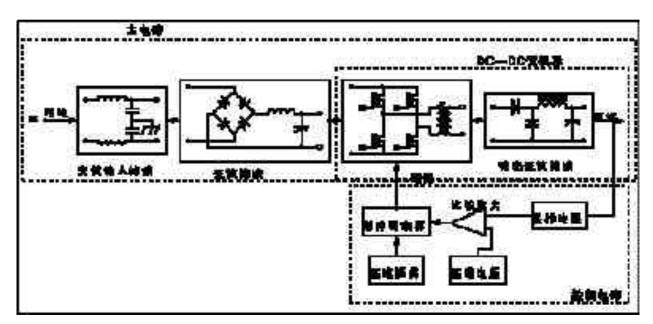

储能电容可以保证在负载快速变到最重时供电电压不会下跌。储能电容可分为板极储能电容、器件级储能电容两种:

一是,板极储能电容:保证负载快速变到最重时,单板各处供电电压不会下跌。在高频、高速单板(以及条件允许的背板),建议均匀排布一定数量的较大容值的钽电容(luf、10uf、22uf、33uf),以保证单板同一电压的值保持一致。

二是,器件级储能电容:保证负载快速变到最重时,器件周围各处供电电压不会下跌。对于工作频率、速率较高、功耗较大的器件,建议在其周围排放1-4个较大容值的钼电容(luf、10uf、22uf、33uf),以保证器件快速变换时其工作电压保持不变。

储能电容的设计应该与去耦电容的设计区别开来,有以下设计建议:

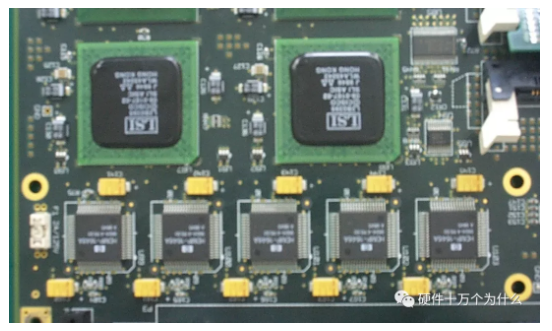

1、当单板上具有多种供电电压时,对一种供电电压储能电容仍然只选用一种容值的电容器,一般选用表贴封装的Tantalum电容(钽电容),可以根据需要选择10uf、22uf、33uf等。

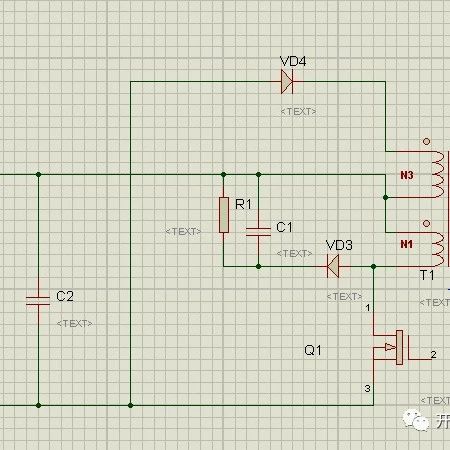

2、不同供电电压的芯片构成一个群落,储能电容在这个群落内均匀分布,如下图所示:

本文转载自硬件十万个为什么,如涉及作品内容、版权和其它问题,请于联系工作人员微,我们将在第一时间和您对接删除处理!

暂无评论