高速高密度多层PCB板的SI/EMC(信号完整性/电磁兼容)问题长久以来一直是设计者所面对的最大挑战。然而,随着主流的MCU、DSP和处理器大多工作在100MHz以上(有些甚至工作于GHz级以上),以及越来越多的高速I/O埠和RF前端也都工作在GHz级以上,再加上应用系统的小型化趋势导致的PCB空间缩小问题,使得目前的高速高密度PCB板设计已经变得越来越普遍。许多产业分析师指出,在进入21世纪以后,80%以上的多层PCB设计都将会针对高速电路。

高速讯号会导致PCB板上的长互连走线产生传输线效应,它使得PCB设计者必须考虑传输线的延迟和阻抗搭配问题,因为接收端和驱动端的阻抗不搭配都会在传输在线产生反射讯号,而严重影响到讯号的完整性。另一方面,高密度PCB板上的高速讯号或频率走线则会对间距越来越小的相邻走线产生很难准确量化的串扰与EMC问题。SI和EMC的问题将会导致PCB设计过程的反复,而使得产品的开发周期一再延误。

一般来说,高速高密度PCB需要复杂的阻抗受控布线策略才能确保电路正常工作。随着新型组件的电压越来越低、PCB板密度越来越大、边缘转换速率越来越快,以及开发周期越来越短,SI/EMC挑战便日趋严峻。为了达到这个挑战的要求,目前的PCB设计者必须采用新的方法来确保其PCB设计的可行性与可制造性。过去的传统设计规则已经无法满足今日的时序和讯号完整性要求,而必须采取包含仿真功能的新款工具才足以确保设计成功。

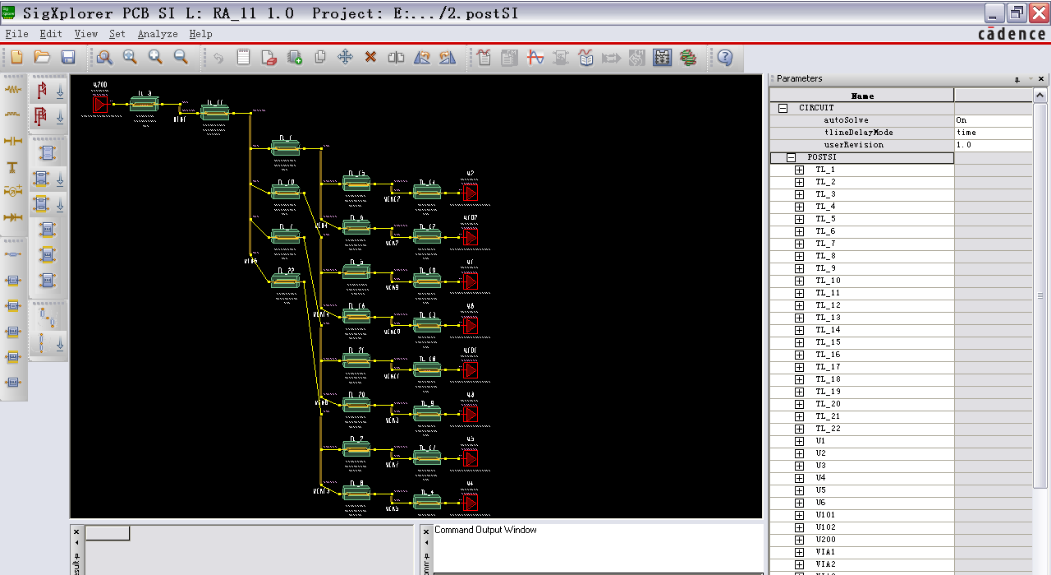

Cadence的Allegro PCB SI提供了一种弹性化且整合的信号完整性问题解决方案,它是一种完整的SI/PI(功率完整性)/EMI问题的协同解决方案,适用于高速PCB设计周期的每个阶段,并解决与电气性能相关的问题。

Allegro PCB SI信号完整性分析的操作步骤,就是接下来将要介绍的。

一、Allegro PCB SI分析前准备:

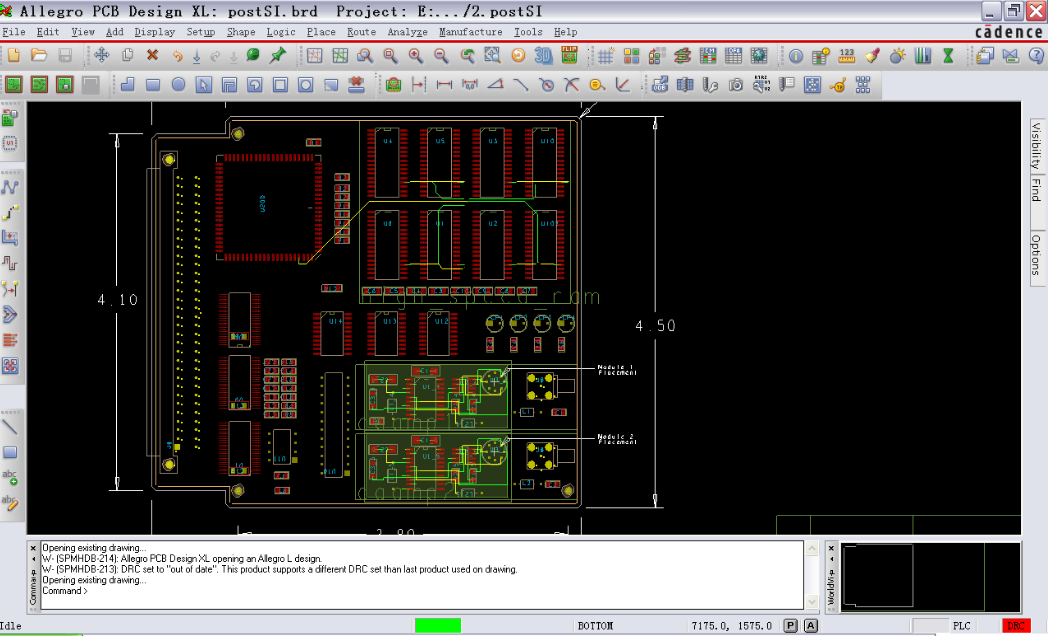

1、准备需要分析的PCB,如下图;

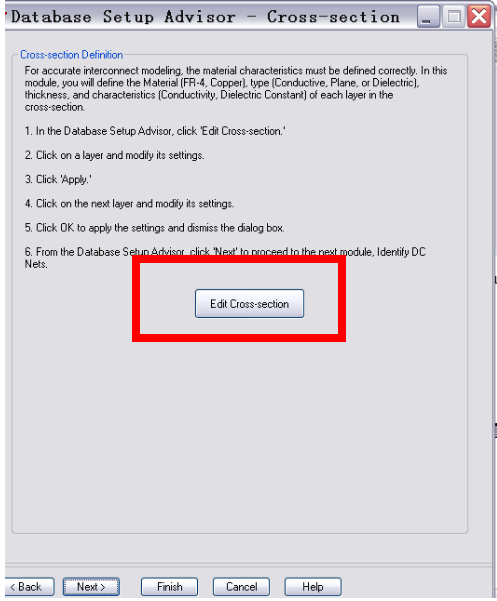

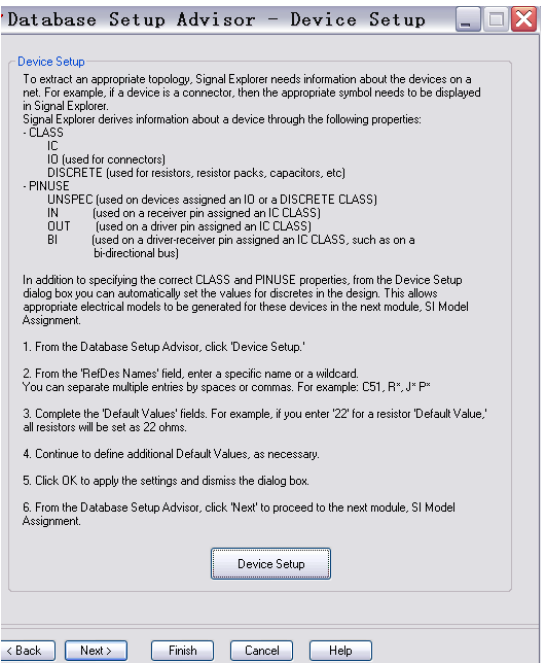

2、SI分析前的相关设置,执行Tools/Setup Advisor,进入Database Setup Advisor对话框,进行SI分析前的设置;

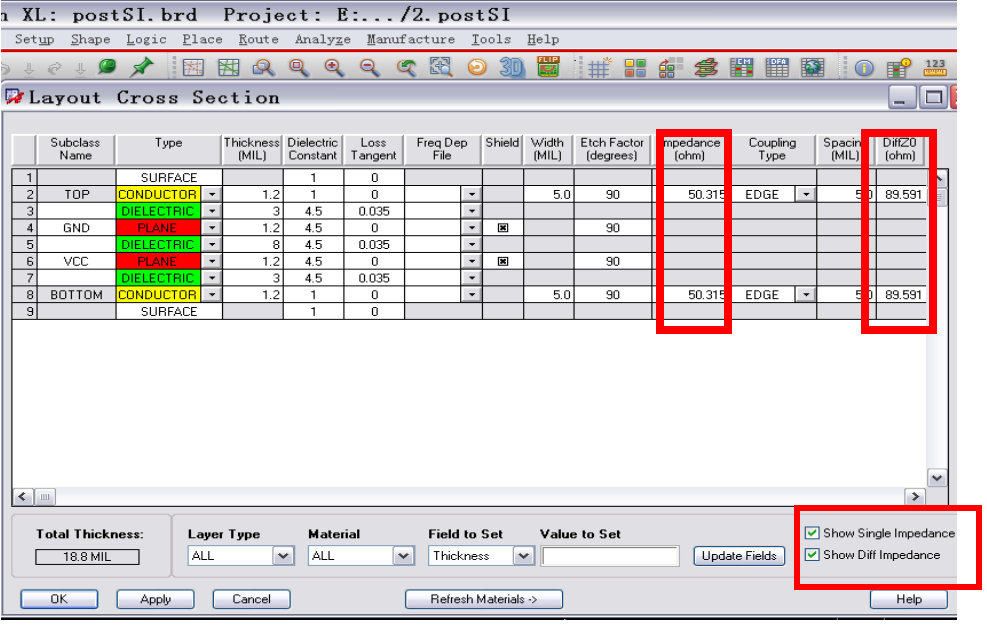

(1)设置PCB叠层的材料、阻抗等,点击Edit Cross section,进入叠层阻抗等设置界面。

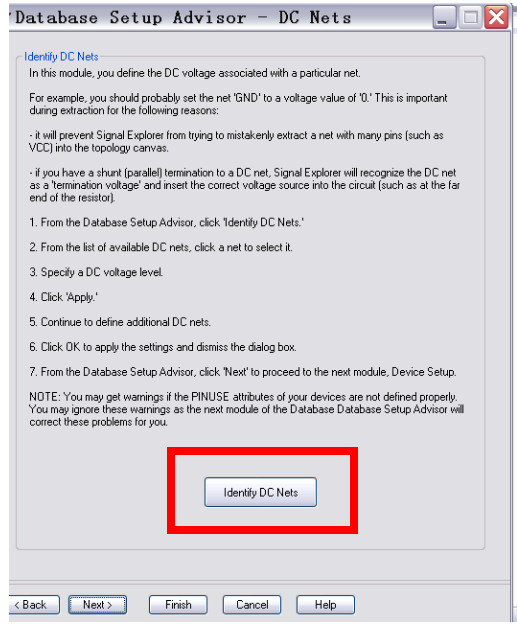

(2)设置直流电压网络的参考值,点击Identify DC Nets,进入直流电压参考值的设置界面。

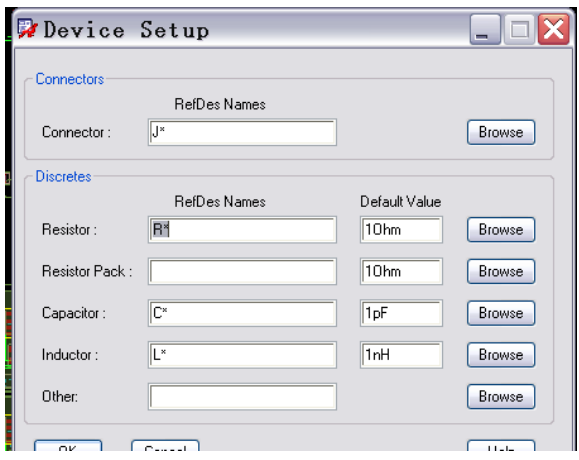

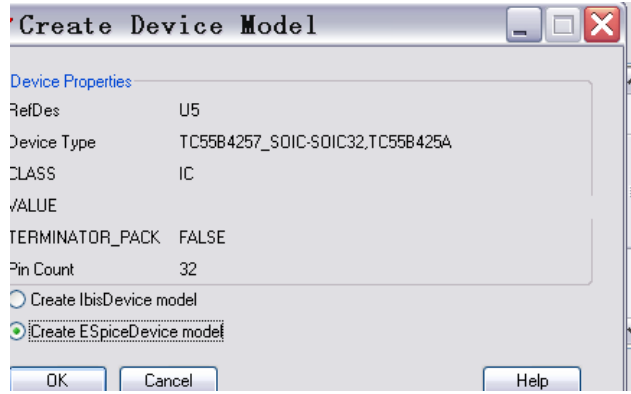

(3)零件默认设置,点击Device Setup进入设置界面。

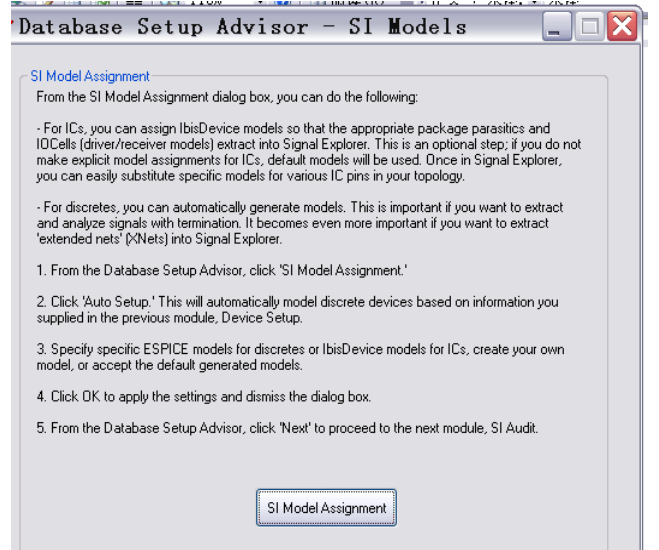

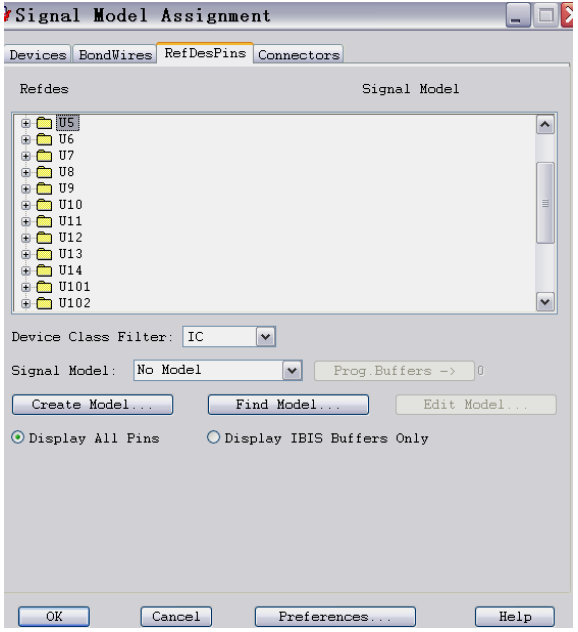

(4)信号完整性分析需要PCB上的零件都有自己的电气模型,在这一步里,进入SI Model Assignment界面,进行零件的模型赋予。

在Signal Model Assignment模型赋予的界面中,对于集总元件R、C、L而言,可以直接点击Create Model来创建元件电气模型。

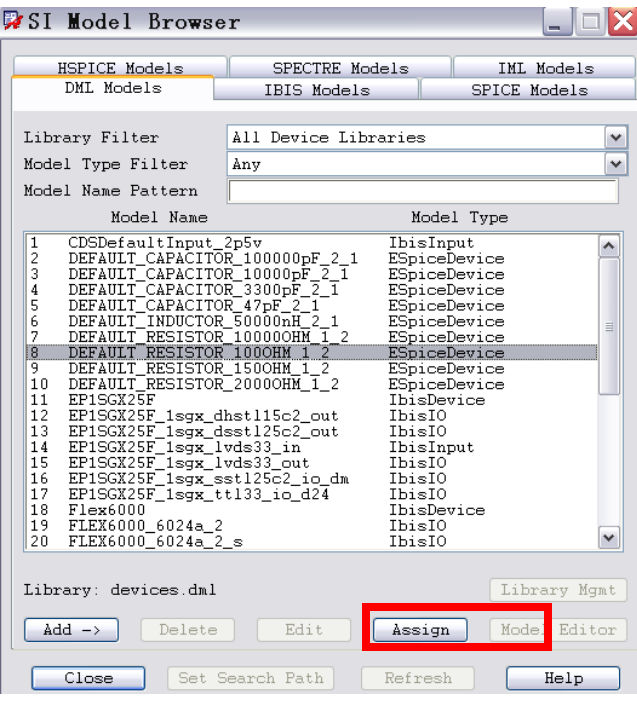

对于有源器件和其他芯片,可以点击Find Model,进入SI Model Browser界面,寻找器件对应的SI仿真模型,然后点击Assign命令,赋予元件对应的DML信号完整性分析模型。

其中元件的IBIS模型通常芯片生产厂家都会提供,在其网上下载即可。

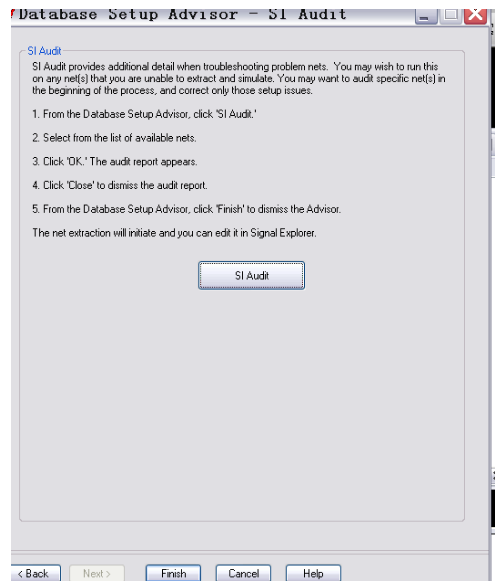

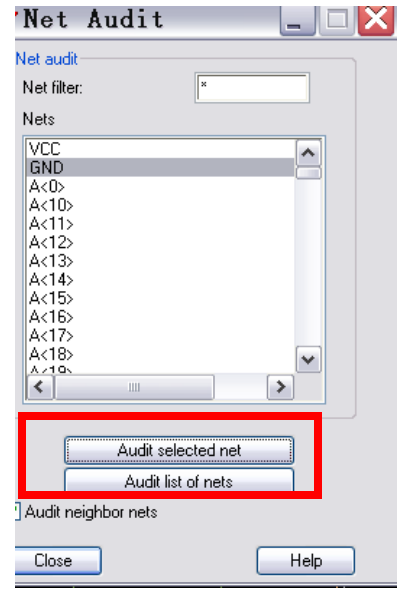

(5)零件的SI模型审核,点击SI Audit进入Net Audit界面,选择相应网络进行审核。

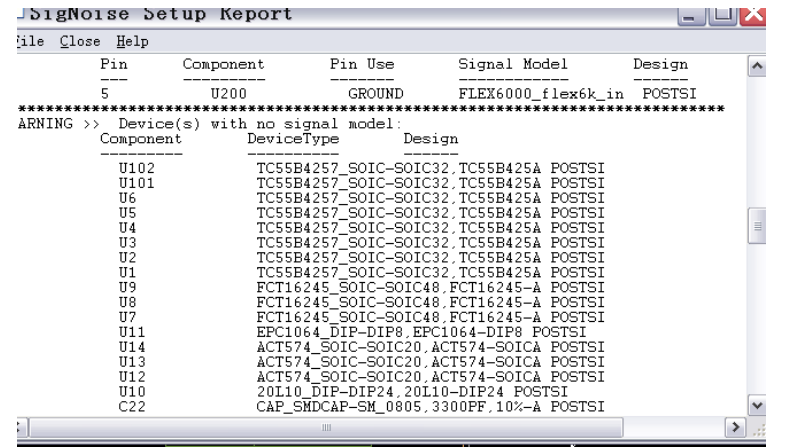

(6)点击Finish命令,弹出SigNoise Setup Report窗口,这里是信号完整性分析的设置报告。

本章节完,请继续阅读第2章节

暂无评论