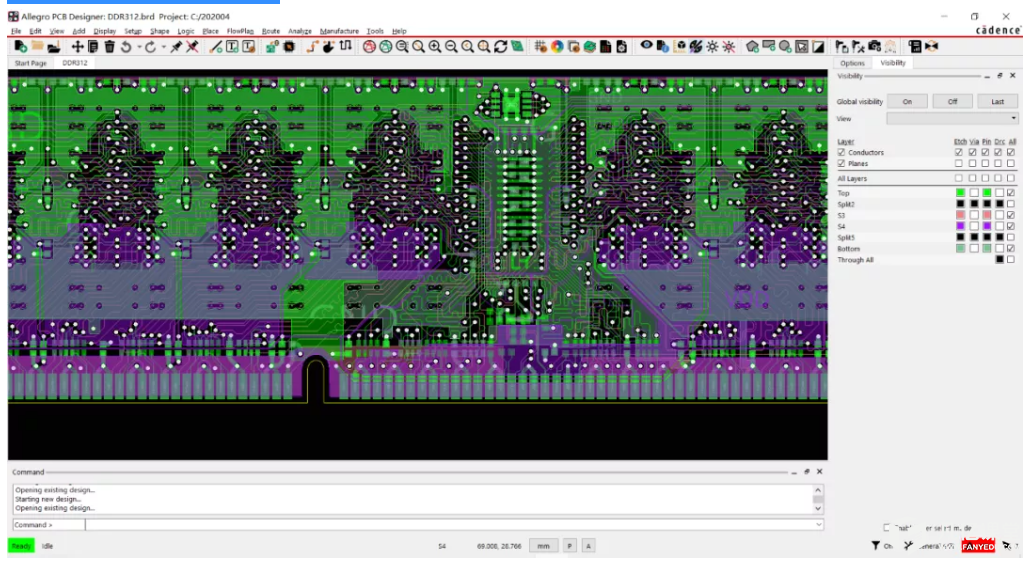

Cadence PCB SI仿真流程(2)

SI信号完整性分析:

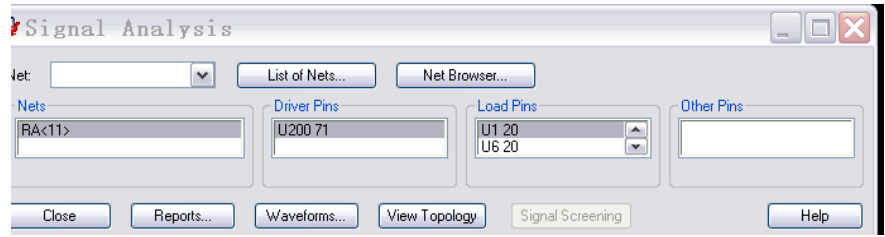

SI分析的前期准备完成之后,就可以进行信号完整性分析了,执行Analyze/SI EMI Sim/Probe命令,然后选择需要进行SI分析的网络或者差分对(模型分配中必须设置好差分对),如下图所示:

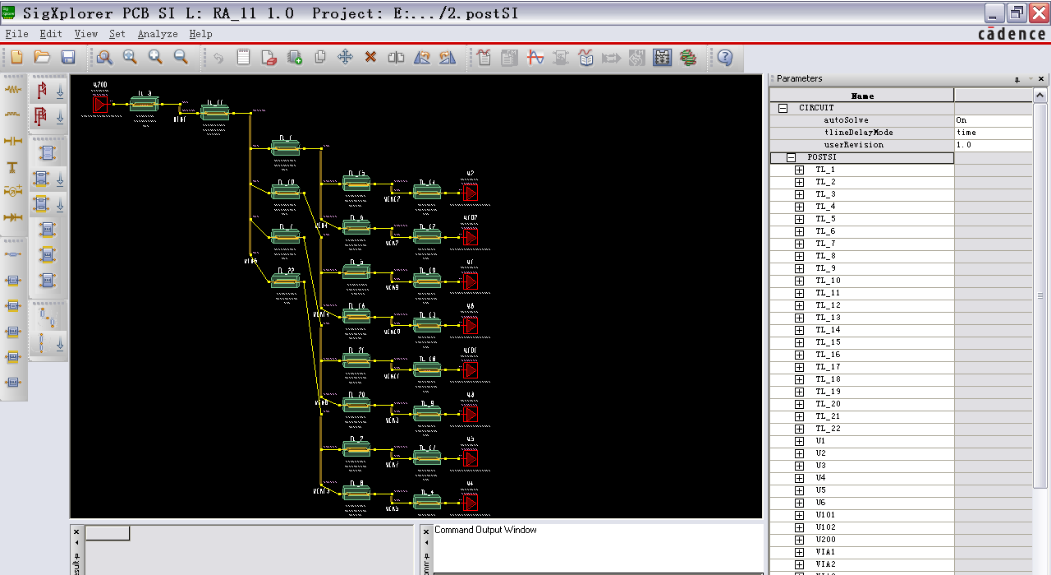

点击View Topology可以进入SigXlorer界面,则所选网络的拓扑结构被提取出来,如下图:

网络拓扑结构提取成功之后,接下来就是设置仿真默认参数,设置驱动端激励源信号,然后就是分析得到网络信号完整性分析波形,具体流程如下。

1、 仿真默认参数设置

在提取的网络拓扑结构中,执行Analyze/Preferences…命令,弹出Analysis Preferences对话框,设置信号完整性分析的默认参数。

我们做SI分析的时候,有一些默认分析参数设置,其中主要默认参数设置有以下几点:

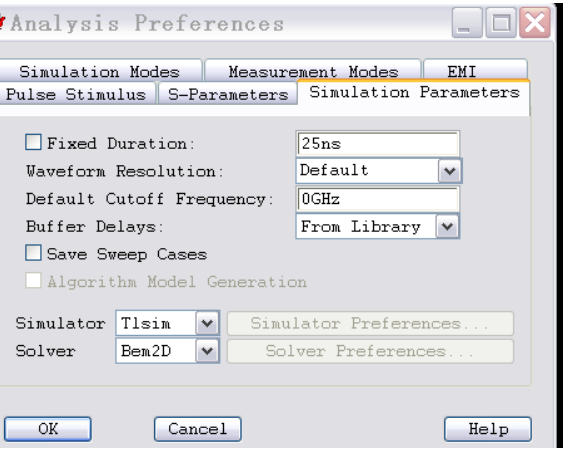

(1)Pulse Stimulus栏,用以设置默认激励源,Measurement Cycle设置仿真分析的周期数;Switching Frequency设置默认脉冲激励的频率;Duty Cycle设置脉冲激励的占空比;Offset设置激励源相位。

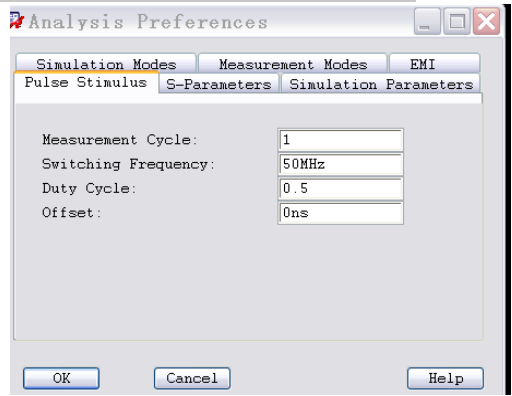

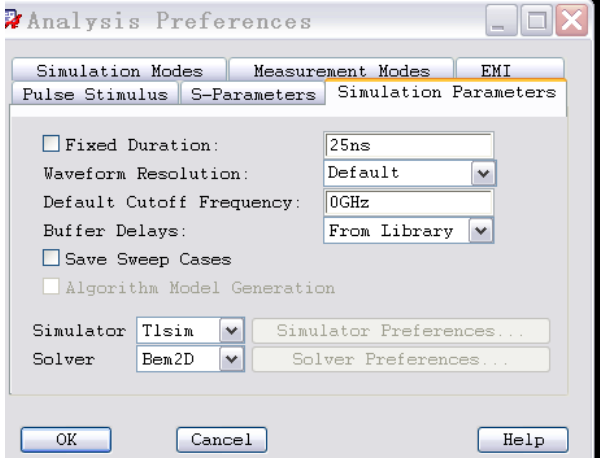

(2)仿真参数(Simulation Parameters)设置,Fixed Duration设置脉冲激励的持续时间;Waveform Resolution设置输出波形的分辨时间;Default Cutoff Frequency设置分析截止时间;Simulator和Solver设置仿真分析的解算器和分析算法。

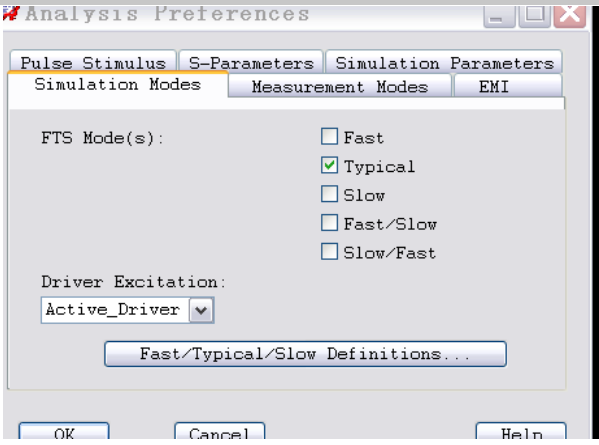

(3)仿真模式(Simulation Modes)设置,FTS Modes(s)设置仿真类型,有典型分析,还有两种最坏情况分析,即Fast、Slow两种模式.

(4)测量模式(Measurement Modes)设置,Measure Delay At脉冲延时设置;Receiver Selection接收端选择;Custom Simulation设置用户分析类型,Reflection信号反射分析,Crosstalk串扰分析,EMI电磁干扰分析;Drvr Measurement Location设置驱动端位置,Pin表示驱动端在芯片外部封装引脚处,Die则表示驱动端信号在芯片内部的裸片引脚处;Rcvr Measurement Location设置接收端信号位置,也是Pin和Die两种选择,意义相同。

结束以上的设置,即完成了SI分析的默认参数设置,接下来就需要设置驱动端的激励源设置。

1、 驱动端激励源设置

SI仿真分析,都需要设置好驱动端的激励源,然后才能进行分析。

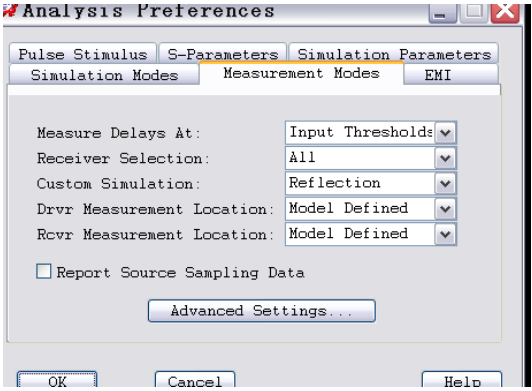

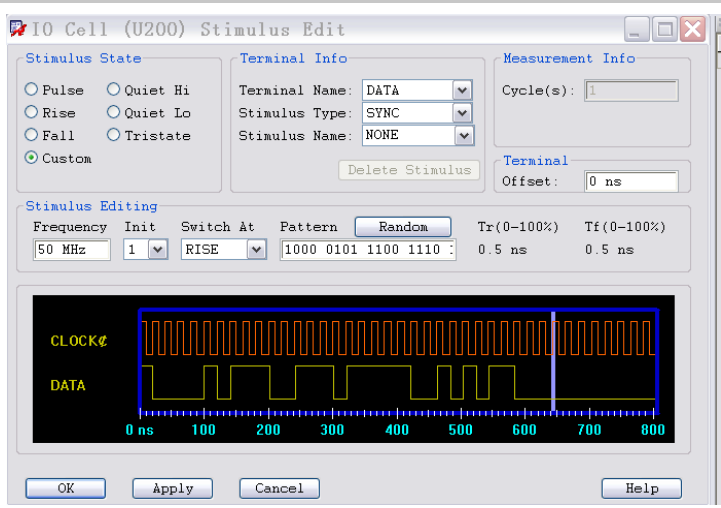

在驱动端点击TRISTATE,弹出Stimulus Edit激励源编辑窗口,在这里进行激励源的编辑,如下图。

Stimulus State选择激励源状态;Terminal Info设置激励源输出信息;Stimulus Editing设置激励源的频率,初始值,转换边沿,激励信号输出波形。

1、 SI信号完整性分析

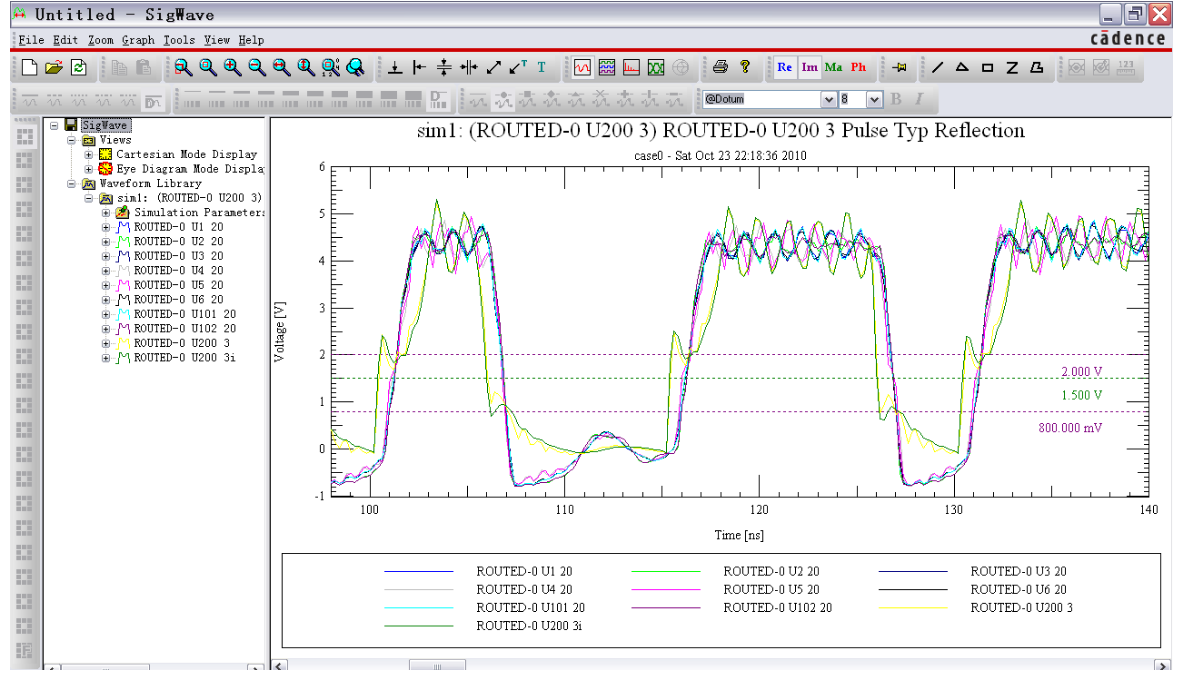

驱动端激励源设置完成后,就可以进行SI分析了,在SigXlorer界面中,执行Analyze/Simulate命令,即可进入SigWave窗口,输出该网络SI分析的波形。

这就是输出波形,是对相应网络进行SI分析的结果。其中ROUTED-0 U200 3是驱动端芯片U200的外部封装引脚3处的波形,ROUTED-0 U200 3i则表示驱动端芯片U200的内部裸片引脚3处的波形。

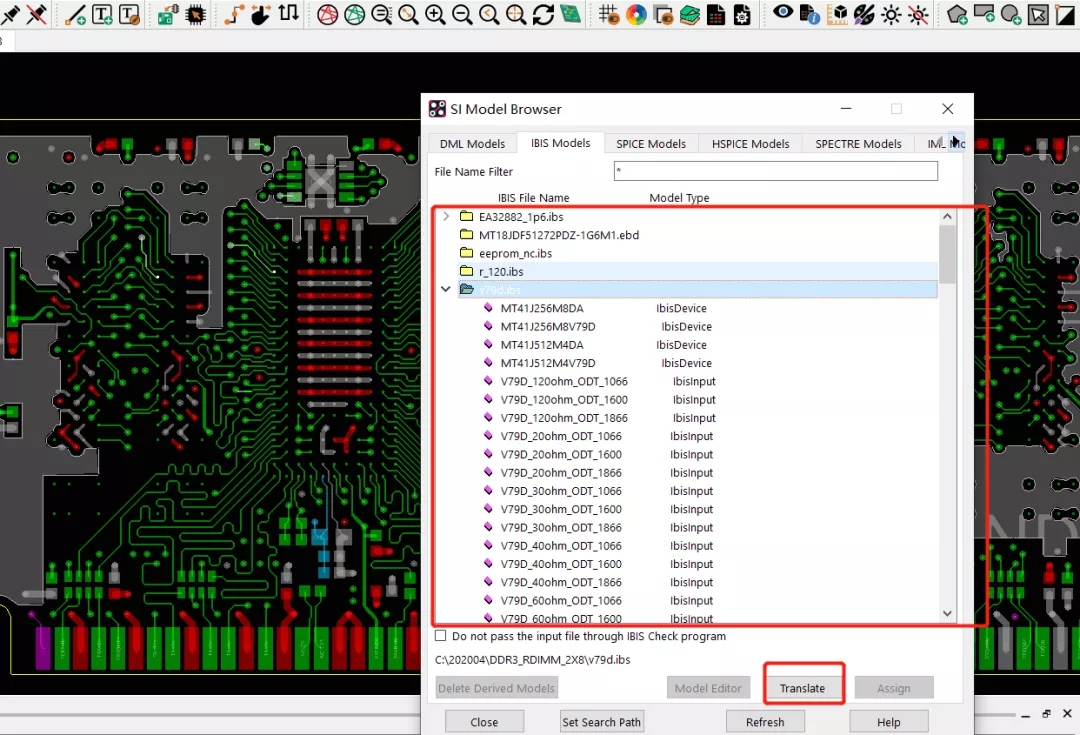

三、IBIS模型

IBIS(Input/Output Buffer Informational Specifation)是用来描述IC 器件的输入、输出和I/O Buffer行为特性的文件,并且用来模拟Buffer和PCB上电路系统的相互作用。在IBIS模型里核心内容就是Buffer的模型,因为这些Buffer 产生一些模拟的波形,仿真器利用这些波形仿真出传输线、对PCB的影响和一些高速现象(如串扰,EMI 等)。具体而言IBIS 描述了一个Buffer 的输入和输出阻抗(通过I/V曲线的形式)、上升和下降时间以及对于不同情况下的上拉和下拉,那么工程人员可以利用这个模型对PCB 板上的电路系统进行SI、串扰、EMC 以及时序的分析。

IBIS 模型中包含的是一些可读的ASCII 格式的列表数据。IBIS 有特定的语法和书写格式。IBIS模型中还包括一些电气说明如Vinh 、Vinl 、Vmeas 以及管脚的寄生参数(如管脚的引线R、L、C等)。有一点需要注意的是IBIS 模型并不提供IC 器件:功能信息、逻辑信息、输入到输出的时间延迟等。也就是说,IBIS 模型只是提供了器件的输入、输出以及I/O Buffer 的行为特性,而不是在IC 器件给定不同的输入,测量对应不同的输出波形;而是在描述器件有一个输入时,我们看不同情况下输出的特性(具体的说我们可以在输出端接一个电压源,这样我们在确保器件输出高电平或者是低电平时,调整电压源的数值,可以测出不同的电流,这样我们就可以在确保输出管脚输出某一个状态时得出一些I/V 的数值,至于电压源具体的变化范围后面的内容会涉及到)。所以对于器件商家而言IBIS模型不会泄漏器件的内部逻辑电路的结构。

要实现上面提到的对系统的SI和时序的仿真,那么需要的基本的信息就是Buffer的I/V曲线和转换特性。IBIS模型中Buffer的数据信息可以通过测量器件得出也可以通过器件的SPICE模型转换得到。IBIS是一个简单的模型,当做简单的带负载仿真时,比相应的全Spice三极管级模型仿真要节省10~15倍的计算量。

IBIS 模型是基于器件的,就是说一个IBIS 模型是对于整个器件的管脚而言的,而不是几个特殊的输入、输出或者是I/O 管脚的Buffer。因此IBIS 模型中除了一些器件Buffer的电气特性,还包括引脚pin与buffer 的映射关系(除了电源、地和没有连接的管脚,每个管脚都有一个特定的Buffer),以及器件的封装参数。

IBIS提供两条完整的V-I曲线,分别代表驱动器为高电平和低电平状态,以及在确定的转换速度下状态转换的曲线。V-I曲线的作用在于为IBIS提供保护二极管、TTL推拉驱动源以及射极跟随输出等非线性效应的建模能力。一般而言,IC器件的输入、输出和I/O 管脚的Buffer的行为特性是通过一定的形式描述的。下面分别对于输入、输出和I/O 管脚Buffer 的表述形式作一个介绍。

对于一个输出或者是I/O 管脚的Buffer需要下列的相关数据:

1、输出为逻辑低时,输出管脚Buffer 的I/V 特性;

2、输出为逻辑高时,输出管脚Buffer 的I/V 特性;

3、输出电平强制在Vcc以上和GND以下时,输出管脚Buffer的I/V 特性;

4、Buffer由一个状态转换为另一个状态的转换时间;

5、Buffer的输出电容。

对于一个输入管脚的Buffer 需要以下的数据:

1、输入Buffer 的I/V 曲线(包括电平高于Vcc 或者是低于GND);

2、Buffer的输入电容

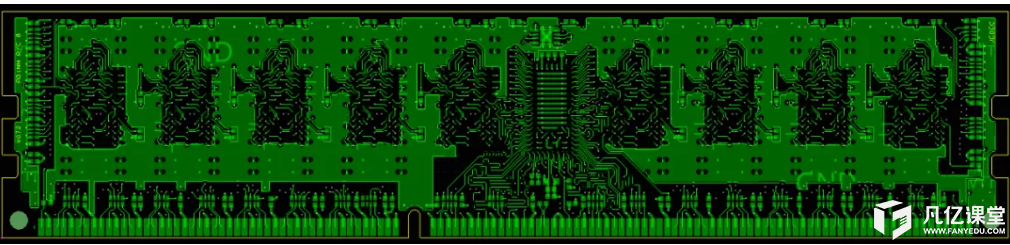

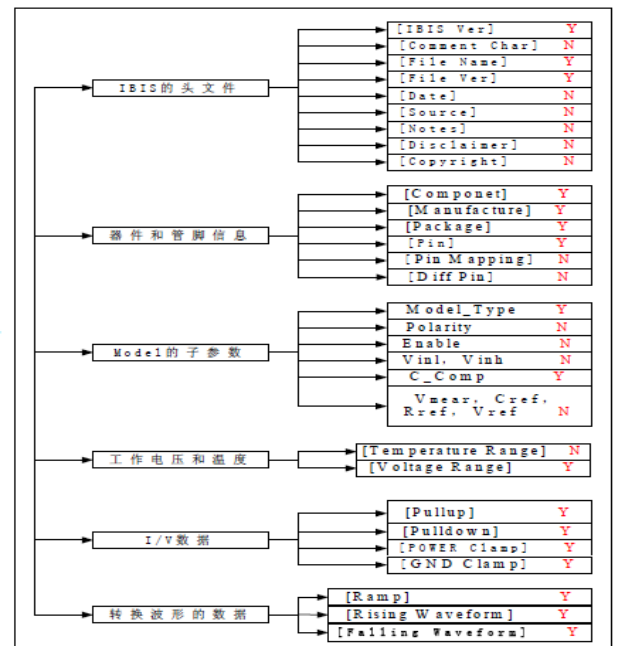

一般情况,IBIS 模型包含以下一些信息,IBIS 模型的结构如下图1 所示。

1、关于文件本身和器件名字的信息。这些信息用以下的关键词描述: [IBIS Ver] IBIS的版本号, [File Name]文件的名称,[File Rev]文件的版号,[Component]器件的名称,[Manufacturer]器件制造商;

2、关于器件的封装电气特性和管脚与Buffer模型的映射关系。可以使用关键词[Package]和[Pin]描述。

3、为表述器件管脚Buffer所需要的相关数据信息。关键词[Model]用来表示每个Buffer的数据,具体内容有:Model_type表示Buffer的类型,Vinh、Vinl表示高低电平,C_comp表示IC芯片的电容。在前面的内容中提到了Buffer的特性描述,在IBIS模型中需要下面的一些关键词描述:[Pull-up]、[Pull-down]、[GND clamp]、[Power clamp]和[Ramp]。当然对于不同的Buffer可能不需要上面的全部的关键词来描述。如OC和漏极开路电路就不需要[Pull-up]关键词的数据信息。

图1:右半部分内容是IBIS 模型中的关键词,没有方括号的条目则代表的是子参数的标题。同时对于红颜色的字符“Y”标明在IBIS 模型中是必选项;而“N”则是标明该内容在IBIS 模型中为任选项。