凡亿教育-江江

凡事用心,一起进步打开APP

公司名片CMOS集成电路异常漏电失效现象有哪些?

CMSO集成电路是电子工程师最熟悉了解的大类电路之一,在设计CMOS电路时工程师都会考虑不少减少漏电的因素,但工作过程中不难发现部分电路依然存在异常漏电现象,所以我们今天来盘点CMOS集成电路异常漏电失效现象,看看是否哪方面没做好。

1、故障复现方法

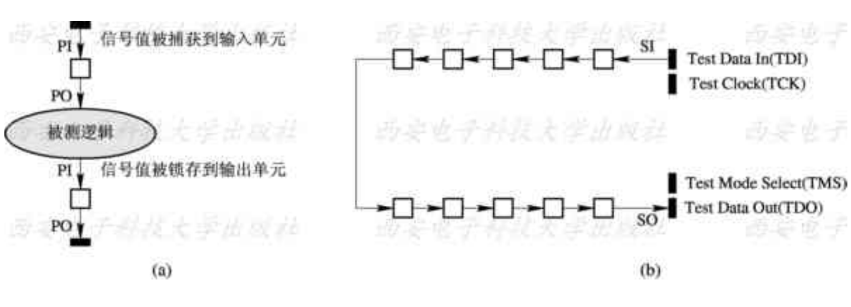

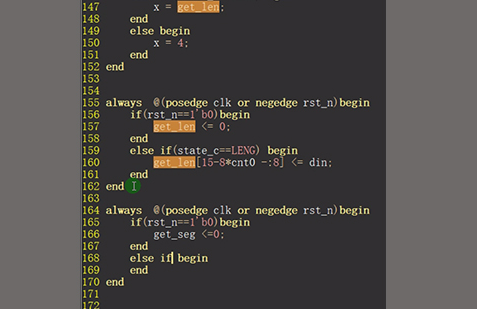

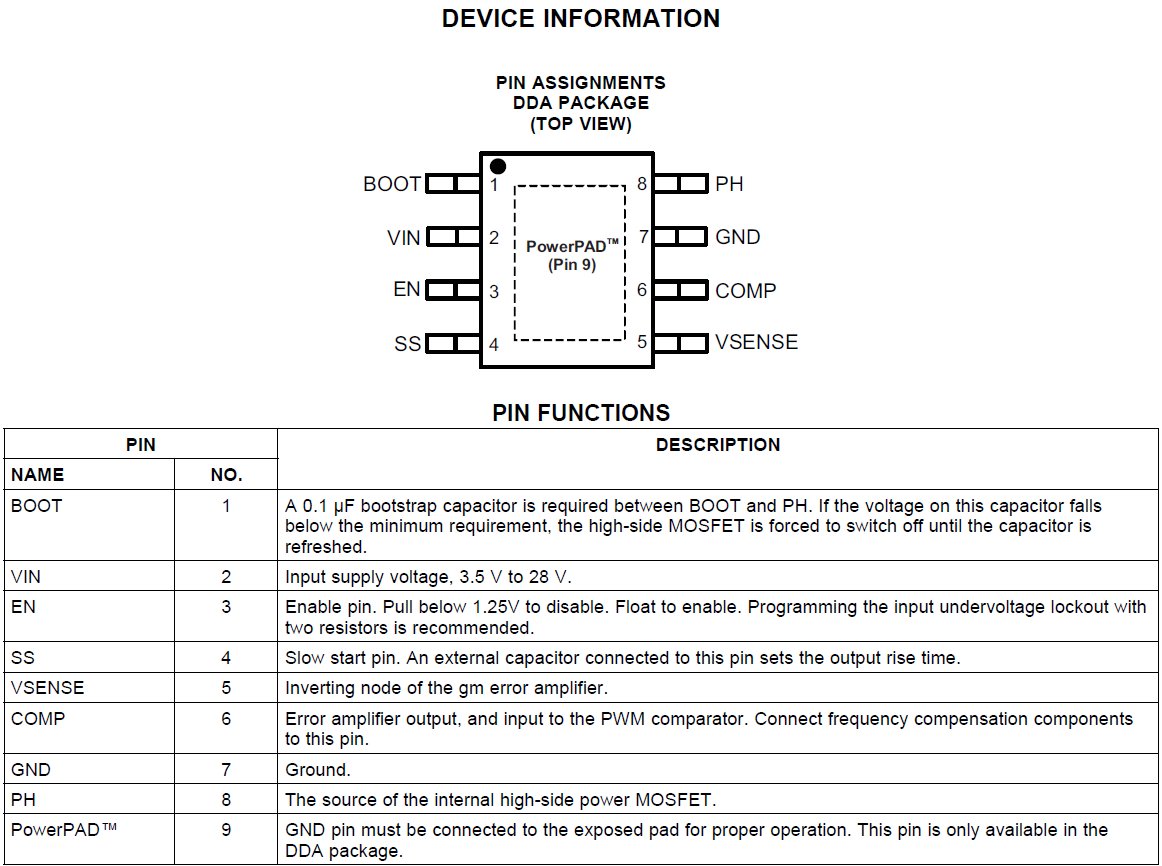

通常在进行集成电路失效分析时要对失效样品的失效模式进行验证,验证的主要方法是用测试设备进行测试以及用I-V特性图示仪进行管脚之间的I-V特性测量分析。

通常,用测试设备进行测试的流程如下:

(1)首先进行接触性测试(又称开路、短路测试),以确定被测器件的输入、输出端与测试系统接触良好。.

(2)功能测试,一般先进行正常工作电源电压下的功能测试,再进行电源拉偏测试。

(3)静态(直流)、动态(交流)参数测试。

通过测试设备的测试(有时对测试程序进行裁减)以及管脚之间的I-V特性测试分析就可判断出电路是否己失效。

2、失效现象

(1)原始失效现象:委托方提供的测试数据表明电路短路失效。

(2)测试仪复测:用数字信号测试系统进行复测,发现管脚连接未能通过,对地短路。同时也发现改变测试设置后出现管脚对地短路不固定的状态。

(3) I-V特性测试:用半导体参数测试仪在小电压下测量管脚组合的I-V特性,一般不会出现短路现象,但有时也会出现短路现象,但会消失。

(4)将电路开帽后在显微镜下观察:压焊丝、压焊点正常,芯片表面无异常。

(5)在扫描电镜下对怀疑范围进行表面和EBIC观察分析,未发现结有明显异常。

可见电测试结果和物理观察分析的结果是不能对应的,失效机理不明确。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表凡亿课堂立场。文章及其配图仅供工程师学习之用,如有内容图片侵权或者其他问题,请联系本站作侵删。

相关阅读

进入分区查看更多精彩内容>

暂无评论