很多人在PCB电路设计中都会尽量做到减小EMC影响,保证电路达到最佳效率,能够作为成品从而上市,但在该过程中必然带来多种疑问,所以本文将搜集平台上多个关于PCB电路设计和EMC设计的问题,并进行回答。

1、做PCB板时,为减小干扰,地线有必要采用闭合形式?

在做PCB板时,一般来讲都要减小回路面积,以便减少干扰,布地线时,也不应布成闭合形式,而是布成树枝状较好,还有就是尽可能增大地面积。

2、在EMC测试中发现时钟信号的谐波超标严重,若是在电源引脚上连接去耦电容,那么在PCB设计中需要注意哪些方面来抑制电磁辐射?

一般来说,EMC的三要素是辐射源、传播途径和守海提,传播途径分为空间辐射传播和电缆传导,所以要抑制谐波,首先先看看传播途径,电源去耦是解决传导方式传播,此外必要的匹配和屏蔽也是需要的手段。

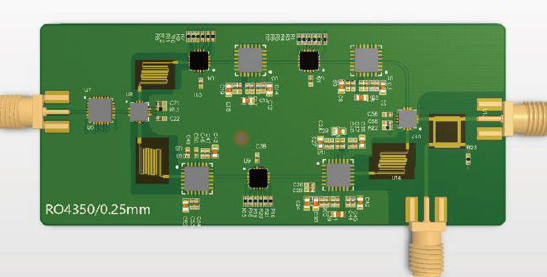

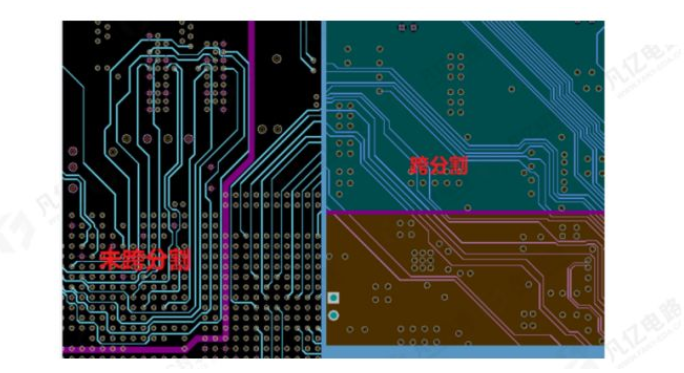

3、在PCB设计中,通常将地线分为保护地和信号地;电源地又分为数字地和模拟地,为什么要对地线进行划分?

划分地的目的主要是处于EMC的考虑,担心数字部分电源和地上的噪声会对其他信号,特别是模拟信号通过传导途径有干扰。至于信号和保护地的划分,是因为EMC中ESD静放电的考虑,类似于我们生活中避雷针接地的作用。无论怎样分,最终的大地只有一个,只是噪声泄放途径不同而已。

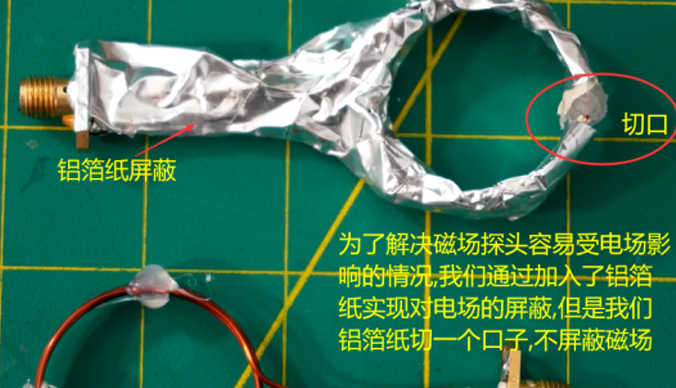

4、PCB设计中,在布置时钟时,有必要两边加地线屏蔽吗?

是否加屏蔽地线要根据板上的串扰/EMI情况来决定,而且如对屏蔽地线的处理不好,有可能反而会使情况更糟。

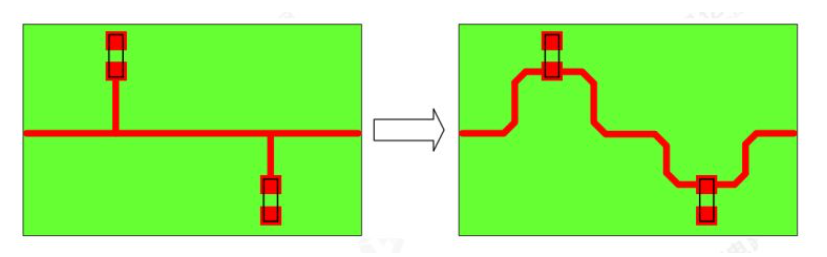

5、在PCB布线时,电源的分布和布线是否要像地线那样注意,若是不注意将带来什么问题?

电源若是作为平面层处理,其方式应类似于地层的处理,当然,为了降低电源的共模辐射,建议内缩20倍的电源层距底层的高度。如果布线,建议走树状结构,注意避免电源环路问题,电源闭环将引起较大的共模辐射。

暂无评论