EMC:Electro Magnetic Compatibility的简称,也称电磁兼容,各种电气或电子设备在电磁环境复杂的共同空间中,以规定的安全系数满足设计要求的正常工作能力。

本章对于 RK3588产品设计中的 ESD/EMI防护设计及EMC的设计检查给出了建议,帮助大家更好的提高产品的抗静电、抗电磁干扰水平。

EMC设计检查建议

按照设计流程,一个产品Layout完成之后,需要进入严格的评审环节,所设计的产品是否满足ESD或者EMI防护设计要求,撇开原理图设计,PCB设计一般需要我们从PCB布局和PCB布线两个方面进行审查,本小节就这两方面的检查做了建议,读者可以此作为审核PCB Layout人员的PCB的参考标准。

EMC设计布局检查建议

1、整体布局检查建议

1)模拟、数字、电源、保护电路要分开,立体面上不要有重叠;

2)高速、中速、低速电路要分开;

3)强电流、高电压、强辐射元器件远离弱电流、低电压、敏感元器件;

4)多层板设计,必须要有单独的电源平面和地平面;

5)对热敏感的元件(含液态介质电容、晶振)尽量远离大功率的元器件、散热器等热源。

2、接口与保护布局检查建议

1)一般电源防雷保护器件的顺序是:压敏电阻→保险丝→抑制二极管→EMI滤波器→电感或者共模电感,对于原理图缺失上面任一器件进行顺延布局;

2)一般对接口信号的保护器件的顺序是:ESD(TVS管)→隔离变压器→共模电感→电容→电阻,对于原理图缺失上面任一器件进行顺延布局;

3)电平变换芯片(如RS232)要靠近连接器的位置(如串口)放置;

4)易受ESD干扰的器件,如NMOS、CMOS器件等,要尽量远离易受ESD干扰的区域(如单板的边缘区域)。

3、时钟电路布局检查建议

1)时钟电路的滤波器(尽量采用“∏”型滤波)要靠近时钟电路的电源输入管脚;

2)晶体、晶振和时钟分配器的布局要注意远离大功率的元器件、散热器等发热的器件;

3)晶体、晶振和时钟分配器与相关的IC器件要尽量靠近;

4)晶振距离板边和接口器件要大于1inch的距离。

4、开关电源布局检查建议

1)开关电源要远离AD\DA转换器、模拟器件、敏感器件、时钟器件;

2)严格按照原理图的要求进行布局,不要将开关电源的电容随意放置;

3)开关电源布局要紧凑,输入\输出要分开。

5、电容与滤波器件布局检查建议

1)原则上每个电源管脚放置一个0.1uf的小电容、一个集成电路放置一个或多个10uf大电容,可以根据具体情况进行增减;

2)电容务必要靠近电源管脚放置,而且容值越小的电容要越靠近电源管脚;

3)EMI滤波器要靠近芯片电源的输入口。

6、叠层检查建议

1)多层板(四层以上)至少有一个连续完整的地平面用来控制PCB的阻抗和信号质量;

2)电源平面和地平面靠近放置;

3)叠层尽量避免两个信号层相邻,如果相邻加大两个信号层的间距,并且布线时应该错位布线,不能重叠布线,否侧后期布线可能会引起串扰的产生;

4)避免两个电源平面相邻,特别是由于信号层铺电源而导致的电源平面相邻;

5)外层铺地。

7、其他设计检查建议

1)整机设计为浮地设备时,建议各接口不要分地设计;

2)机器外壳为金属时,电源是三孔,要求金属外壳必须良好连接大地。

EMC设计布线检查建议

1、整体布线检查建议

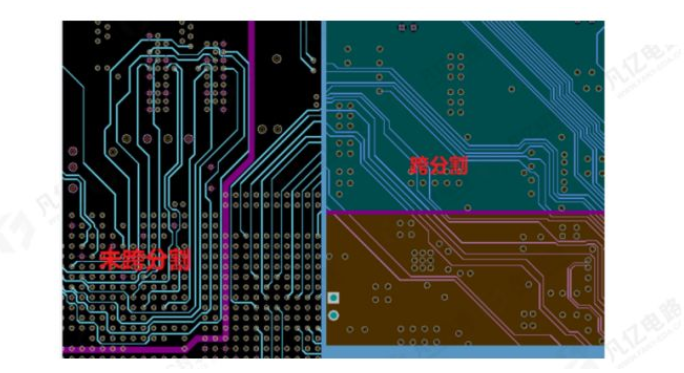

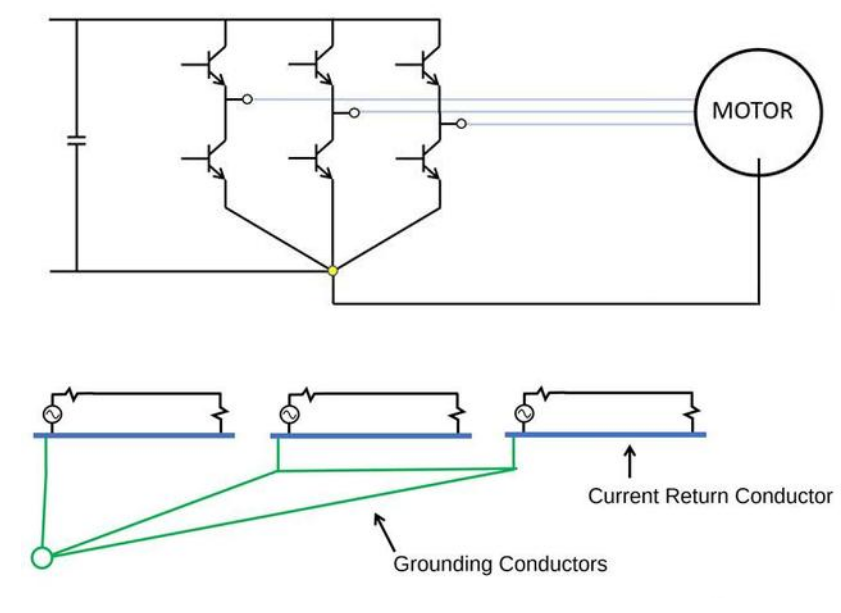

1)关键信号线走线避免跨分割

我们PCB中的信号都是阻抗线,是有参考的平面层,对于设计的关键信号避免跨分割的现象出现,否则会导致信号阻抗的突变,导致信号完整性问题的出现。如图10,描述了信号跨分割的现象。

图10 信号跨分割

2)相同功能的总线要并行走、中间不要夹叉其它信号,如果空间允许可以进行包地处理;

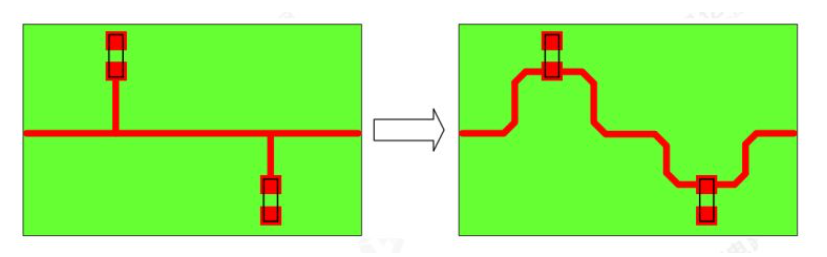

3)关键信号线走线避免“U”型或“O”型;

4)关键信号线走线不要人为的绕长(以最短路径进行走线);

5)关键信号线需要距离边沿和接口400mil以上;

6)晶振下面所有层都不能走线;

7)开关电源下面不能走线,特别是电感或转换芯片下方;

8)接收和发送信号要分开走,不能互相交叉布线。

2、隔离与保护

1)浪涌抑制器件(TVS管、压敏电阻)对应的信号走线尽量表层,短且粗(一般10mil以上);

2)不同接口之间的走线要清晰,不要互相交叉布线;

3)接口线到所连接的保护和滤波器件布线要尽量短;

4)接口线必需要先经过保护或滤波器件再到信号接收芯片;

5)接口器件的固定孔要接到保护地上,连接到机壳的定位孔、扳手要直接接到信号地;

6)变压器、光耦等器件的输入输出地要分开处理(两端使用不同的GND);

3、时钟布线

1)超过1inch的时钟线尽量走在内层,时钟线采用立体包地处理;

2)时钟线换层为不同的地参考平面需要增加回流地过孔;

3)时钟线不允许跨分割;

4)时钟线与其它信号线的间距达到5W,空间允许的情况下可以进行包地处理。

5)时钟电路的电源走线需要加宽或铺铜处理;

4、其他

1)保护地和信号地之间的间距大于80mil;

2)DC48V的爬电间距是否为80mil以上;

3)电源平面要比地平面内缩“20H”(H为电源和地平面的距离),一般情况地内缩20mil,电源需要内缩60mil,并间隔150mil打地过孔;

4)布线要避免出线Stub线,Stub线就是俗称的线头或歪线, 或者说信号没打算经过的路径;

5)AC220V的爬电间距最少为300mil,具体可以查爬电间距规格表;

6)差分走线可以抑制共模干扰;

7)敏感的信号线必须采用包地处理,包地线每隔200mil增加一个GND孔。

声明:本文转载自凡亿电路 公众号,如涉及作品内容、版权和其它问题,请于联系工作人员微,我们将在第一时间和您对接删除处理!

暂无评论