凡亿教育-媛媛

凡事用心,一起进步打开APP

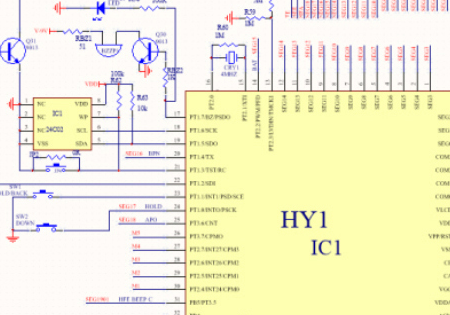

公司名片电路设计如何配置去耦电容?

随着微电子技术的发展,越来越多的电子产品急需高性能来处理高数据量问题,这也促使电路设计愈发复杂,以适应多种不同的需求变化,这也充分考验电子工程师的设计能力和理论能力。其中之一是电路设计时应如何配置去耦电容?

在直流电源回路中,负载的变化都会引起电源噪声,如在数字电路中,当电路从一个状态转换为另一种状态时,将会在电源线上产生一个很大的尖峰电流。形成瞬变的噪声电压,配置去耦电容可抑制因负载变化而产生的的噪声,是印制电路板的可靠性设计的一种常规做法,配置原则如下:

1、电源输入端跨接一个10-100uF的电解电容器,如果印制电路板的位置允许,采用100uF以上的电解电容器的抗干扰效果会更好。

2、为每个集成电路芯片配置一个0.01uF的陶瓷电容器,如遇到印制电路板空间小而装不下时,可每4-10个芯片配置一个1-10uF钽电解电容器,这种器件的高频阻抗特别小,在500kHz-20MHz范围内阻抗小于1Ω,而且漏电流很小(0.5uA以下)。

3、对于噪声能力弱,关断时电流辩护大的器件和ROM、RAM等存储型器件,应在芯片的电源线(Vcc)和地线(GND)间直接接入去耦电容。

4、去耦电容的引线不能过长,特别是高频旁路电容不能带引线。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表凡亿课堂立场。文章及其配图仅供工程师学习之用,如有内容图片侵权或者其他问题,请联系本站作侵删。

相关阅读

进入分区查看更多精彩内容>

暂无评论