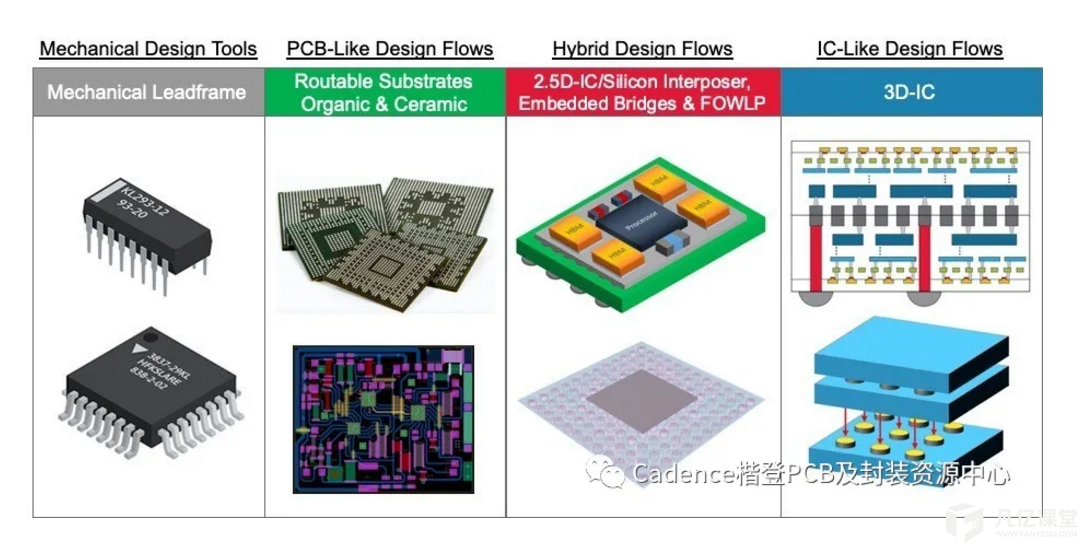

首先,如上图所示,封装设计有许多处理方法:

采用以机械引线框设计封装本身

采用可布线的有机和陶瓷基板设计封装,这是一种PCB风格的设计流程

设计2.5D硅中介层、嵌入式桥和扇出型晶圆级封装(FOWLP)的混合设计流程

采用集成电路类设计流程设计具有硅穿孔(通常)的3D集成电路

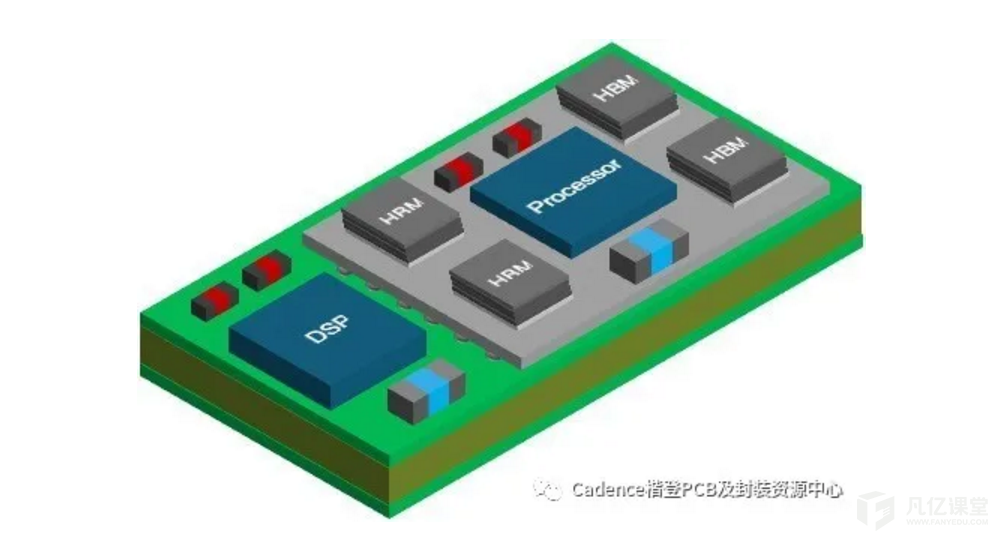

下一代封装的异质性可能更高,例如,将3D堆叠放在2.5D硅中介层上,如上图所示,而2.5D硅中介层又放在具有更多器件的有机中介层上。

这种类型的设计会面临许多挑战:

顶级设计聚合和管理

预布局规划

顶层(芯片到芯片到封装到PCB)网表定义

系统级I/O优化

理解芯片/chiplet提取/表示的正确层级

简单(范围和引脚位置)

复杂(全芯片/chiplet)

先进的多芯片/chiplet集成电路封装需要专门的验证

由顶层管理工具驱动的布局与原理图(LVS)连接验证

高级芯片间对准检查

硅基底设计和验证方法

跨域电/热建模

模拟域间的耦合效应

为集成电路、封装和PCB连接不同的提取工具

实现和签核

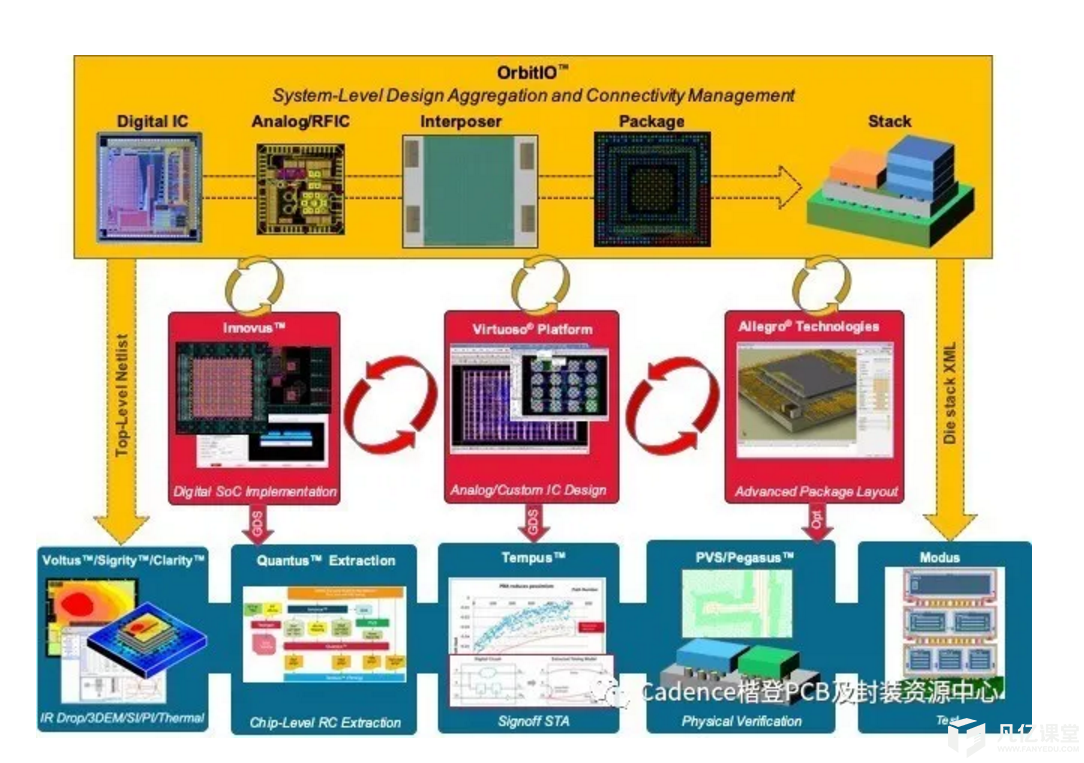

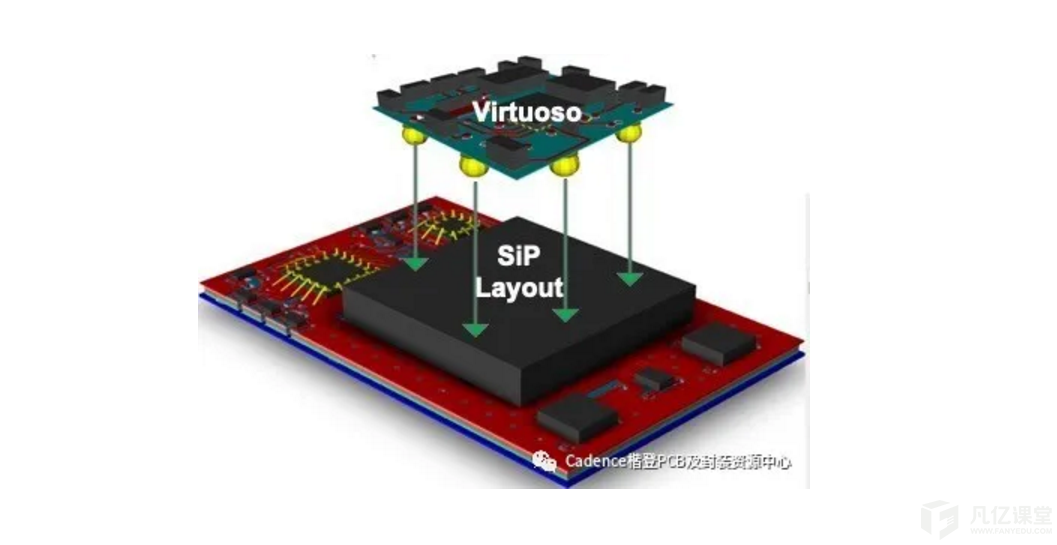

Cadence OrbitIO™ 软件是为规划、优化和管理设计专门打造的工具,用以处理顶级原理图、网表以及所有芯片堆叠。再通过Cadence的实现工具组合来具体实现:Innovus™、Virtuoso®以及Allegro®。此外,还有一套提取、验证和签核工具:Voltus™、Sigrity™、Clarity™、Celsius™等软件。

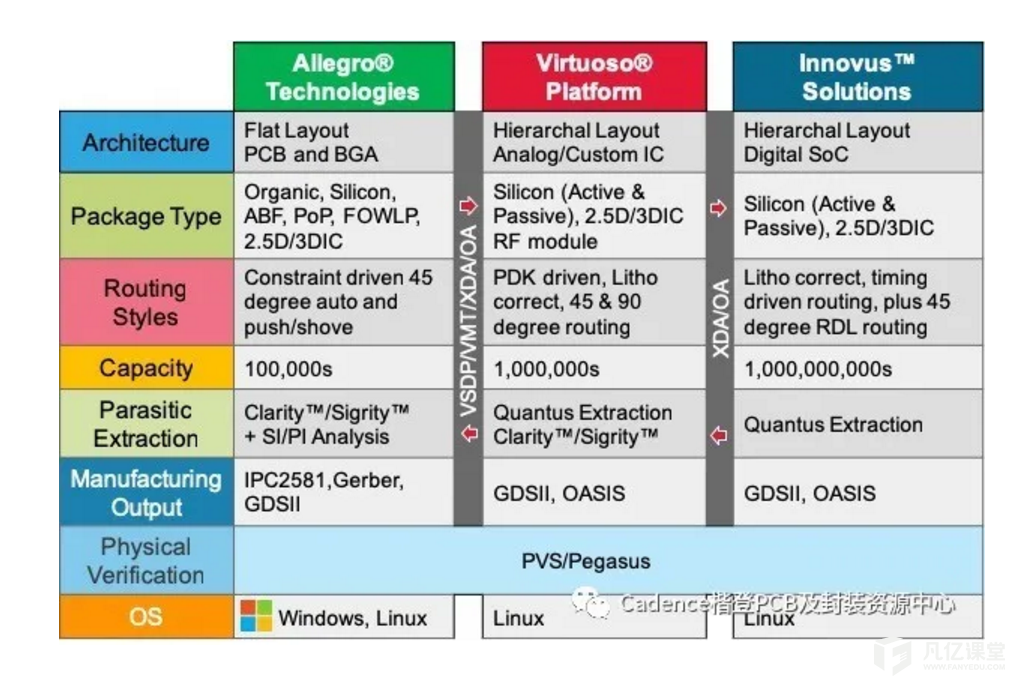

何种实现和验证平台最合适取决于设计风格,即在很大程度上取决于是否类似PCB设计(在这种情况下,Allegro和Sigrity等工具是最佳选择),或者是否类似集成电路设计(在这种情况下,Innovus和Voltus等工具是最佳选择)。上表深入说明了所涉及权衡的更多细节。

所有的多芯片工具都可以处理多个PDK,因为芯片通常采用不同的技术,但需要一起分析。例如,也可以通过SiP的context打开Virtuoso的IC设计来检查(或更改)芯片。数据库是共享的,因此不必一直从一个工具中写出文件,然后再将它们读回到另一个工具中。虽然每个工具都有独特的功能,但它们都有跨平台的功能。

通过本文无法介绍完所有工具的功能,尤其是在工具涵盖范围极其广泛的情况下,即包括机械建模、PCB设计、集成电路设计、片上信号完整性、板级和封装级信号完整性、热电建模、射频、硅光子学......事实上,几乎涵盖了Cadence的所有EDA技术。

分解式系统级芯片

系统级封装(SiP)正在成为新的系统级芯片(SoC)。这是因为它们都是集成方法,但更重要的是,系统级封装最具成本效益,且最高效。根据定义,在系统级芯片中,一切都必须采用同一制程。自芯片尺寸足以容纳微处理器和所有支持逻辑以来,这一直都是主要的集成方法。但现在,并非每个逻辑功能都需要采用同一制程。还有一些标准化chiplet接口的举措,借此,使用系统级封装方法来构建分解式系统级芯片将变得更加简单。

Cadence与合作伙伴在3D集成电路方面的合作已有十多年,已经完成了10多项测试设计,包括多项生产流片和系统级封装设计;更多项目仍在进行中,欢迎大家持续关注。

暂无评论