凡亿助教-姗慧

凡事用心,一起进步打开APP

公司名片高速电路的理解及信号的完整性

高速电路的定义:

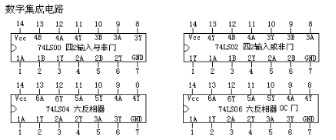

1)一个是从频率上来讲的含义频率高,通常认为如果数字逻辑电路设计的频率达到或超过20MH(有的说10MHz),而且工作在这个频率的电路已占整个电子系统一定的份量(常说三分之一),则称为高速电路

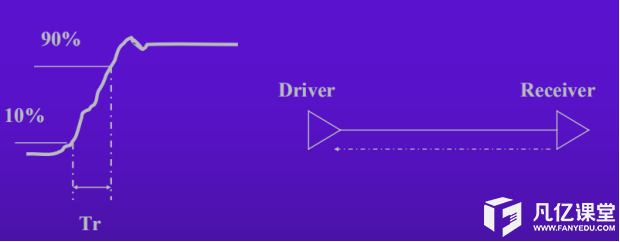

2)另一个是指数字信号的上升沿与下降沿(有时称信号的跳变)非常快,当信号的上升沿时间小于6倍(有说4倍)信号传输延时时即认为信号是高速信号,而与信号的频率无关。

高速电路的理解:

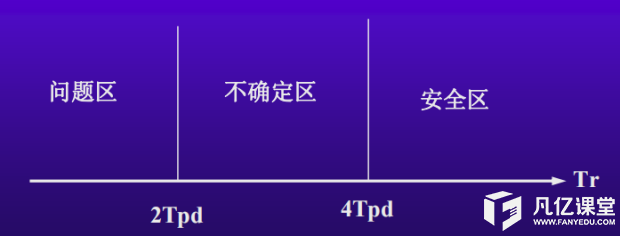

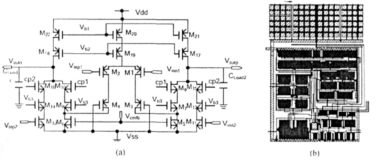

上面两个概念的定义都有点偏严,现在很多人都不会再把10M20M放在心里,30M、50M也是常有人说;大家主要是能理解这个概念就行了。Tr<6Tpd也是偏严了点,Trs4Tpd比较合理,Tr<2Tpd是理论值有点太松,实际因素太多有很大不确定性,把4Tpd≥Tr≥2Tpd归为不确定区,Tr≤2Tpd有间题区,。以Tr=4ns为例,结合集总参数来加强理解。

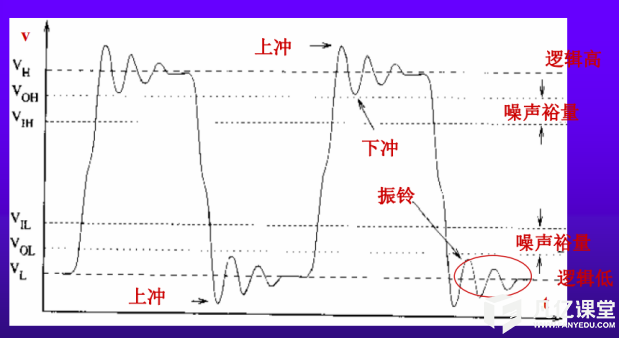

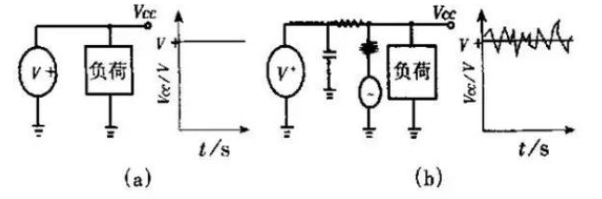

信号从驱动端到接收端需要一定的时间(Tpd),如果传输时间小于1/2的上升或下降时间(Tr),那么来自接收端的反射信号将在信号改变状态之前到达驱动端。反之,反射信号将在信号改变状态之后到达驱动端。如果反射信号很强,叠加的波形就有可能会改变逻辑状态,就是我们常说的过冲、振铃等信号完整性问题。

信号的完整性概念:

信号完整性( Signal Integrity,简称SI)是指在信号线上的信号质量。表示信号质量和信号经传输媒质传输后仍保持正确的功能特性,也就是要求信号从源端经过传输媒质后必须把信息完整无误的传送到负载端。例如我们要求传送一个高电平逻辑1,这就要求负载段必须正确得接受到高电平逻辑1。然而由于我们设计的速度越来越高,再加上各种其他不利的因素,造成负载端接受到的为逻辑0,这就出现了我们说的信号完整性问题。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表凡亿课堂立场。文章及其配图仅供工程师学习之用,如有内容图片侵权或者其他问题,请联系本站作侵删。

相关阅读

进入分区查看更多精彩内容>

暂无评论