在使用CH340芯片进行电路设计时,我们应该注意哪些细节与事项呢?接下来我们一起来看看。

CH340芯片通过USB转换出来的TTL串口输出和输入电压是根据芯片供电电压是自适应的。也即,如果芯片是5V供电,那么串口输出和采样都是5V;如果是3.3V供电,那么标准就成了3.3V,因此在实际使用的时候,电路设计串口连接到的对端设备需要注意电压匹配的问题。其中在5V供电模式下,是可以与3.3V系统兼容的,反过来则不可以,如果CH340是3.3V供电,那么不可以接5V系统,会损坏芯片。另外如果对端是1.8V系统,那么是不能与CH340的3.3V模式兼容的,此时输出和采样会出错。最好加一些器件来升降压来进行电压匹配。因此设计时确认好对端串口电平范围,然后决定CH340工作在3.3V或者5V工作模式。在电路设计原理上,5V供电时芯片V3引脚需要接一个104电容到地,3.3V供电时直接将V3脚与3.3V电源引脚短接就可以了。

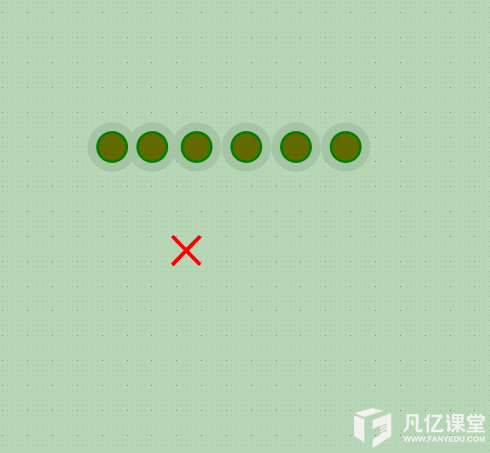

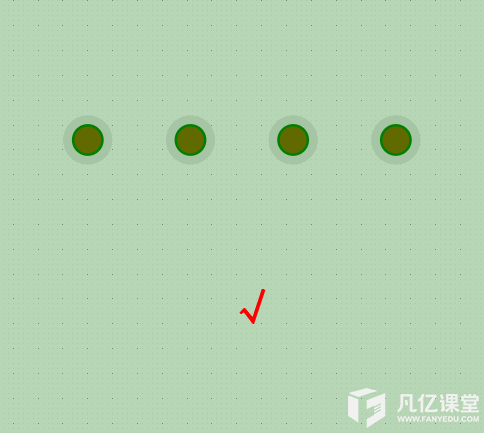

在实际应用中,当CH340与其他IC譬如MCU等器件一同使用时,如果串口直连的双方器件有一方不需要供电工作时,要注意电流倒灌导致未供电的芯片继续工作的情况,或者是在串口下载场景中,当MCU需要复位以实现下载时,发现复位不成功,可能也是由于该原因造成的。因此,在电路设计中可以做如下改动来防止CH340与对端IC出现任何一方被倒灌电的情况。

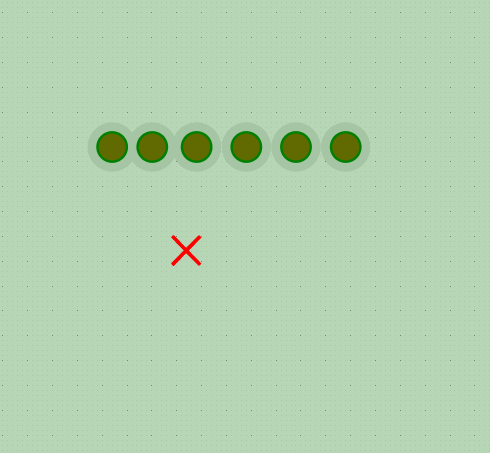

也就是在CH340芯片的发送引脚TXD上接一个反向二极管,然后再连接到对端IC。在接收引脚上加一个限流电阻来防止对端IC对CH340倒灌电。

通过反向二极管的原理是:在CH340发送数据时,发送高电平时二极管截止,但是由于对端RXD默认上拉也是高电平不会有采样问题,而发送低电平时二极管导通,对端RXD接收到低电平,因此可以正常通讯。并防止了CH340的TXD发送引脚将电流倒灌到对端IC。

通过限流电阻的原理是:倒灌电流导致芯片工作甚至闩锁效应,是由于引脚电流过大超过了芯片设计时容忍的上限导致芯片内部电路出现异常。因此加一个限流电阻就可以了,其他通讯场景也可以仿照此方法进行尝试。

对于CH340系列需要外部晶振的芯片,在选用晶振时如果选择12MHz的石英晶体,那么电路设计旁路电容选择22pF的独石或高频瓷片电容。如果选用的低成本陶瓷晶体,那么旁路电路的容量必须用该晶体厂家的推荐值,一般情况下是47pF。对起振困难的晶体,建议电容数值减半。如果仍然无法起振,最好参考一下选用晶振的官方推荐电容值。

V3的引脚除了在不同电压供电模式下接法不同,对于电容数值选用也是需要注意的。V3引脚的电容用于内部电源节点退耦,来改善USB传输过程中的EMI,通常容量在4700pF到0.1uF范围,建议容量为0.01uF,即103电容。

因为USB信号属于模拟信号,所以在CH340等USB芯片内部包含数字电路和一些模拟电路,另外,USB芯片中还包含时钟震荡及PLL倍频电路,电路的公共地端在芯片内部已经连接在一起并连接到芯片的GND引脚。

如果USB芯片有时工作不正常、或者USB数据传输随机性失败、或者抗干扰能力差,那么就应该考虑USB芯片是否稳定工作。影响USB芯片工作稳定性的几大因素有:

时钟信号不稳定-这是主要原因,下面将详细分析。

时钟信号受干扰-解决方法:PCB设计时尽量不再晶体及震荡电容附近走线,尤其是不要走继电器、电动机等带有瞬时冲击电流的电源线和强信号线;在晶体及震荡电容周边布置GND铺铜屏蔽干扰;将晶体外壳接地(任何需要晶体工作的电流都可以这样设计);或者使用有源晶振等。

USB信号受干扰-解决办法:PCB设计时使USB信号线D+与D-平行布线,最好在两侧布置GND铺铜,减少干扰。使用符合USB规范的带屏蔽层的传输线,不能使用普通排线或者非USB线缆。

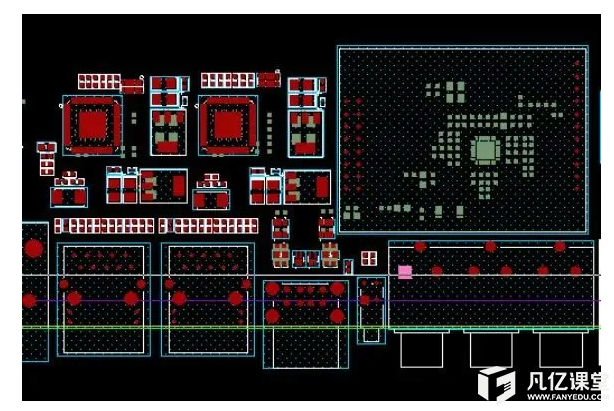

时钟信号不稳定通常是PCB布线中GND走线不佳。设计电路及PCB时应该尽量避免这6个GND点之间存在电压差(主要是指数字电路中的高频毛刺电压,也就是数字噪声)。

解决方法是:

1.尽量缩短这6个点之间的距离;

2.类似模拟电路设计中的单点接地;

3.大面积GND铺铜及GND多点过孔VIA降低高频信号阻抗。可以用示波器探头接D点测量时钟输入端XI引脚的12MHz时钟波形是否有抖动。

暂无评论