凡亿助教-小美

凡事用心,一起进步打开APP

公司名片CMOS电路的版图制作环节详解

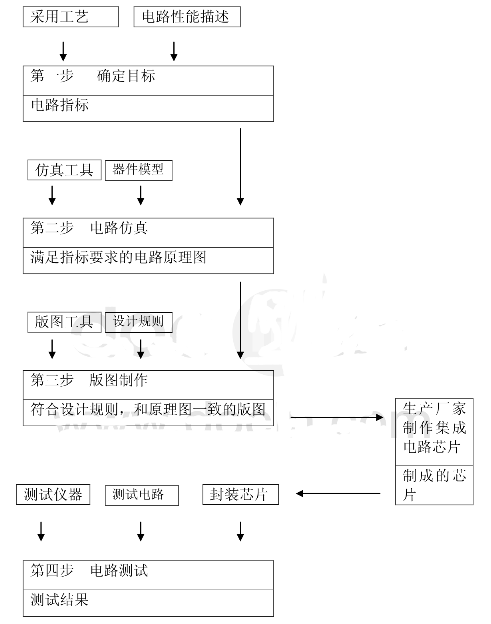

之前我们聊了下CMOS电路设计流程,然后很多粉丝私聊我询问CMOS电路的版图制作该如何做好,今天就谈谈CMOS电路如何做包版图制作,希望对各位小伙伴们有所帮助。

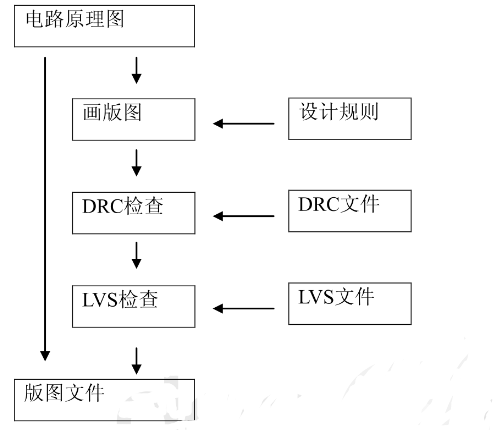

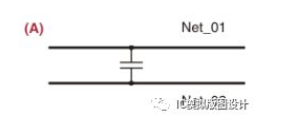

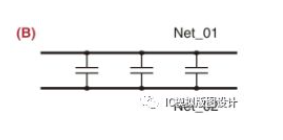

如图所示,该图是工程师根据电路原理图画出对应的版图,其实就是把对应的器件摆好,完成连线,因为电路的制造精度是有限的,所以版图必须满足一定的要求,举个简单的例子来说,电路中两条导线必须保持一定的间距,否则它们将连在一起,这些电路制造中的种种限制归纳在一起就是版图设计规则。

按照设计规则画完版图之后,接着就要对它进行检查。因为版图是由人来画的,所以不可避免地存在或多或少的错误,这时就由软件来进行“设计规则检查”(Design Rule Check,DRC)。软件检查所依据的是DRC文件,它和画版图时使用的规则是一致的只不过规则文件是给版图设计者参考用的,而 DRC文件则是为软件编写的。

当版图没有DRC错误,完全合乎设计规则后,再依靠LVS文件,将它和电路原理图进行比较。如果两者不同,说明版图存在错误,经过修改之后还要重复DRC、LVS的过程。如果两者相同,说明版图和原理图一致,到这一步就完成了版图的制作。完成版图后,可以利用工具提取版图中的寄生参数,对包含这些寄生参数的电路再次进行仿真,从而更准确确定电路的性能。

最后把图形格式的版图文件转换成通用格式的二进制文件(GDS文件),提交给生产厂商制作。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表凡亿课堂立场。文章及其配图仅供工程师学习之用,如有内容图片侵权或者其他问题,请联系本站作侵删。

相关阅读

进入分区查看更多精彩内容>

暂无评论