如果电子工程师接到了关于MOS集成运放的版图设计任务,为保证项目顺利完成,我们该如何合理设计,确定思路和方法来设计出更好的产品?也许可以看看这篇文来得到灵感。

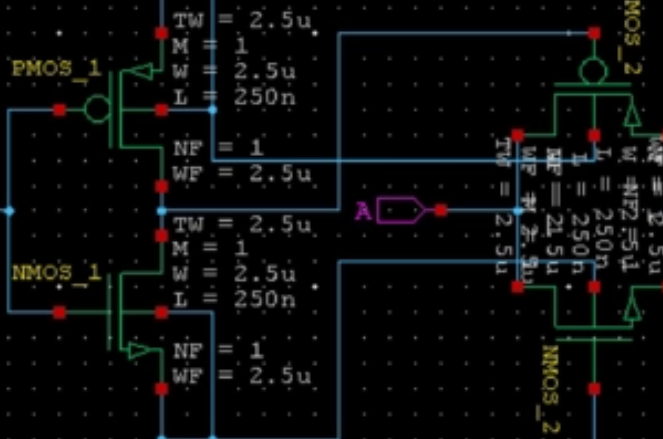

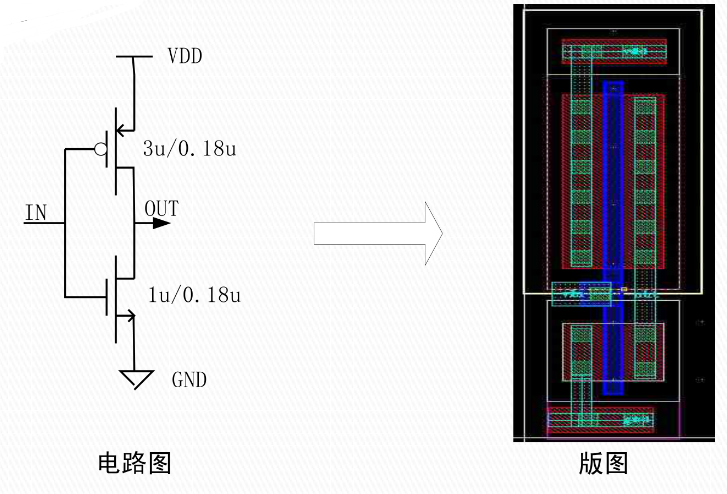

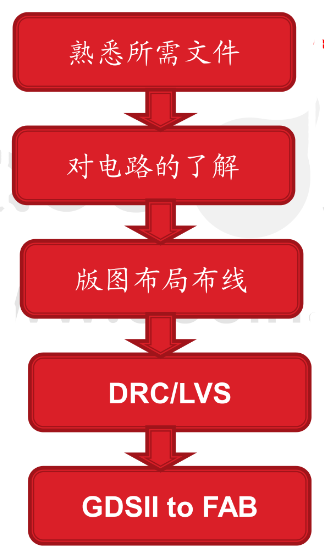

MOS运放的版图设计过程:先进行电路分析,计算出各端点的电压及各管的电流,从而求出各管的W/L,进而设计各管图形,进行布局布线,完成版图设计。

版图设计的一般要求具体如下:

1、布局要合理

布局是否合理将对许多指标产生重要影响,考虑布局合理性的标准是各引出端的分布是否与有关电容兼容(既要通用);有特要求的单元(如输入对管等)是否做了合理的安排;布局是否紧凑;温度分布是否合适。

2、单元配置要适当

即逻辑门到管子的安放位置和方向要核实,它不仅包括单元具体形状的 确定,也包括单元方位的选择。如:对于一定尺寸的管子或反相器究竟画成什么形状,按什么方向安放,可有多种方式,不同做法将对于电路性能、芯片面积紧凑程度、连线长度等产生很大影响,由于CAD已广泛用于集成电路的版图设计,所以在设计中应尽量使用重复单元,以便于计算辅助设计和差错。

3、布线要合理

这点在MOS运放版图设计中较为重要,这不仅是因为电路中布线所占的面积往往是其元件总面积的好几倍,而且由于小尺寸MOSFET构成的电路线延迟是最小的,此时布线的RC时间常数将是电路工作速度的主要限制因素。

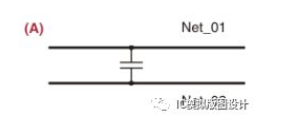

对于硅栅MOS集成电路,由于已经有了两层布线,通常不再把避免或减小布线交叉作为重要的布线指标。在硅栅MOS集成电路中,主要的布线是绿线和多晶硅线,通常是以一种作为水平方向布线,而另外一种作为垂直方向的布线。这样做,不仅可以是板面调整,而且可以减小两层间的寄生电容。要根据流过电流的大小及性能要求,选择连线种类。要尽量减小布线长度,特别是减小细连线的长度。对于电源线和地线,必须保证足够的宽度,且应是网状或枝状布满整个芯片,对于那些要防止互相引起串扰的布线,一定要远离,不可靠拢并行。

由于整个硅片表面起伏不平,因此在铝布线时尽量避免铝线的爬坡梯度过大,由最低处到最高处要分几个台阶过渡。

为便于检查工艺质量,版图上要安排大量的测试图形,此外,在MOS运放的设计中,对电路中对称部分,如输入差分放大器,在版图上尽量对称(包括尺寸、位置、方向等),以减小输入失调。为了减小S,D,G区面积,沟道宽度W大的MOS管,多采用U形栅布局。为保证电阻比和电容比的精度,不同数值的电阻和电容,通过重复采用单位电阻和电容图形来实现。

暂无评论