之前聊了下影响信号完整性(SI)的两个因素,即反射和串扰,接下来我们将聊聊过冲下冲、振铃、信号延迟等,希望对小伙伴们有所帮助,若是想看上篇可点击右侧链接《一文教你看懂信号完整性(SI)(上)》。

3、过冲(Overshoot)与下冲(Undershoot)

过冲是由于电路切换速度过快及反射引起的信号跳变,也就是信号第一个峰值超过了峰值或谷值的设定电压。下冲是指下一个谷值或峰值,过分的过冲能够引起保护二极管工作,导致过早地失效,严重的还会损坏器件,过分的下冲能够引起假的时钟或数据错误,它们可通过增加适当端接予以减少或消除。

4、振铃(Ringring)

振荡的现象是反复出现过冲和下冲。信号的振铃由传输线上过度的电感和电容引起的接收端与传输线和源端的阻抗不匹配而产生的,通常发生在逻辑电平门限附近,多次跨越逻辑电平门限会导致逻辑功能紊乱。振铃由反射等多种因素引起的,振铃可以通过适当的端接或是改变PCB参数予以减小,但是不可能完全消除。

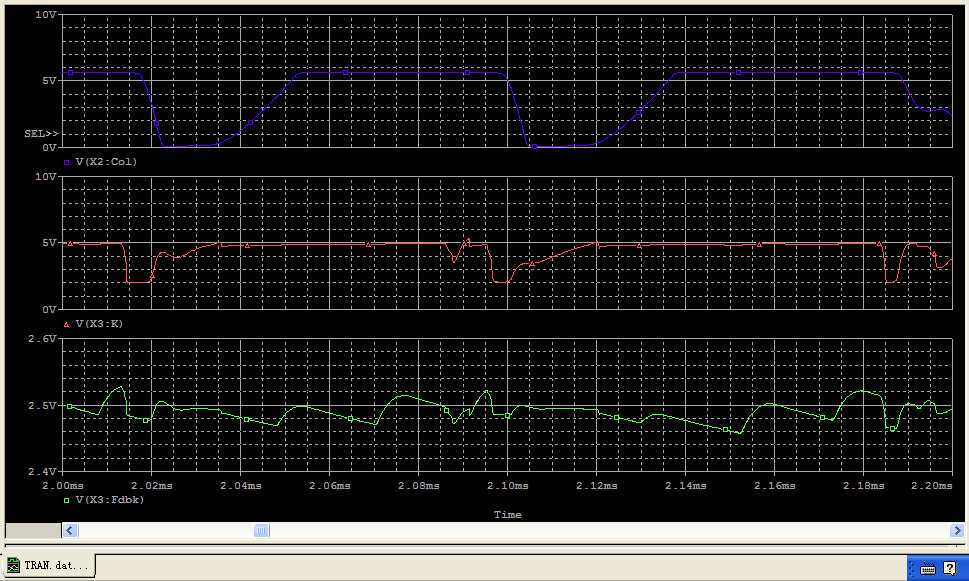

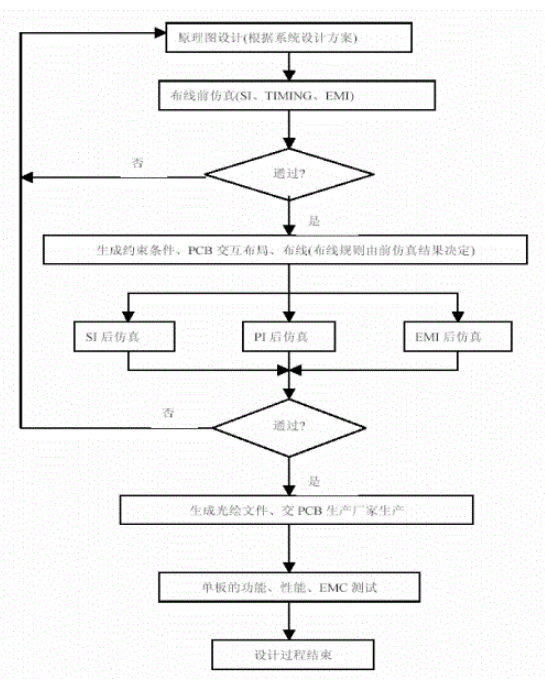

在Cadence的信号仿真软件中,将以上的信号完整性问题都放在反射参数中去度量。在接收和驱动器件的IBIS模型库中,我们只需要设置不同的传输线阻抗参数、电阻值、信号传输速率以及选择微带线还是带状线,就可以通过仿真工具直接计算出信号的波形以及相应的数据,这样就可以找出匹配的传输线阻抗值、电阻值、信号传输速率,在对应的PCB软件Allegro中,就可以根据相对应的传输线阻抗值和信号传输速率得到各层中相对应信号线的宽度(需提前设好叠层的顺序和各参数)。选择电阻匹配的方式也有多种,包括源端端接和并行端接等,根据不同的电路选择不同的方式。在布线策略上也可以选择不同的方式:菊花型、星型、自定义型,每种方式都有其优缺点,可以根据不同的电路仿真结果来确定具体的选择方式。

5、信号延迟(Delay)

电路中只能按照规定的时序接收数据,过长的信号延迟可能导致时序和功能的混乱,在低速的系统中不会有问题,但是信号边缘速率加快,时钟速率提高,信号在器件之间的传输时间以及同步时间就会缩短。驱动过载、走线过长都会引起延时。必须在越来越短的时间预算中要满足所有门延时,包括建立时间,保持时间,线延迟和偏斜。由于传输线上的等效电容和电感都会对信号的数字切换产生延迟,加上反射引起的振荡回绕,使得数据信号不能满足接收端器件正确接收所需要的时间,从而导致接收错误。在Cadence的信号仿真软件中,将信号的延迟也放在反射的子参数中度量,有Settledelay、Switchdelay、Propdelay。其中前两个与IBIS模型库中的测试负载有关,这两个参数可以通过驱动器件和接收器件的用户手册参数得到,可以将它们与仿真后的Settledelay、Switchdelay加以比较,如果在Slow模式下得到的Switchdelay都小于计算得到的值,并且在Fast的模式下得到的Switchdelay的值都大于计算得到的值,就可以得出我们真正需要的两个器件之间的时延范围Propdelay。在具体器件布放的时候,如果器件的位置不合适,在对应的时延表中那部分会显示红色,当把其位置调整合适后将会变成蓝色,表示信号在器件之间的延时已经满足Propdelay规定的范围了。

暂无评论