凡亿教育-可可

凡事用心,一起进步打开APP

公司名片工程师如何减小芯片的开关噪声问题?

随着数字电路工作频率越来越高,集成规模越来越大,电磁兼容性(EMC)问题也变得越来越尖锐突出,因此,电磁兼容设计已成为PCB设计中不可忽略的环节,那么如果遇到减小芯片的开关噪声类似的问题,工程师该如何解决?

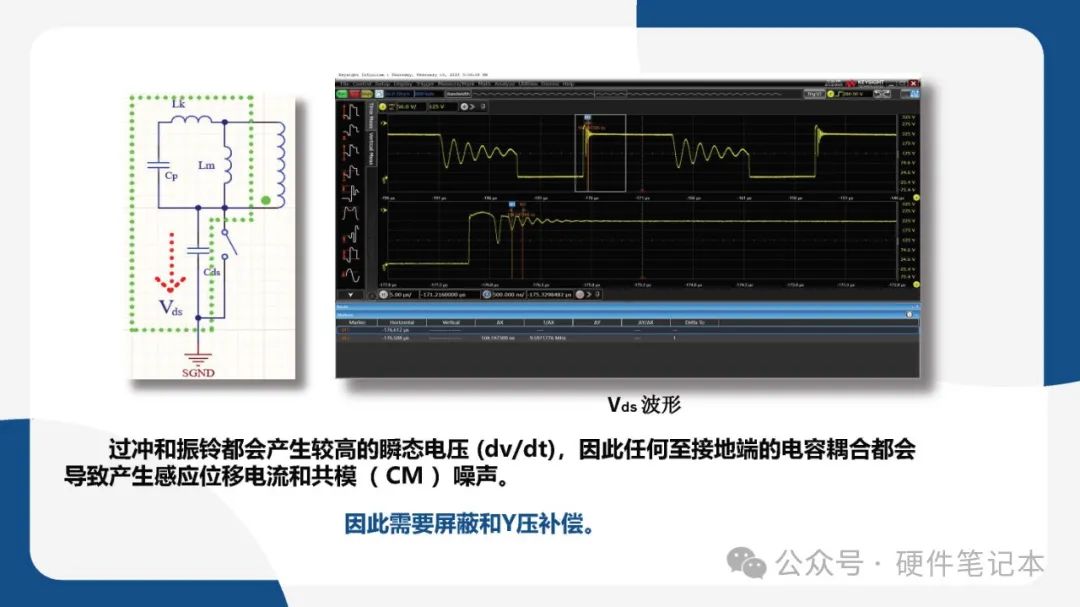

一般来说,引起芯片的开关噪声问题的直接原因是寄生电感,试验表明随着寄生电感的增加,开关噪声最大值也随之增大,因此工程师可采取一定措施减小寄生电感,即可解决芯片的开关噪声问题。

很多工程师是通过降低开关信号的变化速率及减小感应电压的方法来实现的,具体如下:

1、在工作速率要求允许的情况下尽量降低芯片内部逻辑器件开关速度,或者减少同时开关数目从而减小电流变化率。但需要注意点是:当电路本身要求的工作频率很高时该方法不适用。

2、为了减小电源系统的分布电感可使用电源/地平面结构,并尽量使电源平面和地平面接近。

3、通过增加电源/地平面引脚数及缩短电源/地直接阴角线长度等措施,降低电源板和地板之间的寄生电感,从而达到减小开关噪声的效果。

4、为了减小封装总电感增加封装中电源和地路径的互感可将电源和地引脚承兑放置并尽量靠近。

5、通过给高频交流信号提供低电感的旁路,而频率较低的信号仍然刘静系统电源回路,这样产生的噪声电压就会减小,具体做法是给电源增加旁路电容。

6、为了减小高频电流的回路电感,可增加去耦电容,这一做法能有效抑制芯片内部的开关噪声。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表凡亿课堂立场。文章及其配图仅供工程师学习之用,如有内容图片侵权或者其他问题,请联系本站作侵删。

相关阅读

进入分区查看更多精彩内容>

暂无评论