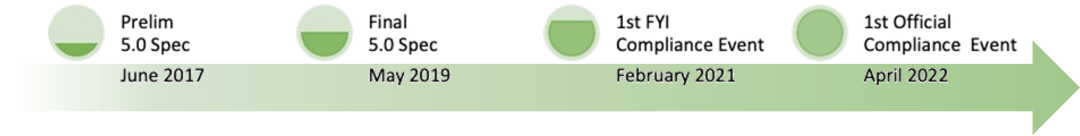

从规范草案到被 PCI-SIG 列入集成商的合规目录需要经历数年。初步 PCIe 5.0 规范于 2017 年 6 月公布,最终规范于 2019 年 5 月发布,第一次正式合规研讨会于 2022 年 4 月举行。如此漫长的过程说明了所开发的产品以及支持这些产品所需的生态系统非常复杂。

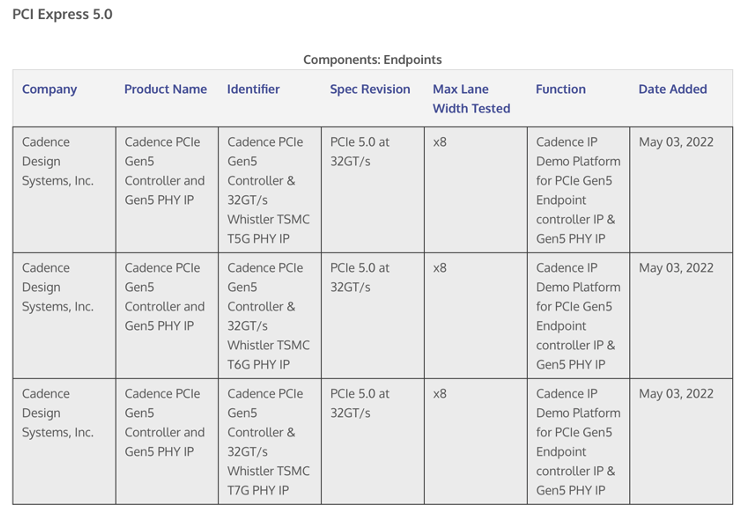

Cadence 一直是 PCI-SIG 的长期成员,也是 PCIe IP 的积极开发者。随着多个产品被列入集成商的合规目录,PCIe 5.0 也不例外。Cadence依托之前的技术专长,增强了子系统解决方案,以开发符合这些严格规范的 IP,同时也参与了合作性的合规计划。

PCI-SIG 合规计划:PCIe 5.0

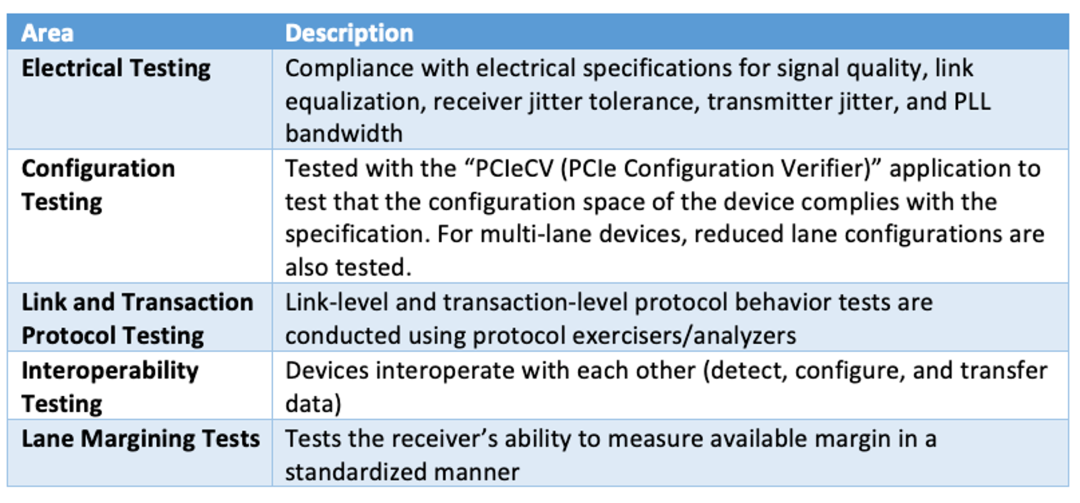

工作小组 Serial Enabling Workgroup (SEG) 负责执行 PCI-SIG 合规性计划。该合规性计划旨在确保经认证符合规范的设备可以实现互操作。该合规性计划包括一套电气和协议合规性测试(设备需要通过这些测试),还要在 PCI-SIG 组织的研讨会上指定测试程序。此外,在这些研讨会上,PCI-SIG 成员需要针对其他成员的产品测试自家设备的互操作性。

SEG 与各个成员公司和测试设备供应商合作,为每个版本的规范制定测试程序。该计划涵盖了规范的各个领域。

对于 PCIe 5.0,在 2022 年 4 月举行的正式合规性研讨会之前,PCI-SIG 在 2021 年以及之前的一年多时间里举办了多场“FYI(For Your Information,供参考)”研讨会。这些 FYI 研讨会不仅仅是一次预演,更是在完善测试程序以及确保设备和软件可靠运行方面发挥了重要作用。这些研讨会是保密的,使竞争者能够彼此合作并改进各自的产品和标准——这是一种真正的竞争性合作,有力地推动了行业的发展。

Cadence 的方法和成功经验

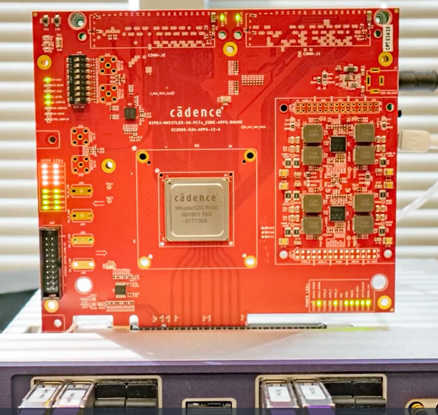

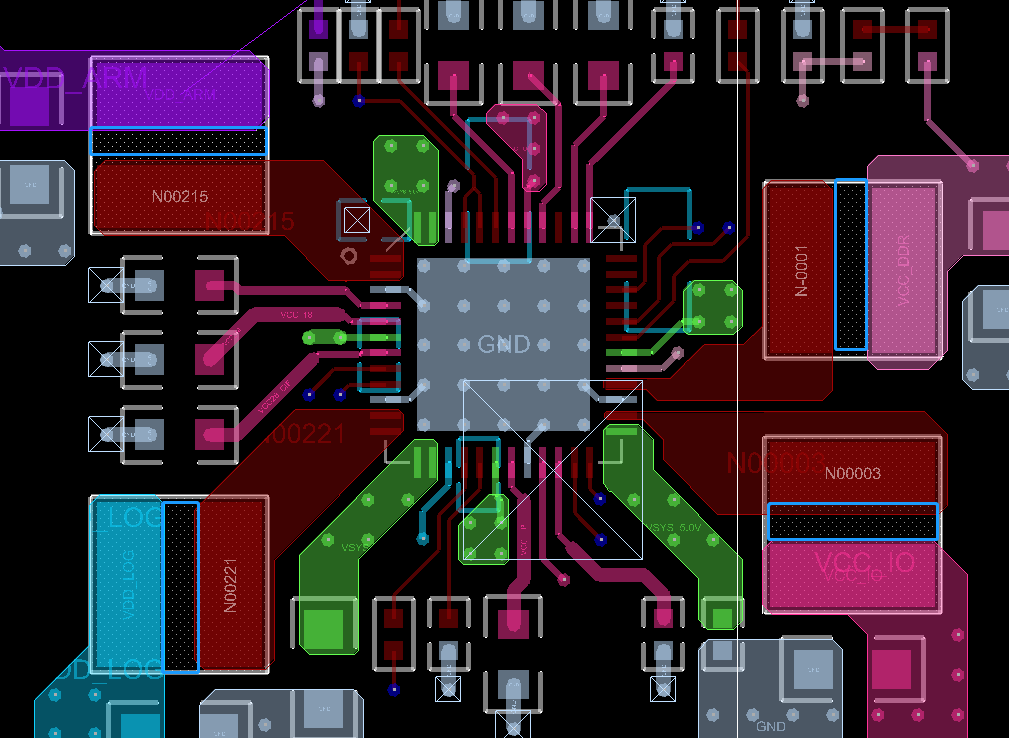

Cadence 依托之前在 3.0 和 4.0 版规范合规性方面取得的成功,对 PCIe 5.0 采取了独特的方法。通过在硅片中构建一个 IP 子系统,Cadence可以将整个协议栈作为一个 8 通道的解决方案进行测试,其中涵盖了许多客户实际使用的应用。

左图为 PCIe 5.0 子系统子卡

右图为 PCIe 5.0 子系统示意图

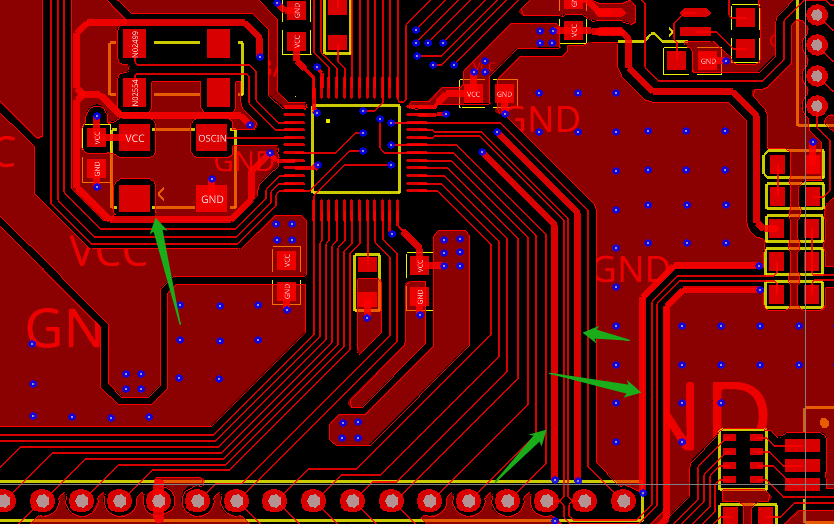

Cadence 的 PCIe 5.0 产品在整个 FYI 计划中表现良好,并在 2022 年 4 月举行的第一次研讨会上实现了合规。由于测试点有限,Cadence 在这次会议上对终端产品进行了多个工艺节点的认证。我们的根端口配置在7月 25-28 日举行的研讨会上经过了认证,并将很快被列入集成商的目录。

在 2022 年 4 月举行的合规性研讨会上,Cadence PCIe 5.0 接受测试

超越合规性:压力测试和互操作性

虽然合规性测试旨在检查产品是否符合互操作性的一系列必要要求,但在现实中,这些测试只是产品需要满足的最低要求。

在真实的系统中,我们会需要测试各种状况,包括链路错误、速度变化和电源状态变化。我们的实验室经过妥当配置,可针对这些条件进行压力测试,涵盖各种温度和工艺条件,在各种商用平台上进行数十万次测试。除了 8 通道扩展卡,我们还构建了 U.2 规格的扩展卡,可以将其轻松插入机架安装的系统中进行测试。通过在以上条件下的详尽测试,我们可以胸有成竹地向 Cadence IP 解决方案的采用者保证其应用将平稳运行。

目前,PCIe 6.0 规范也已于2022年初由 PCI-SIG 发布。PCIe 6.0 具有64GT/s 的原始数据速率,通过 x16 配置,最高可达 256GB/s,并利用业界现有的 PAM4 技术。如欲了解 PCIe 6.0 的详细内容,欢迎阅读文章《行业洞察 I PCIe 6.0 标准与 Cadence 的实施方法》。

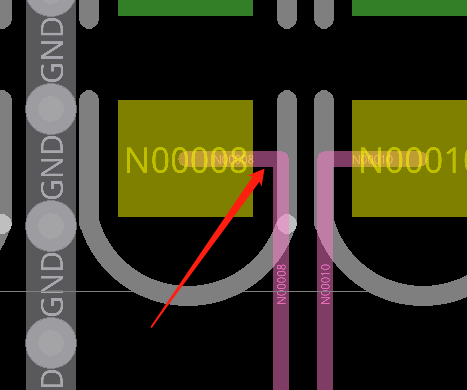

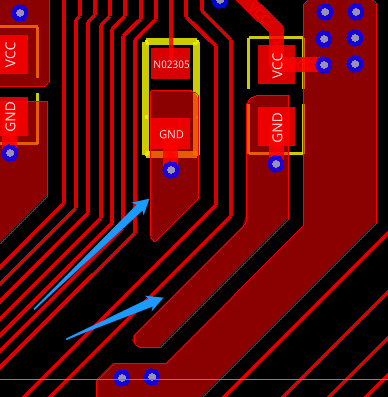

在设计 PCIe 6.0 时,信号完整性问题格外重要。因为PCIe 通道并不是隔离的,并且通道的走线与附近的所有导电结构都会产生电耦合。这就意味着数学模型、2D 仿真和近似值通常都太不准确,无法正确预测寄生值以满足 PCIe 6.0 代标准的要求。

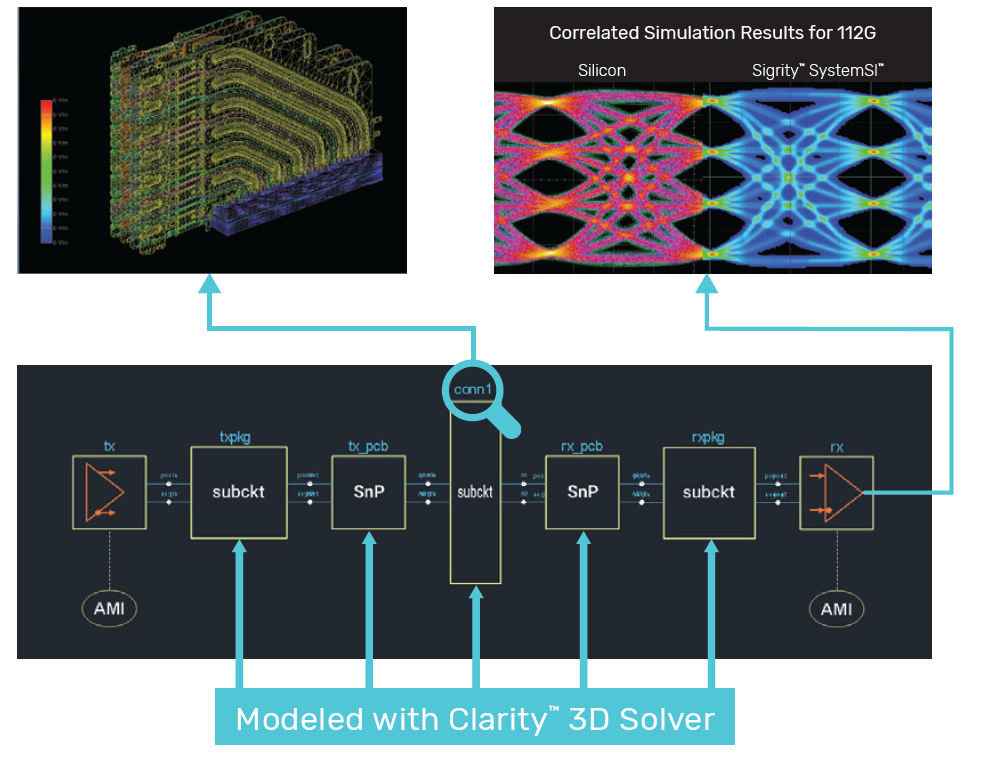

Cadence Clarity 3D Solver 使用了真正的整体的 3D 电磁场求解器,专门为适应大型 PCB 结构的仿真而构建。具有足够高的精度和速度来捕获小尺寸的 3D 电磁求解器甚至可以用于提供 IC 封装和 PCB 走线的电磁仿真。与将通过不同 IC 和 PCB 寄生提取方法得到的结果级联在一起相比,这种方法能够更加精确和完整地展现寄生行为和通道特性。

与近似值和简化模型相比,拥有足够容量的精确 3D 仿真工具可以生成与 PCIe 通道特性的实验数据更好匹配的模型。

同时,使用 Clarity 3D Solver 生成的模型与实验室的测量结果会更为接近,并且可以直接导入到行业标准电路仿真器(例如 Cadence Sigrity SystemSI)中,以实现实际测量和仿真之间极高的相关性。这对 PCIe 的合规性和互操作性测试尤具价值,可以帮助设计在电气测试(包括平台和内插卡发射器和接收器特性测试)中获得关键性优势,增强设计人员首次测试即可通过的信心。

如欲了解更多 Clarity 3D Solver 内容,欢迎点击文末阅读原文:

暂无评论