凡亿教育-可可

凡事用心,一起进步打开APP

公司名片FPGA管脚调整:高可靠性设计

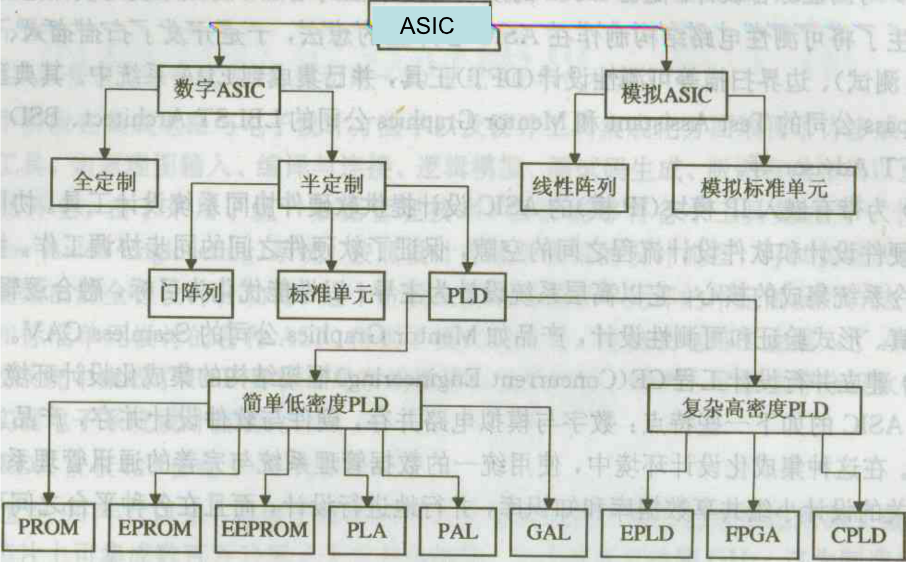

FPGA管脚调整是FPGA设计中的重要技术环节,主要涉及到FPGA芯片的输入输出管脚与外部硬件连接,确保信号传输的准确性和稳定性,工程师经常需要根据具体的应用需求来调整FPGA管脚配置,以此适配外部电路和信号接口,那么如何做?

1、管脚规划

在进行FPGA管脚调整之前,首先需要进行管脚规划。根据设计需求,确定哪些管脚需要用于输入、输出或双向信号传输,以及它们与外部器件的连接方式。

2、信号完整性考虑

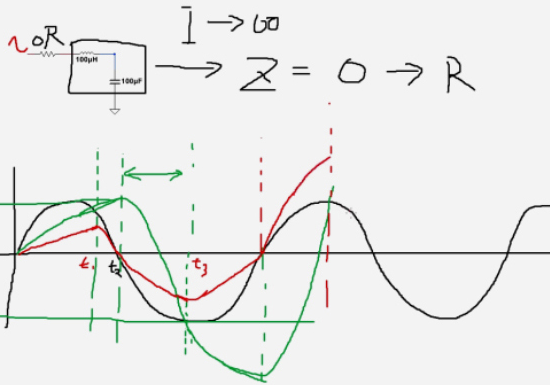

在管脚调整过程中,需要注意信号的完整性。高速信号或时钟信号的传输过程中可能会受到信号失真、串扰等问题的影响。因此,需要进行合理的布线和阻抗匹配,以确保信号传输的稳定性。

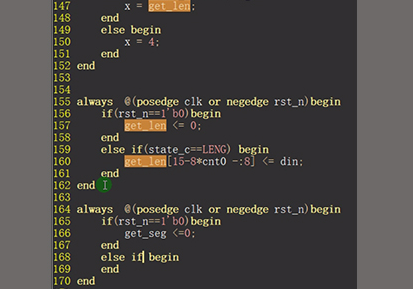

3、约束设置

在管脚调整过程中,需要注意信号的完整性。高速信号或时钟信号的传输过程中可能会受到信号失真、串扰等问题的影响。因此,需要进行合理的布线和阻抗匹配,以确保信号传输的稳定性。

4、差分信号处理

很多高速通信接口使用差分信号传输,这需要对FPGA管脚进行差分对调整。差分信号可以降低噪声和串扰,提高信号传输的可靠性。

5、管脚映射

管脚调整后,需要将FPGA管脚映射到具体的物理引脚上。在映射过程中,需要考虑电路板布局和信号走线,以确保FPGA芯片与外部硬件连接正确。

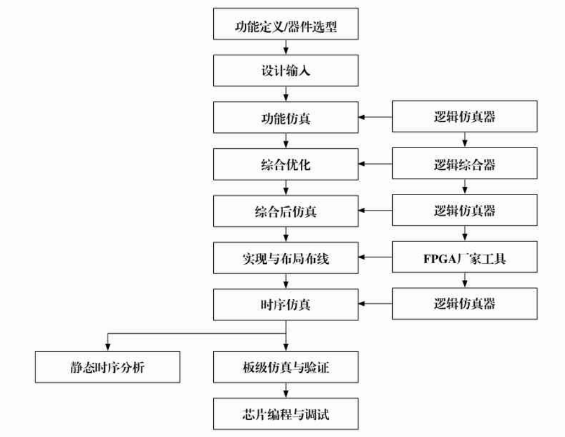

6、仿真验证

在完成FPGA管脚调整后,需要进行仿真验证,确保FPGA设计满足时序和功能要求。通过仿真可以检查信号完整性、时序约束是否满足,以及是否存在潜在的问题。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表凡亿课堂立场。文章及其配图仅供工程师学习之用,如有内容图片侵权或者其他问题,请联系本站作侵删。

相关阅读

进入分区查看更多精彩内容>

暂无评论