回答网友的问题:逻辑电路设计规则里gate width方向的尺寸一般要求远比feature size大,比如28nm的gate width最小也是100nm,间隔也最小80nm,这是出于什么考虑呢?有没有可能跟DRAM工艺那样,也压到feature附近的尺寸呢?

逻辑电路设计中,Gate width (指的是晶体管沟道的宽度)相比feature size (指的是制程节点,例如28nm)较大的原因涉及几个方面:

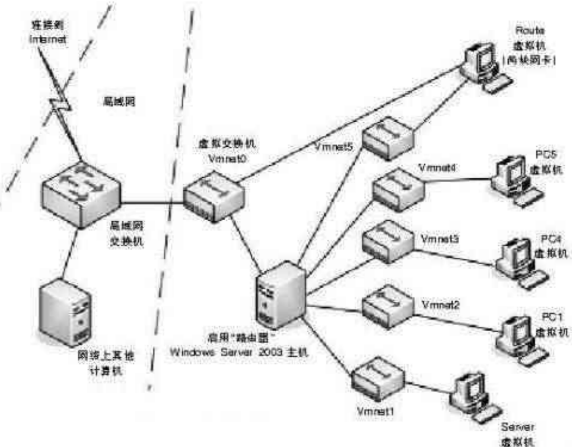

1. 工艺设计规则(Design Rule Checking,DRC): 电路设计必须遵循特定制程的工艺设计规则。这些规则由芯片制造商根据其工艺能力和可靠性数据定义。设计规则确保了电路元件之间有足够的间隔,以避免电气故障,并确保生产过程中的可重复性和高良品率。

2. 电气性能:更大的Gate width可以提供更高的驱动电流能力,对于负载电容较大的线路来说,它可以提高信号传输速度,以及改善电路的开关速度。

3. 可靠性:较大的设计尺寸可以提高设备在多种工艺条件下的健壮性和可靠性,降低由于工艺变化造成的性能分散,如阈值电压(Vt)变化和漏电流。

4. 热管理:随着逻辑电路的微缩,热密度会上升。如果没有充足的间隔和尺寸大小来分散热量,可能会导致过热问题。

5. 构造复杂度:逻辑电路设计往往要考虑到晶体管之间以及晶体管和其他部分(如铜线层)的互连与布局。在有限空间内容纳大量的晶体管和互连,确定合适的尺寸非常关键。

至于将gate width压缩到feature size附近,如同在动态随机存取存储器(DRAM)中的做法,存在下列挑战:

工艺挑战:制造逻辑电路时,晶体管的门控结构、源漏区与沟道之间的工艺复杂度远高于存储器单元。制造密度更高的逻辑电路,要求制造工艺能够在极小特征尺寸下保持电路的完整性和性能。

设计挑战:晶体管的门尺寸是影响器件性能的核心参数,与DRAM相比,逻辑电路的性能要求更严格,包括速度、功耗和噪声容忍度等指标。

成本考虑:逼近物理极限会增加设计和制造的复杂度和成本。压缩设计尺寸可能要求使用更先进的光刻技术,比如极紫外光(EUV)光刻,这将显著增加成本。

漏电流和可靠性:随着gate width的减小,在一定程度上会增加短道效应,造成漏电流增加,从而影响器件的能效和可靠性。

尽管有诸多挑战,工艺技术仍在不断发展。例如,采用FinFET(鳍式场效应晶体管)和GAAFET(栅全包围晶体管)等3D晶体管技术可以在更小的feature size下构造逻辑电路。然而,即使如此,gate width仍受限于上述因素,不太可能像DRAM单元那样被压缩到feature size附近。

声明:本文转载自老虎说芯 公众号,如涉及作品内容、版权和其它问题,请于联系工作人员,我们将在第一时间和您对接删除处理!

暂无评论